EDA软件的导线合并计算方法、装置、设备及介质与流程

本发明涉及eda软件,尤其涉及一种eda软件的导线合并计算方法、装置、设备及介质。

背景技术:

1、eda软件在布局或者设计阶段,在用户的设计修改过程中,或者导入第三方设计工具的设计数据等一些场景下会出现大量逻辑上连通的布线通路,被分割成多个导线的情况。

2、例如,在altium designer(电子产品开发系统)生成的pcb布局图中显示了电路板上各个元件的物理布局、导线的路径、布线层次和连接关系,目前的开发工具,通常是基于离散的导线数据进行导线排布计算,换而言之,需合并的多个导线会被逐一进行计算,导致计算量较大,计算效率较低。

3、因此,有必要提出一种eda软件的导线合并计算方法、装置、设备及介质以解决上述问题。

技术实现思路

1、本发明的目的在于提供一种eda软件的导线合并计算方法、装置、设备及介质,用以改善现有开发工具基于离散的导线数据进行导线排布计算,计算量较大,计算效率较低的问题。

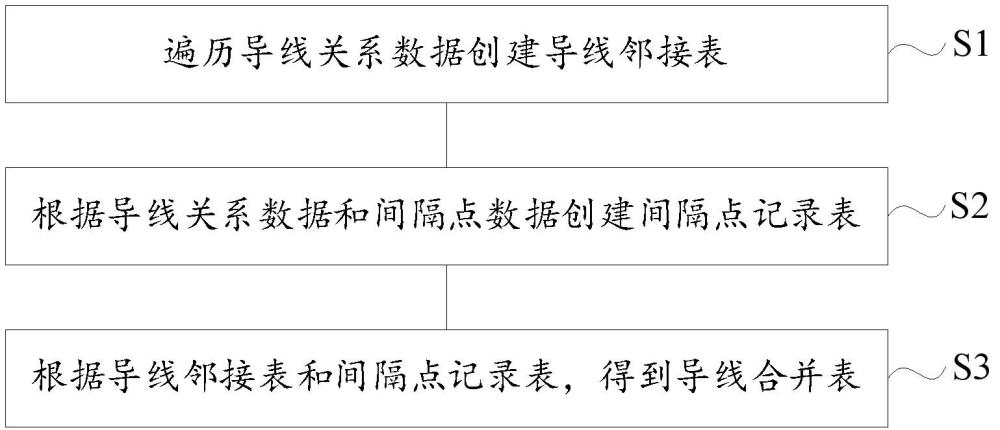

2、第一方面,本发明提供了一种eda软件的导线合并计算方法,该方法包括:

3、s1:遍历导线关系数据创建导线邻接表,其中,所述导线关系数据包括导线网络中各导线间连接关系,所述导线邻接表包括所述导线网络中节点与所述导线之间的对应关系;

4、s2:根据所述导线关系数据和间隔点数据创建间隔点记录表,其中,所述导线网络中节点包括间隔点和非间隔点,所述间隔点包括管脚、过孔、交叉点,所述非间隔点为两个所述导线非间断连接的节点;

5、s3:根据所述导线邻接表和所述间隔点记录表,得到导线合并表,其中,所述导线合并表包括m个待合并组,每个所述待合并组包括n个待合并导线,m、n分别为正整数。

6、在一种可能的实施例中,根据所述导线邻接表和所述间隔点记录表,得到导线合并表,包括:

7、s31:判断所述导线网络中导线数据是否遍历结束,若是,结束导线合并过程,若否,获取一当前待处理导线数据,执行步骤s32;

8、s32:判断所述当前待处理导线数据是否已处理,若是,返回执行步骤s31,若否,创建待合并组,将所述当前待处理导线数据写入堆栈中,执行步骤s33;

9、s33:判断所述堆栈中是否存在导线数据,若是,执行步骤s34,若否,执行步骤s35;

10、s34:从所述堆栈中移除栈顶的导线数据,将当前移除导线数据标记为已处理,并将所述当前移除导线数据加入当前待合并组中,判断所述当前移除导线数据是否端点为非间隔点且邻接的导线数据未处理,若是,将所述当前移除导线数据的非间隔点的邻接未处理导线数据写入所述堆栈中,返回执行步骤s33,若否,返回执行步骤s33;

11、s35:将所述当前待合并组中数据添加到导线合并表中,返回执行步骤s31。

12、在一种可能的实施例中,判断所述当前移除导线数据是否端点为非间隔点且邻接的导线数据未处理,若是,将所述当前移除导线数据的非间隔点的邻接未处理导线数据写入所述堆栈中,返回执行步骤s33,若否,返回执行步骤s33,包括:

13、s342:判断所述当前移除导线数据的始端节点是否为非间隔点,若是,执行步骤s343,若否,执行步骤s344;

14、s343:判断是否存在与所述始端节点邻接未处理的导线数据,若是,将与所述始端节点邻接未处理的导线数据写入所述堆栈中,执行步骤s344,若否,执行步骤s344;

15、s344:判断所述当前移除导线数据的终端节点是否为非间隔点,若是,执行步骤s345,若否,返回执行步骤s33;

16、s345:判断是否存在与所述终端节点邻接未处理的导线数据,若是,将与所述终端节点邻接未处理的导线数据写入所述堆栈中,返回执行步骤s33,若否,返回执行步骤s33。

17、在一种可能的实施例中,判断所述当前移除导线数据的始端节点是否为非间隔点,包括:

18、通过查询所述间隔点记录表判断所述当前移除导线数据的始端节点是否为非间隔点。

19、在一种可能的实施例中,在步骤s31之前,还包括:

20、s30:创建导线记录表,其中,所述导线记录表包括所述导线网络中各所述导线及对应的处理状态,初始时,所述导线均为未处理状态;

21、将当前移除导线数据标记为已处理,包括:

22、在所述导线记录表中将当前移除导线数据标记为已处理。

23、在一种可能的实施例中,判断是否存在与所述始端节点邻接未处理的导线数据,包括:

24、从所述导线邻接表中获取与所述始端节点邻接的导线数据,在所述导线记录表中查询与所述始端节点邻接的导线数据的处理状态,根据查询结果判断是否存在与所述始端节点邻接未处理的导线数据。

25、在一种可能的实施例中,判断是否存在与所述终端节点邻接未处理的导线数据,包括:

26、从所述导线邻接表中获取与所述终端节点邻接的导线数据,在所述导线记录表中查询与所述终端节点邻接的导线数据的处理状态,根据查询结果判断是否存在与所述终端节点邻接未处理的导线数据。

27、第二方面,本发明实施例中还提供了一种eda软件的导线合并计算装置,该装置包括执行上述第一方面的任意一种可能的设计的方法的模块/单元。这些模块/单元可以通过硬件实现,也可以通过硬件执行相应的软件实现。

28、第三方面,本发明实施例中还提供了一种电子设备,包括处理器和存储器。其中,存储器用于存储一个或多个计算机程序;当存储器存储的一个或多个计算机程序被处理器执行时,使得该电子设备能够实现上述第一方面的任意一种可能的设计的方法。

29、第四方面,本发明实施例中还提供了一种计算机可读存储介质,计算机可读存储介质包括计算机程序,当计算机程序在电子设备上运行时,使得电子设备执行上述第一方面的任意一种可能的设计的方法。

30、第五方面,本发明实施例中还提供了一种包含计算机程序产品,当所述计算机程序产品在电子设备上运行时,使得所述电子设备执行上述任一方面的任意一种可能的设计的方法。

31、本发明的有益效果在于:通过创建导线邻接表和间隔点记录表,利用导线邻接表和间隔点记录表,对导线和节点进行计算判断,实现了自动化地对导线数据进行合并,开发工具在后续进行导线排布计算时,可以基于该导线合并表中导线合并数据进行计算,即需合并的多个导线会作为一根导线计算,无需逐一单独计算,大大减小了计算量,提高了计算效率。

技术特征:

1.一种eda软件的导线合并计算方法,其特征在于,所述方法包括:

2.根据权利要求1所述的eda软件的导线合并计算方法,其特征在于,根据所述导线邻接表和所述间隔点记录表,得到导线合并表,包括:

3.根据权利要求2所述的eda软件的导线合并计算方法,其特征在于,判断所述当前移除导线数据是否端点为非间隔点且邻接的导线数据未处理,若是,将所述当前移除导线数据的非间隔点的邻接未处理导线数据写入所述堆栈中,返回执行步骤s33,若否,返回执行步骤s33,包括:

4.根据权利要求3所述的eda软件的导线合并计算方法,其特征在于,判断所述当前移除导线数据的始端节点是否为非间隔点,包括:

5.根据权利要求3所述的eda软件的导线合并计算方法,其特征在于,在步骤s31之前,还包括:

6.根据权利要求5所述的eda软件的导线合并计算方法,其特征在于,判断是否存在与所述始端节点邻接未处理的导线数据,包括:

7.根据权利要求5所述的eda软件的导线合并计算方法,其特征在于,判断是否存在与所述终端节点邻接未处理的导线数据,包括:

8.一种eda软件的导线合并计算装置,其特征在于,所述装置包括:

9.一种电子设备,其特征在于,包括:处理器及存储器,所述存储器用于存储计算机程序;所述处理器用于执行所述存储器存储的计算机程序,以使所述电子设备执行权利要求1至7中任一项所述的方法。

10.一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现权利要求1至7中任一项所述的方法。

技术总结

本发明涉及电子设计技术领域,提供了一种EDA软件的导线合并计算方法、装置、设备及介质,包括:S1:遍历导线关系数据创建导线邻接表,其中,导线关系数据包括导线网络中各导线间连接关系,导线邻接表包括导线网络中节点与导线之间的对应关系;S2:根据导线关系数据和间隔点数据创建间隔点记录表,导线网络中节点包括间隔点和非间隔点,间隔点包括管脚、过孔、交叉点,非间隔点为两个导线非间断连接的节点;S3:根据导线邻接表和间隔点记录表得到导线合并表,导线合并表包括M个待合并组,每个待合并组包括N个待合并导线。本发明基于该导线合并表中导线合并数据进行计算,需合并的多个导线会作为一根导线计算,大大减小了计算量,提高计算效率。

技术研发人员:裴震,喻小香,樊宏斌,马俊毅,赵新锋,孟伟,李豪斌,龙朝阳

受保护的技术使用者:上海合见工业软件集团有限公司

技术研发日:

技术公布日:2024/4/24

- 还没有人留言评论。精彩留言会获得点赞!