一种基于Winograd算法的神经网络加速器系统

本发明涉及卷积神经网络,具体涉及一种基于winograd算法的神经网络加速器系统。

背景技术:

1、随着人工智能技术的不断发展,卷积神经网络已成为处理图像识别、语音处理和其他复杂数据分析任务的关键技术。卷积神经网络的核心优势在于其能够有效地提取和学习数据中的深层次特征。然而,这种能力伴随着显著的计算复杂度和存储需求。随着模型结构的日益深化和复杂化,如何在有限的硬件资源下有效地运行卷积神经网络模型成为了一个重要的研究领域。

2、卷积操作是计算密集型、存储密集型运算的典型代表,在整个卷积神经网络模型中卷积层的计算量占了85%以上,是提升整个系统性能的“瓶颈”所在。winograd算法作为一种高效的卷积计算优化方法受到了广泛关注。该算法通过将卷积运算转换为一系列较小的矩阵运算,显著减少了乘法操作的数量,从而提高了计算效率。这种优化特别适用于那些具有有限计算资源但需要高效处理卷积运算的设备,如智能手机、嵌入式系统和边缘计算节点。然而,要实现winograd算法在硬件上的高效运行,需要对数据流的管理和缓存结构进行精心设计,以确保数据在处理过程中的高速访问和有效存储。

3、此外,专用神经网络加速器虽然在性能方面表现优越,但通常缺乏足够的可移植性。相反,通用神经网络加速器虽然在灵活性方面占优,但在推理速度和效率上往往不足。

技术实现思路

1、针对现有技术中的上述不足,本发明提供了一种基于winograd算法的神经网络加速器系统,用以解决常见卷积神经网络和轻量级神经网络推理运算速度低的特点以及提高加速器的计算能力,从而实现硬件资源的经济高效利用,并对整个系统进行性能优化。

2、为了达到上述发明目的,本发明采用的技术方案为:

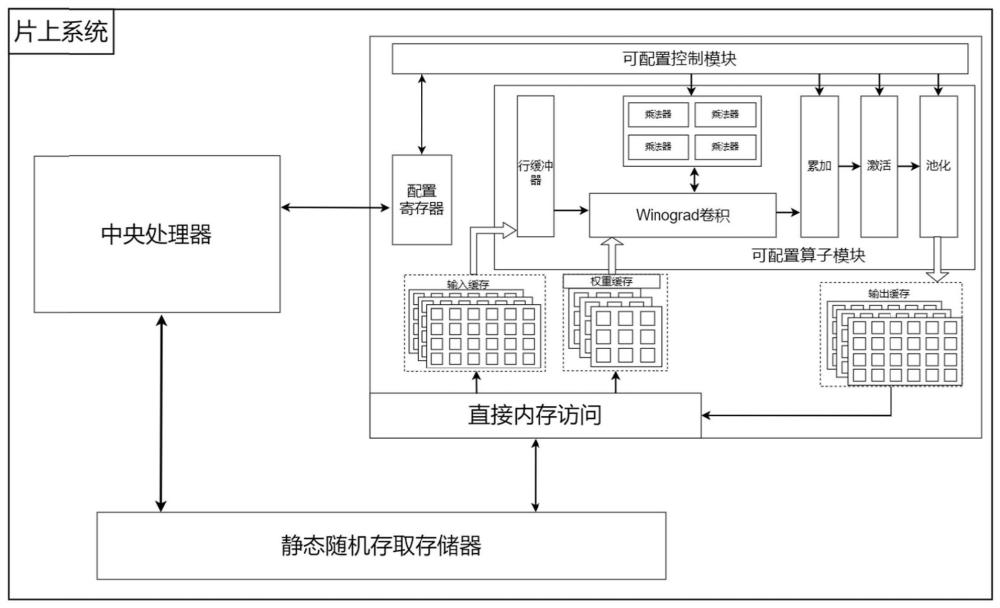

3、一种基于winograd算法的神经网络加速器系统,其特征在于,包括:

4、控制通路,用于利用中央处理器将卷积神经网络的控制信息传输给配置寄存器,配置寄存器根据接收的控制信息进行配置信息操作,同时将配置信息与控制信息传输给可配置控制模块,可配置控制模块根据接收的配置信息与控制信息控制数据流动与数据通路中算子的执行顺序;

5、数据通路,用于根据控制通路传输的卷积神经网络的控制信息,在可配置算子模块采用winograd算法对输入特征图与输入卷积核数据进行卷积加速计算,得到输入特征图与输入卷积核数据的卷积结果,并将卷积结果传输给缓存模块作为卷积神经网络中后续网络层的输入,实现对卷积神经网络的调度与运行。

6、进一步地,数据通路还包括静态随机存取存储器模块以及直接内存访问模块;

7、直接内存访问模块,用于传输卷积神经网络的输入特征图与输入卷积核数据到可配置算子模块中进行运算,得到网络层的中间结果,同时将网络层的中间结果传输给静态随机存取存储器模块;

8、静态随机存取存储器模块,用于存储整个卷积神经网络需要的输入特征图和输入卷积核数据以及网络层的中间结果。

9、进一步地,缓存模块包括输入缓存、权重缓存以及输出缓存;

10、输入缓存,用于存储直接内存访问模块传输的输入特征图;

11、权重缓存,用于存储直接内存访问模块传输的输入卷积核数据;

12、输出缓存,用于存储可配置算子模块将输入特征图与输入卷积核数据完成卷积、激活、池化运算后输出的特征图数据。

13、进一步地,可配置算子模块包括行缓冲器、winograd卷积模块、乘法器单元、累加模块、激活模块以及池化模块;

14、行缓冲器,用于暂存输入特征图中的多行数据,将串行输入的数据以并行窗口的形式输出,以供winograd卷积模块计算使用;

15、winograd卷积模块,根据权重缓存传输的输入卷积核数据,采用winograd算法进行输入特征图与输入卷积核数据的卷积加速计算,得到卷积神经网络中单层卷积层的域间转换结果,并将单层卷积层的域间转换结果传输给乘法器单元进行矩阵乘法运算,得到winograd域的卷积结果,将winograd域的卷积结果转换为空间域后,得到多个单层卷积层的中间结果,将多个单层卷积层的中间结果传输给累加模块;

16、乘法器单元,用于接收winograd卷积模块传输的单层卷积层的域间转换结果,并利用乘法器执行相应的矩阵乘法运算;

17、累加模块,用于利用累加器对winograd卷积模块传输的多个单层卷积层的中间结果进行并行累加,得到累加的最终卷积结果;

18、激活模块,用于对累加模块传输的累加的最终卷积结果进行非线性变换,并利用relu激活函数将所有负值置为零;

19、池化模块,用于执行池化操作,从输入特征图的局部区域中选取最大值作为输出,以对输入特征图进行下采样。

20、进一步地,神经网络加速器系统采用三级缓存结构,第一级缓存结构为可配置算子模块,第二级缓存结构为缓存模块与直接内存访问模块,第三级缓存结构为静态随机存取存储器模块。

21、进一步地,行缓冲器包括上层状态机与下层状态机;

22、上层状态机,用于控制数据流上下滑动;

23、下层状态机,用于控制数据流在水平方向上滑动。

24、进一步地,行缓冲器的输出后设置有两个4×4的卷积缓存窗口,用于临时存储输入特征图的部分数据,以在进行winograd算法的加速卷积计算时,获取所需的局部数据。

25、进一步地,数据通路采用四输入、四输出的并行数据通道结构,每一个数据通道包括行缓冲器、winograd卷积模块、乘法器单元、累加模块、激活模块以及池化模块。

26、进一步地,控制通路还用于响应自设计的自动化硬件配置生成工具生成的外部参数指令,并利用外部参数指令控制可配置控制模块的数据流动与算子的执行顺序。

27、本发明具有以下有益效果:

28、1.本发明所提出的一种基于winograd算法的神经网络加速器系统,采用winograd算法将空间域的卷积转换到数据通路中做逐元素矩阵乘法运算,以节省大量的乘法器资源;

29、2.利用winograd模块与乘法器单元实现卷积加速计算,并设计并行数据通路,有效提升了神经网络加速器的计算能力,实现了硬件资源的经济高效利用;

30、3.采用三级缓存结构,提高了神经网络加速器的计算能力,同时能够有效存储和传输数据,有效减轻了神经网络加速器系统对宽带的依赖,提高了数据访问效率,优化了系统性能。

31、4.利用外部参数指令作用于控制模块,提升了卷积神经网络加速器系统在不同应用场景下的可配置性和适应性,不仅使卷积神经网络加速器系统的配置过程变得迅速,而且减少了手动编码时可能出现的错误。

技术特征:

1.一种基于winograd算法的神经网络加速器系统,其特征在于,包括:

2.根据权利要求1所述的基于winograd算法的神经网络加速器系统,其特征在于,数据通路还包括静态随机存取存储器模块以及直接内存访问模块;

3.根据权利要求1所述的基于winograd算法的神经网络加速器系统,其特征在于,缓存模块包括输入缓存、权重缓存以及输出缓存;

4.根据权利要求1所述的基于winograd算法的神经网络加速器系统,其特征在于,可配置算子模块包括行缓冲器、winograd卷积模块、乘法器单元、累加模块、激活模块以及池化模块;

5.根据权利要求1或2所述的基于winograd算法的神经网络加速器系统,其特征在于,神经网络加速器系统采用三级缓存结构,第一级缓存结构为可配置算子模块,第二级缓存结构为缓存模块与直接内存访问模块,第三级缓存结构为静态随机存取存储器模块。

6.根据权利要求4所述的基于winograd算法的神经网络加速器系统,其特征在于,行缓冲器包括上层状态机与下层状态机;

7.根据权利要求6所述的基于winograd算法的神经网络加速器系统,其特征在于,行缓冲器的输出后设置有两个4×4的卷积缓存窗口,用于临时存储输入特征图的部分数据,以在进行winograd算法的加速卷积计算时,获取所需的局部数据。

8.根据权利要求4所述的基于winograd算法的神经网络加速器系统,其特征在于,数据通路采用四输入、四输出的并行数据通道结构,每一个数据通道包括行缓冲器、winograd卷积模块、乘法器单元、累加模块、激活模块以及池化模块。

9.根据权利要求1所述的基于winograd算法的神经网络加速器系统,其特征在于,控制通路还用于响应自设计的自动化硬件配置生成工具生成的外部参数指令,并利用外部参数指令控制可配置控制模块的数据流动与算子的执行顺序。

技术总结

本发明涉及卷积神经网络技术领域,公开了一种基于Winograd算法的神经网络加速器系统,包括:数据通路,用于根据控制通路传输的卷积神经网络的控制信息,在可配置算子模块采用Winograd算法对输入特征图与输入卷积核数据进行卷积加速计算,得到输入特征图与输入卷积核数据的卷积结果,并将卷积结果传输给缓存模块作为卷积神经网络中后续网络层的输入,实现对卷积神经网络的调度与运行;本发明采用Winograd算法将空间域的卷积转换到数据通路做逐元素矩阵乘法运算,节省了大量乘法器资源;利用Winograd模块与乘法器单元实现卷积加速,结合设计并行数据通路,有效提升神经网络加速器的计算能力;采用三级缓存结构,有效存储和传输数据,提高了数据访问效率,优化了系统性能。

技术研发人员:肖卓凌,唐亮,雷治宇,陈柏宇,郭志勇

受保护的技术使用者:电子科技大学

技术研发日:

技术公布日:2024/6/26

- 还没有人留言评论。精彩留言会获得点赞!