一种标准单元电路晶体管的布局方法

本发明涉及晶体管布局,具体涉及一种标准单元电路晶体管的布局方法。

背景技术:

1、在数字电路的标准单元库开发中,晶体管布局的优化是至关重要的一环。传统标准单元的晶体管布局主要依赖人工计算和绘制图纸,但是这种方式不仅在布局时间方面存在较大缺陷,而且布局方案容易出现不符合约束条件的情况。此外,员工在布局过程中需要消耗大量脑力和注意力,过于依赖老员工的经验也会对企业的业务开展产生一定的制约。

2、然而,标准单元库在集成电路的设计中扮演着至关重要的角色,而传统的人工布局方法已经无法跟上标准单元库快速发展的脚步。以往的人工布局方法存在制约因素,如布局时间长、布局结果差、布局结果不符合约束等问题。

技术实现思路

1、本发明提供一种标准单元电路晶体管的布局方法,旨在解决现有的晶体管布局时间长、布局结果差、布局结果不符合约束等问题。

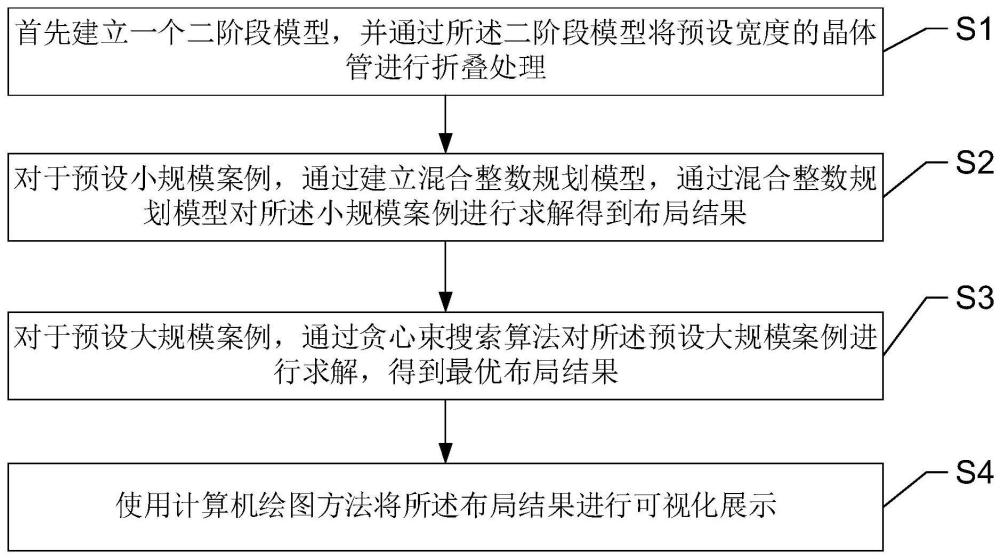

2、本发明实施例提供一种标准单元电路晶体管的布局方法,所述布局方法包括以下步骤:

3、s1、首先建立一个二阶段模型,并通过所述二阶段模型将预设宽度的晶体管进行折叠处理;

4、s2、对于预设小规模案例,通过建立混合整数规划模型,通过混合整数规划模型对所述小规模案例进行求解得到布局结果;

5、s3、对于预设大规模案例,通过贪心束搜索算法对所述预设大规模案例进行求解,得到最优布局结果;

6、s4、使用计算机绘图方法将所述布局结果进行可视化展示。

7、优选的,所述步骤s1,所述二阶段模型的建立具体包括以下步骤:

8、建立第一阶段模型:将宽度较大的晶体管折叠成多个小晶体管,每个小晶体管的宽度都在120-220nm之间,最小化折叠所得到的晶体管数量;

9、建立第二阶段模型:在所述第一阶段模型的晶体管数量不改变的情况下,重新分配子晶体管的宽度,让子晶体管的宽度尽可能相同,当子晶体管的最大宽度最小时,所述子晶体管之间的宽度尽可能相同,将最小化子晶体管的最大宽度作为优化目标。

10、优选的,所述步骤s1,所述折叠处理具体包括以下步骤:

11、当宽度≤220nm时,无需进行折叠处理;

12、当220nm≤宽度≤240nm,找不到合法的折叠方式,即无需进行折叠处理;

13、当240nm≤宽度≤440nm,将原来晶体管的宽度设置为并折叠出一个宽度为的新晶体管;其中,原晶体管的宽度表示为w,为向下取整;

14、当宽度≥440nm时,采用所述二阶段模型来对晶体管进行折叠。

15、优选的,所述步骤s2,建立所述混合整数规划模型具体包括以下子步骤:

16、s21、对每个晶体管进行晶体管编号,将所述晶体管编号存储预设的字典的键中;

17、s22、根据所述晶体管编号建立混合整数规划模型,根据混合整数规划模型获得最终晶体管布局。

18、优选的,所述步骤s21中,所述编号具体包括以下子步骤:

19、创建一个字典,定义所述字典的键为线网名称,值为编号;

20、遍历所有晶体管,分别判断所遍历晶体管源极、漏极、栅极所连接的线网名称是否已经被添加到所述字典中;如果不存在于所述字典中,将其添加到所述字典中;第一个被添加到所述字典的线网名称对应的编号为1,第二个被添加到所述字典的线网名称对应的编号为2,依次类推,直到所有线网名称都被存储到字典的键中,编号结束。

21、优选的,所述步骤s3具体包括以下子步骤:

22、s31、将pmos类型和nmos类型的两种晶体管进行配对;

23、s32、找出所有能覆盖全部晶体管的配对方案;

24、s33、使用贪心策略对所述配对方案进行布局;

25、s34、挑选出前十个得分最高的布局作为初始布局来进行束搜索优化;

26、s35、尝试对束搜索得到的布局进行后处理优化;

27、s36、得到最高的分数布局。

28、优选的,所述步骤s32具体包括以下子步骤:

29、s321、使用一个外部循环来遍历pmos晶体管集合里面的所有晶体管;

30、s322、在内部嵌套一个循环来遍历nmos晶体管集合的每个晶体管;

31、s323、判断所遍历到的所述pmos晶体管的栅极所连接线网和所述nmos晶体管的栅极所连接线网是否相同,如果相同,将所述pmos晶体管和所述nmos晶体管组合成一个晶体管对;

32、s324、将每个晶体管都单独封装成一个晶体管对,找到所有的配对方式。

33、优选的,所述步骤s33具体包括以下子步骤:

34、s331、将所述晶体管对按照匹配网计数降序排序;

35、s332、取出所述晶体管对的集合中的第一个配对,将其添加x设置为0;定义,布局中的第一个晶体管对,其横坐标x坐标为0;

36、s333、决定晶体管对集合中剩余晶体管对的所述添加x,先拿到布局中最后的那个晶体管对,所述最后的晶体管对定义为末尾对;

37、s334、从所述晶体管对的集合中选择可以和所述末尾对共用有源区的晶体管对,如果满足这个条件的晶体管对有多个,则选择和所述末尾对有最多共同线网的那个进行布局。

38、优选的,所述步骤s34具体包括以下子步骤:

39、s341、通过束搜索算法在树的每一层通过约束评价规则筛选出部分节点来进行下一步的搜索;

40、s342、通过设置好的评价规则和束宽,获得最优的结果。

41、与现有技术相比,本发明的有益效果在于,通过首先建立一个二阶段模型,并通过所述二阶段模型将预设宽度的晶体管进行折叠处理;对于预设小规模案例,通过建立混合整数规划模型,通过混合整数规划模型对所述小规模案例进行求解得到布局结果;对于预设大规模案例,通过贪心束搜索算法对所述预设大规模案例进行求解,得到最优布局结果;使用计算机绘图方法将所述布局结果进行可视化展示。该布局算法的优点在于它能够充分考虑各种约束条件,并在求解过程中自动进行布局规划。此外,与人工布局相比,算法具有较高的求解效率,且求解结果能够得到准确的保障。该方法无疑是数字电路标准单元库开发中一个非常有潜力的解决方案,能够在加快电路设计开发的速度和提高电路设计的质量方面发挥一定的作用。同时,其高效、准确、高质量的布局方案可替代传统的人工布局结果。该方法的应用前景广阔,有望在未来的集成电路设计领域发挥重要作用。

技术特征:

1.一种标准单元电路晶体管的布局方法,其特征在于,所述布局方法包括以下步骤:

2.如权利要求1所述的标准单元电路晶体管的布局方法,其特征在于,所述步骤s1,所述二阶段模型的建立具体包括以下步骤:

3.如权利要求2所述的标准单元电路晶体管的布局方法,其特征在于,所述步骤s1,所述折叠处理具体包括以下步骤:

4.如权利要求1所述的标准单元电路晶体管的布局方法,其特征在于,所述步骤s2,建立所述混合整数规划模型具体包括以下子步骤:

5.如权利要求4所述的标准单元电路晶体管的布局方法,其特征在于,所述步骤s21中,所述编号具体包括以下子步骤:

6.如权利要求1所述的标准单元电路晶体管的布局方法,其特征在于,所述步骤s3具体包括以下子步骤:

7.如权利要求6所述的标准单元电路晶体管的布局方法,其特征在于,所述步骤s32具体包括以下子步骤:

8.如权利要求7所述的标准单元电路晶体管的布局方法,其特征在于,所述步骤s33具体包括以下子步骤:

9.如权利要求6所述的标准单元电路晶体管的布局方法,其特征在于,所述步骤s34具体包括以下子步骤:

技术总结

本发明提供了一种标准单元电路晶体管的布局方法,布局方法包括以下步骤:S1、首先建立一个二阶段模型,并通过所述二阶段模型将预设宽度的晶体管进行折叠处理;S2、对于预设小规模案例,通过建立混合整数规划模型,通过混合整数规划模型对所述小规模案例进行求解得到布局结果;S3、对于预设大规模案例,通过贪心束搜索算法对所述预设大规模案例进行求解,得到最优布局结果;S4、使用计算机绘图方法将所述布局结果进行可视化展示。本发明的标准单元电路晶体管的布局方法能有效减少人工布局的繁琐操作,提高标准单元库开发的效率与准确性。

技术研发人员:王润钦,魏丽军,杨立信,林杰锐,刘强,舒文兰

受保护的技术使用者:广东工业大学

技术研发日:

技术公布日:2024/7/15

- 还没有人留言评论。精彩留言会获得点赞!