一种芯片验证系统的制作方法

本发明涉及芯片验证,特别是涉及一种芯片验证系统。

背景技术:

1、在芯片验证场景下,为了提高验证的鲁棒性,通常需要生成大量的输入激励对待测试设计(design under test,dut)进行测试,得到每个输入激励对应的输出结果,再将输出结果与输入激励对应的预期结果相比较,从而验证dut的功能。

2、然而,大量的输入激励也就意味着大量的输出结果以及大量的预期结果需要存储,会占据大量的存储空间,并且输出结果与预期结果的逐个比较也会消耗大量的时间,导致芯片验证的成本较高。

3、因此,如何降低芯片验证过程的存储成本和时间成本成为了亟待解决的问题。

技术实现思路

1、针对上述技术问题,本发明采用的技术方案为:

2、一种芯片验证系统,所述系统包括:待测试设计dut、目标数据压缩单元f、数据库、处理器和存储有计算机程序的存储器,其中,所述数据库包括输入激励集合b={b1,b2,…,bn,…,bn}、预期输出集合c={c1,c2,…,cn,…,cn}和c对应的第一压缩结果e1,其中,bn为第n个输入激励,n为[1,n]范围内的整数,n为b中输入激励的个数,cn为第n个输入激励对应的预期输出,当所述计算机程序被处理器执行时,实现以下步骤:

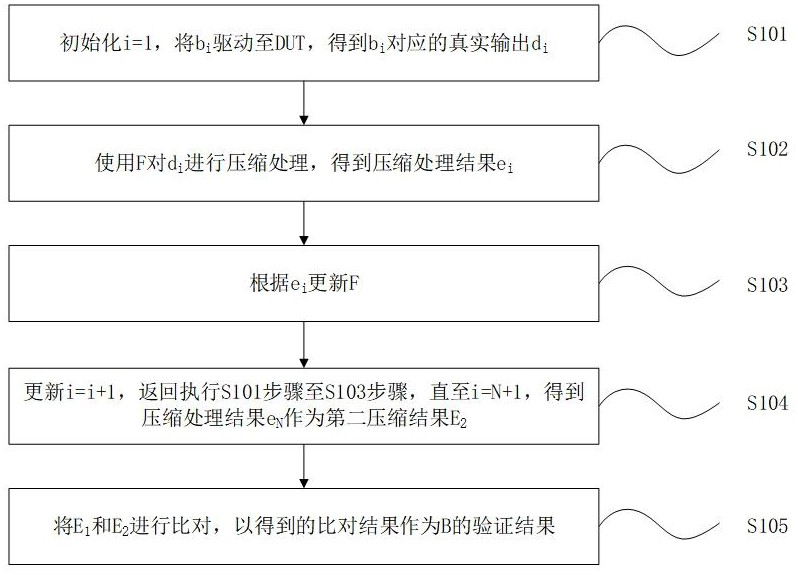

3、s101,初始化i=1,将bi驱动至dut,得到bi对应的真实输出di。

4、s102,使用f对di进行压缩处理,得到压缩处理结果ei。

5、s103,根据ei更新f。

6、s104,更新i=i+1,返回执行s101步骤至s103步骤,直至i=n+1,得到压缩处理结果en作为第二压缩结果e2。

7、s105,将e1和e2进行比对,以得到的比对结果作为b的验证结果。

8、本发明与现有技术相比具有明显的有益效果,借由上述技术方案,本发明提供的一种芯片验证系统可达到相当的技术进步性及实用性,并具有产业上的广泛利用价值,其至少具有以下有益效果:

9、本发明提供了一种芯片验证系统,所述系统包括:待测试设计dut、目标数据压缩单元f、数据库、处理器和存储有计算机程序的存储器,其中,所述数据库包括输入激励集合b={b1,b2,…,bn,…,bn}、预期输出集合c={c1,c2,…,cn,…,cn}和c对应的第一压缩结果e1,其中,bn为第n个输入激励,n为[1,n]范围内的整数,n为b中输入激励的个数,cn为第n个输入激励对应的预期输出,当所述计算机程序被处理器执行时,实现以下步骤:初始化i=1,将bi驱动至dut,得到bi对应的真实输出di,使用f对di进行压缩处理,得到压缩处理结果ei,根据ei更新f,更新i=i+1,返回执行s101步骤至s103步骤,直至i=n+1,得到压缩处理结果en作为第二压缩结果e2,将e1和e2进行比对,以得到的比对结果作为b的验证结果。

10、可知,通过数据压缩单元,将输入激励集合的真实输出和预期输出进行压缩,仅以若干个bit的位宽即可存储第一压缩结果和第二压缩结果,所占用的存储空间相较于直接存储真实输出和预期输出可以忽略不计,极大降低了芯片验证的存储成本,而且,可以通过第一压缩结果和第二压缩结果的比对结果作为验证结果,较低位宽的数据比对一次相较于真实输出和预期输出逐对比对,也极大降低了芯片验证的时间成本。

技术特征:

1.一种芯片验证系统,其特征在于,所述系统包括:待测试设计dut、目标数据压缩单元f、数据库、处理器和存储有计算机程序的存储器,其中,所述数据库包括输入激励集合b={b1,b2,…,bn,…,bn}、预期输出集合c={c1,c2,…,cn,…,cn}和c对应的第一压缩结果e1,其中,bn为第n个输入激励,n为[1,n]范围内的整数,n为b中输入激励的个数,cn为第n个输入激励对应的预期输出,当所述计算机程序被处理器执行时,实现以下步骤:

2.根据权利要求1所述的芯片验证系统,其特征在于,e1由f对c进行压缩处理得到。

3.根据权利要求1所述的芯片验证系统,其特征在于,当所述计算机程序被处理器执行时,还实现以下步骤:

4.根据权利要求1所述的芯片验证系统,其特征在于,所述系统还包括数据压缩单元集合a={a1,a2,…,am,…,am},其中,am为第m个数据压缩单元,m为[1,m]范围内的整数,m为a中数据压缩单元的个数,f∈a。

5.根据权利要求4所述的芯片验证系统,其特征在于,a中的m个数据压缩单元均采用循环冗余校验码进行数据压缩,不同数据压缩单元对应的循环冗余校验码位宽不同。

6.根据权利要求5所述的芯片验证系统,其特征在于,m设置为5,各个数据压缩单元分别对应的循环冗余校验码位宽为16bit、32bit、64bit、96bit、128bit。

7.根据权利要求5所述的芯片验证系统,其特征在于,单个预期输出对应的位宽为w,f为循环冗余校验码位宽与w对应的数据压缩单元。

8.根据权利要求7所述的芯片验证系统,其特征在于,w为128bit,相应地,f对应的循环冗余校验码位宽为128bit。

技术总结

本申请涉及芯片验证技术领域,特别是涉及一种芯片验证系统,系统包括:待测试设计DUT、目标数据压缩单元F、数据库、处理器和存储有计算机程序的存储器,当计算机程序被处理器执行时,实现以下步骤:将输入激励b<subgt;i</subgt;输入DUT,得到d<subgt;i</subgt;,使用F对d<subgt;i</subgt;压缩,得到压缩处理结果e<subgt;i</subgt;,根据e<subgt;i</subgt;更新F,重复执行前述步骤,得到压缩处理结果作为第二压缩结果E<subgt;2</subgt;,将存储的E<subgt;1</subgt;和E<subgt;2</subgt;比对,得到B的验证结果。可知,通过数据压缩单元,将真实输出和预期输出压缩,仅以较低位宽即可存储第一压缩结果和第二压缩结果,极大降低了芯片验证的存储成本,而且,仅需较低位宽数据一次比对即可得到验证结果,也降低了芯片验证的时间成本。

技术研发人员:张昀,王定

受保护的技术使用者:沐曦科技(北京)有限公司

技术研发日:

技术公布日:2024/5/12

- 还没有人留言评论。精彩留言会获得点赞!