芯片设计方法以及芯片设计系统与流程

本发明涉及一种集成电路领域,特别是一种芯片设计方法以及芯片设计系统。

背景技术:

1、在传统的芯片设计过程中,由于先进工艺下的电路布局的设计规模较大,例如在静态时序分析(static timing analysis,sta)的过程需要花费较多时间,因此对于芯片中的多个子模块的接口相关的时序问题需要在芯片设计过程中提前规避,以避免浪费设计时间。然而,目前的实现方式是透过手动修改以及编辑布局数据的方式来进行,因此具有设计效率不佳以及容易出现人为错误的问题。

技术实现思路

1、本发明是针对一种芯片设计方法以及芯片设计系统,可提供有效且便捷的晶片设计效果。

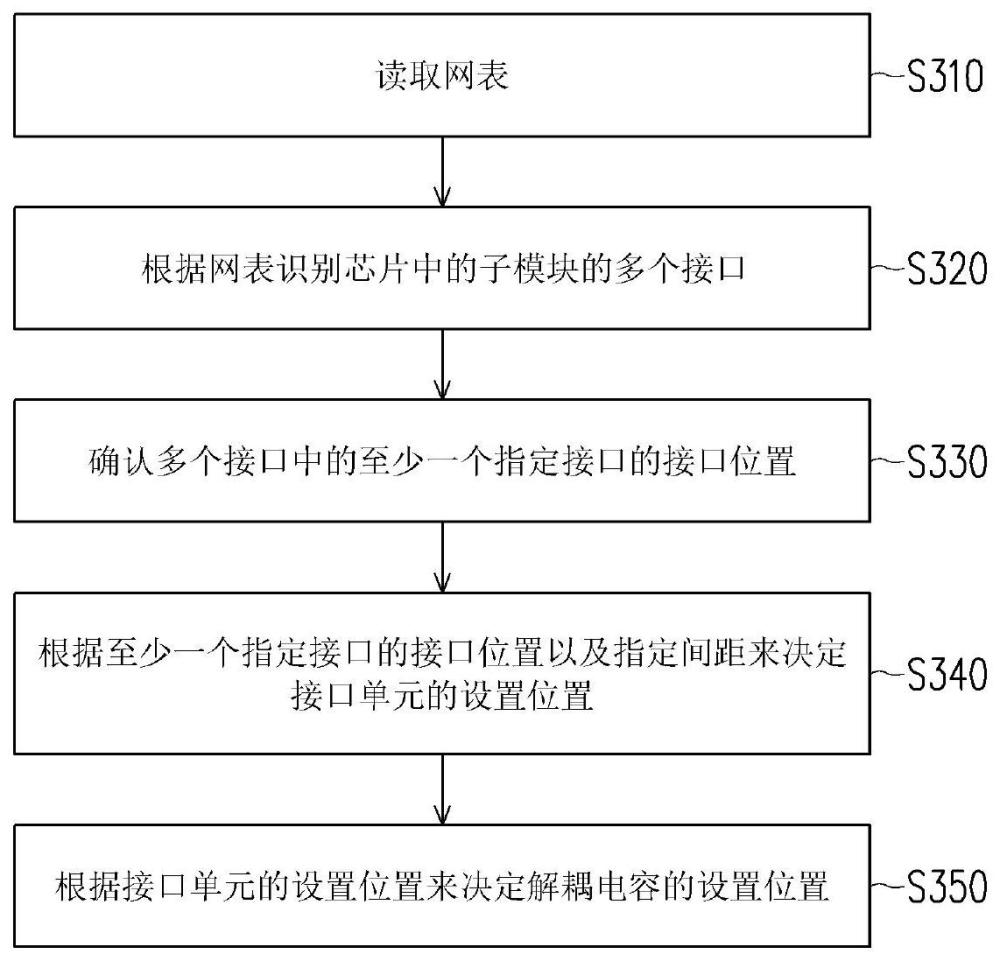

2、根据本发明的实施例,本发明的芯片设计方法包括:读取网表;根据网表识别芯片中的子模块的多个接口;确认多个接口中的至少一个指定接口的接口位置;根据至少一个指定接口的接口位置以及指定间距来决定接口单元的设置位置;以及根据接口单元的设置位置来决定解耦电容的设置位置。

3、在本发明的一实施例中,上述的多个接口包括输入接口、输出接口以及时钟接口。

4、在本发明的一实施例中,上述的至少一个指定接口为输入接口。

5、在本发明的一实施例中,上述的接口单元为缓冲器单元。

6、在本发明的一实施例中,上述的确认多个接口中的至少一个指定接口的接口位置的步骤包括:指定不需设置接口单元的接口名称。

7、在本发明的一实施例中,上述的接口位置与接口单元的设置位置之间的距离符合设计约束的最小物理距离要求。

8、在本发明的一实施例中,上述的在子模块中的第一方向上相邻的两个接口单元之间具有第一预设间隔距离。第一预设间隔距离等于一个接口单元高度。

9、在本发明的一实施例中,上述的子模块中的第二方向上相邻的两个接口单元之间具有第二预设间隔距离。第一方向垂直于第二方向。

10、在本发明的一实施例中,上述的子模块中对应于多个指定接口的多个接口单元与多个解耦电容之间为交错排列。

11、在本发明的一实施例中,上述的多个接口单元为相同的预设尺寸,及/或多个解耦电容为相同的预设尺寸。

12、在本发明的一实施例中,上述的多个接口单元的每一个的至少一侧边连接多个解耦电容的至少一个的至少一侧边。

13、根据本发明的实施例,本发明的芯片设计系统包括存储装置以及处理装置。存储装置用以存储网表。处理装置耦接存储装置,并且用以读取网表。处理装置根据网表识别芯片中的子模块的多个接口,并且处理装置确认多个接口中的至少一个指定接口的接口位置。处理装置根据至少一个指定接口的接口位置以及指定间距来决定接口单元的设置位置,并且处理装置根据接口单元的设置位置来决定解耦电容的设置位置。

14、基于上述,本发明的芯片设计方法以及芯片设计系统,可自动且有效地在芯片中设计接口单元以及解耦电容的设置位置。

15、通过参考以下的详细描述并同时结合附图可以理解本发明,需注意的是,为了使读者能容易了解及为了附图的简洁,本发明中的多张附图只绘出显示设备的一部分,且附图中的特定组件并非依照实际比例绘图。此外,图中各组件的数量及尺寸仅作为示意,并非用来限制本揭露的范围。

技术特征:

1.一种芯片设计方法,其特征在于,包括:

2.根据权利要求1所述的芯片设计方法,其特征在于,所述多个接口包括输入接口、输出接口以及时钟接口。

3.根据权利要求2所述的芯片设计方法,其特征在于,所述至少一个指定接口为所述输入接口。

4.根据权利要求1所述的芯片设计方法,其特征在于,所述接口单元为缓冲器单元。

5.根据权利要求1所述的芯片设计方法,其特征在于,确认所述多个接口中的所述至少一个指定接口的所述接口位置的步骤包括:

6.根据权利要求1所述的芯片设计方法,其特征在于,所述接口位置与所述接口单元的所述设置位置之间的距离符合设计约束的最小物理距离要求。

7.根据权利要求1所述的芯片设计方法,其特征在于,在所述子模块中的第一方向上相邻的两个接口单元之间具有第一预设间隔距离,并且所述第一预设间隔距离等于一个接口单元高度。

8.根据权利要求7所述的芯片设计方法,其特征在于,在所述子模块中的第二方向上相邻的两个接口单元之间具有第二预设间隔距离,其中所述第一方向垂直于所述第二方向。

9.根据权利要求1所述的芯片设计方法,其特征在于,在所述子模块中对应于多个指定接口的多个接口单元与多个解耦电容之间为交错排列。

10.根据权利要求9所述的芯片设计方法,其特征在于,所述多个接口单元为相同的预设尺寸,及/或所述多个解耦电容为相同的预设尺寸。

11.根据权利要求1所述的芯片设计方法,其特征在于,所述多个接口单元的每一个的至少一侧边连接所述多个解耦电容的至少一个的至少一侧边。

12.一种芯片设计系统,其特征在于,包括:

技术总结

本发明提供一种芯片设计方法以及芯片设计系统。芯片设计方法包括:读取网表;根据网表识别芯片中的子模块的多个接口;确认多个接口中的至少一个指定接口的接口位置;根据至少一个指定接口的接口位置以及指定间距来决定接口单元的设置位置;以及根据接口单元的设置位置来决定解耦电容的设置位置。本发明的芯片设计方法以及芯片设计系统可自动且有效地在芯片中设计接口单元以及解耦电容的设置位置。

技术研发人员:请求不公布姓名,请求不公布姓名,请求不公布姓名,请求不公布姓名,请求不公布姓名

受保护的技术使用者:上海壁仞科技股份有限公司

技术研发日:

技术公布日:2024/7/11

- 还没有人留言评论。精彩留言会获得点赞!