一种高速缓存验证方法、装置、设备、介质及程序产品与流程

本申请实施例涉及芯片验证,尤其涉及一种高速缓存验证方法、装置、设备、介质及程序产品。

背景技术:

1、在芯片设计过程中,需要对芯片设计进行验证,以确保芯片设计的正确性,才能保证后续生产出来的芯片符合设计目的和预期功能。对于集成有高速缓存(cache)的芯片设计来说,对其中的cache进行验证是芯片设计过程中的一个重要环节。

2、在对cache进行验证的过程中,通常需要对cache中的命中测试(hit-test)模块进行验证,相关技术中采用c模型(c model),只能将整个cache当作黑盒处理,无法模拟hit-test等关键模块的功能,不能从时序一致性的角度保证c model的输出结果与hit-test模块的输出结果一致,因此,无法实现一些关键模块的输出结果的精确比对,从而导致不能准确地验证cache的正确性。

技术实现思路

1、本申请实施例提供了一种高速缓存验证方法、装置、设备、介质及程序产品,用以提高对高速缓存中的命中测试模块的功能验证结果准确性。

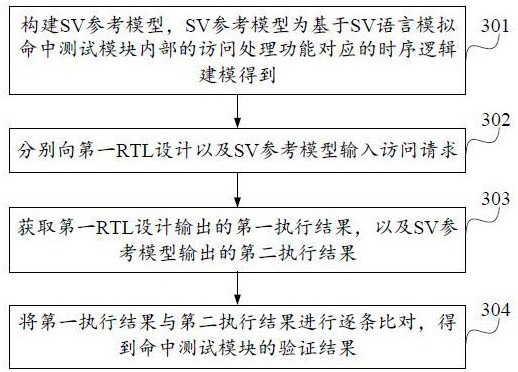

2、第一方面,本申请实施例提供了一种高速缓存验证方法,高速缓存包括命中测试模块,该方法包括:构建sv参考模型,sv参考模型为基于sv语言模拟命中测试模块内部的访问处理功能对应的时序逻辑建模得到;分别向第一硬件逻辑代码rtl设计以及sv参考模型输入访问请求,第一rtl设计为命中测试模块内部的访问处理功能对应的时序电路的rtl描述;获取第一rtl设计输出的第一执行结果,以及sv参考模型输出的第二执行结果;其中,第一执行结果为第一rtl设计对访问请求进行处理得到,第二执行结果为sv参考模型对访问请求进行处理得到;将第一执行结果与第二执行结果进行逐条比对,得到命中测试模块的验证结果。

3、通过上述方法, sv参考模型可以实现与第一rtl设计相同的访问处理功能,且sv参考模型实现的访问处理功能对应的时序逻辑与第一rtl设计实现的访问处理功能对应的时序逻辑一致,如此,在输入同样的访问请求一致的情况下,sv参考模型输出的第二执行结果与第一rtl设计输出第一执行结果也可以实现时序对齐,因此,通过sv参考模型输出的第二执行结果验证第一rtl设计输出第一执行结果,可以提高对高速缓存中的命中测试模块的功能验证结果准确性,从而有助于准确地验证高速缓存的正确性。

4、第二方面,本申请实施例提供了一种高速缓存的验证装置,所述高速缓存包括命中测试模块,所述验证装置包括:

5、构建单元,用于构建sv参考模型,所述sv参考模型为基于sv语言模拟所述命中测试模块内部的访问处理功能对应的时序逻辑建模得到;

6、输入单元,用于分别向第一硬件逻辑代码rtl设计以及所述sv参考模型输入访问请求,第一rtl设计为所述命中测试模块内部的访问处理功能对应的时序电路的rtl描述;

7、监测单元,用于获取所述第一rtl设计输出的第一执行结果,以及所述sv参考模型输出的第二执行结果,并将所述第一执行结果以及所述第二执行结果发送至验证单元;其中,第一执行结果为所述第一rtl设计对所述访问请求进行处理得到,第二执行结果为所述sv参考模型对所述访问请求进行处理得到;

8、验证单元,用于将所述第一执行结果与所述第二执行结果进行逐条比对,得到命中测试模块的验证结果。

9、第三方面,本申请实施例提供了一种电子设备,包括处理器和存储器;

10、所述存储器,用于存储程序指令及数据;

11、所述处理器用于调用所述存储器中的程序指令及数据执行前述任意一方面中或任意一方面中的任意可能的实现方式中提供的方法。

12、第四方面,本申请实施例提供了一种计算机可读存储介质,包括计算机可执行指令,所述计算机可执行指令用于在计算机上运行时,使得所述计算机执行前述任意一方面中或任意一方面中的任意可能的实现方式中提供的方法。

13、第五方面,本申请实施例提供了一种计算机程序产品,所述计算机程序产品存储有计算机程序,所述计算机程序包括程序指令,当所述程序指令被计算机执行时,使所述计算机执行前述任意一方面中或任意一方面中的任意可能的实现方式中提供的方法。

技术特征:

1.一种高速缓存验证方法,其特征在于,所述高速缓存包括命中测试模块,所述方法包括:

2.如权利要求1所述的方法,其特征在于,所述分别向第一rtl设计以及所述sv参考模型输入访问请求之前,还包括:

3.如权利要求1或2所述的方法,其特征在于,所述第二执行结果为所述sv参考模型对所述访问请求进行处理得到,包括:

4.如权利要求3所述的方法,其特征在于,所述至少一个访问处理操作包括以下至少一项:

5.如权利要求3所述的方法,其特征在于,所述第二执行结果还包括所述第一测试结果。

6.如权利要求3所述的方法,其特征在于,所述访问请求用于读取第一地址信息对应的数据,所述第一测试结果为命中结果,所述基于所述第一测试结果生成所述访问请求对应的至少一个访问处理操作,包括:

7.如权利要求3所述的方法,其特征在于,所述访问请求用于读取第一地址信息对应的数据,所述第一测试结果为未命中结果,所述基于所述第一测试结果生成所述访问请求对应的至少一个访问处理操作,包括:

8.如权利要求3所述的方法,其特征在于,所述访问请求用于向第二地址信息写入待写数据块;所述第一测试结果为命中结果,所述基于所述第一测试结果生成所述访问请求对应的至少一个访问处理操作,包括:

9.如权利要求3所述的方法,其特征在于,所述访问请求用于向第二地址信息写入待写数据块;所述第一测试结果为未命中结果,所述基于所述第一测试结果生成所述访问请求对应的至少一个访问处理操作,包括:

10.如权利要求1或2所述的方法,其特征在于,所述访问请求为冲刷请求;所述第二执行结果为所述sv参考模型对所述访问请求进行处理得到,包括:

11.一种高速缓存的验证装置,其特征在于,所述高速缓存包括命中测试模块,所述验证装置包括:

12.一种电子设备,其特征在于,包括处理器和存储器;

13.一种计算机可读存储介质,其特征在于,包括计算机可执行指令,当所述计算机可执行指令在计算机上运行时,使得所述计算机执行如权利要求1至10中任一项所述的方法。

14.一种计算机程序产品,其特征在于,所述计算机程序产品存储有计算机程序,所述计算机程序包括程序指令,当所述程序指令被计算机执行时,使所述计算机执行如权利要求1至10中任一项所述的方法。

技术总结

本申请实施例提供了一种高速缓存验证方法、装置、设备、介质及程序产品,用以提高对高速缓存中的命中测试模块的功能验证结果准确性。该方法包括:构建SV参考模型,分别向第一RTL设计以及SV参考模型输入访问请求,将第一RTL设计输出的第一执行结果与SV参考模型输出的第二执行结果逐条比对,得到命中测试模块的验证结果。由于SV参考模型实现命中测试模块内部的访问处理功能所对应的时序逻辑与第一RTL设计实现的访问处理功能所对应的时序逻辑一致,SV参考模型输出的第二执行结果与第一RTL设计输出第一执行结果可以实现时序对齐,从而可以提高对高速缓存中的命中测试模块的功能验证结果准确性。

技术研发人员:请求不公布姓名,请求不公布姓名

受保护的技术使用者:北京壁仞科技开发有限公司

技术研发日:

技术公布日:2024/5/16

- 还没有人留言评论。精彩留言会获得点赞!