一种互联缓冲装置、计算晶粒及电子设备的制作方法

本发明涉及数据传输领域,具体而言,涉及一种互联缓冲装置、计算晶粒及电子设备。

背景技术:

1、在半导体制造中,晶粒(又称为,die)指的是从一整块半导体晶圆切割下来的单个方形或矩形部分,是未封装的单个集成电路。多晶粒结构芯片是指将多个晶粒集成在单一的封装内,以实现更高的性能、更大的容量或更多的功能。通过将多个高性能晶粒集成在一起,可以显著提高处理速度和数据吞吐量。多晶粒结构允许不同功能的芯片组合,如将中央处理器(central processing unit,简称cpu)、图形处理器(graphics processing unit,简称gpu)以及ai加速器集成在同一封装中,为特定应用提供定制化解决方案。多晶粒结构可以更有效地利用晶圆,减少制造成本,同时也降低了设计复杂性和风险。

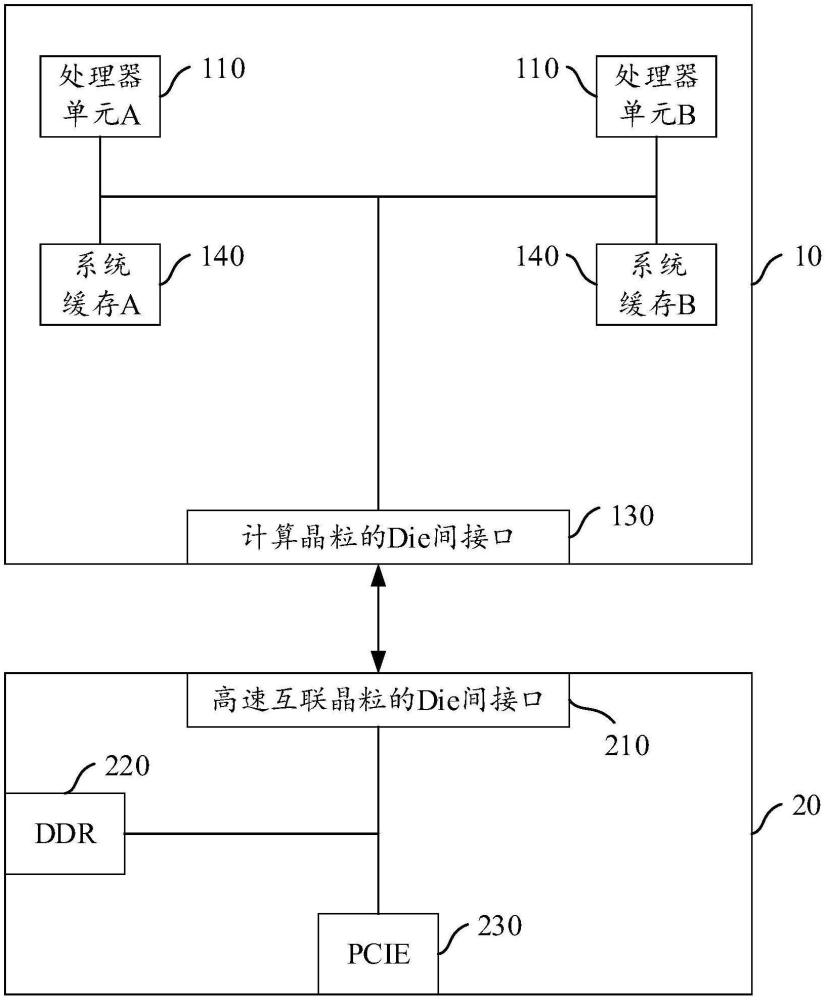

2、一种常见的多晶粒结构设计方法是将整个芯片设计分为计算晶粒(又称为,compute die)和高速互联晶粒(又称为,io die),将处理核心与输入/输出功能分开,各自封装在不同的晶粒中。

3、但受限于当前晶粒间互联技术的不成熟,以及晶粒间连接速度天生低于晶粒内部连接速度的限制,晶粒间通信的延迟显著增加。

技术实现思路

1、本发明的目的在于提供一种互联缓冲装置、计算晶粒及电子设备,以至少部分改善上述问题。

2、为了实现上述目的,本发明实施例采用的技术方案如下:

3、第一方面,本发明实施例提供一种互联缓冲装置,所述装置包括:标签模块、静态随机存储器、调度器以及缓冲区;

4、所述标签模块分别与所述静态随机存储器、所述调度器以及所述缓冲区连接;

5、所述标签模块还用于连接计算晶粒的die内接口;

6、所述调度器与所述缓冲区连接;

7、所述调度器还用于连接所述计算晶粒的die间接口,所述计算晶粒的die间接口用于连接高速互联晶粒的die间接口。

8、第二方面,本发明实施例提供一种计算晶粒,包括:至少一组处理器单元和上的互联缓冲装置,所述处理器单元通过计算晶粒的die内接口连接所述互联缓冲装置。

9、第三方面,本发明实施例提供一种电子设备,包括:上述的计算晶粒。

10、相对于现有技术,本发明实施例所提供的一种互联缓冲装置、计算晶粒及电子设备,包括:标签模块、静态随机存储器、调度器以及缓冲区;标签模块分别与静态随机存储器、调度器以及缓冲区连接;标签模块还用于连接计算晶粒的die内接口;调度器与缓冲区连接;调度器还用于连接计算晶粒的die间接口,计算晶粒的die间接口用于连接高速互联晶粒的die间接口。当标签模块接收到计算晶粒的die内接口的请求地址段与标签中的地址段匹配时,可以直接对静态随机存储器中对应的存储区间进行操作,不需要进行die间通信,从而减少晶粒间通信的延迟,提升通信速度。

11、为使本发明的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

技术特征:

1.一种互联缓冲装置,其特征在于,所述装置包括:标签模块、静态随机存储器、调度器以及缓冲区;

2.如权利要求1所述的互联缓冲装置,其特征在于,

3.如权利要求2所述的互联缓冲装置,其特征在于,

4.如权利要求1所述的互联缓冲装置,其特征在于,

5.如权利要求1所述的互联缓冲装置,其特征在于,所述互联缓冲装置还包括预取处理模块,所述预取处理模块分别与所述标签模块、所述静态随机存储器以及所述调度器连接,所述预取处理模块还用于连接所述计算晶粒的die内接口和所述计算晶粒的die间接口;

6.如权利要求5所述的互联缓冲装置,其特征在于,

7.如权利要求5所述的互联缓冲装置,其特征在于,

8.如权利要求7所述的互联缓冲装置,其特征在于,

9.一种计算晶粒,其特征在于,包括:至少一组处理器单元和权利要求1-8中任一项所述的互联缓冲装置,所述处理器单元通过计算晶粒的die内接口连接所述互联缓冲装置。

10.一种电子设备,其特征在于,包括:如权利要求9所述的计算晶粒。

技术总结

本发明提出一种互联缓冲装置、计算晶粒及电子设备,包括:标签模块、静态随机存储器、调度器以及缓冲区;标签模块分别与静态随机存储器、调度器以及缓冲区连接;标签模块还用于连接计算晶粒的Die内接口;调度器与缓冲区连接;调度器还用于连接计算晶粒的Die间接口,计算晶粒的Die间接口用于连接高速互联晶粒的Die间接口。当标签模块接收到计算晶粒的Die内接口的请求地址段与标签中的地址段匹配时,可以直接对静态随机存储器中对应的存储区间进行操作,不需要进行Die间通信,从而减少晶粒间通信的延迟,提升通信速度。

技术研发人员:汪磊,高梁,唐铭浩,王绍麟

受保护的技术使用者:广东鸿钧微电子科技有限公司

技术研发日:

技术公布日:2024/8/27

- 还没有人留言评论。精彩留言会获得点赞!