一种FPGA间双模互连网络结构的映射方法及系统

本发明涉及芯片的多fpga验证,具体涉及一种fpga间双模互连网络结构的映射方法及系统。

背景技术:

1、随着芯片设计规模越来越大,单片fpga因其资源限制,无法满足大规模芯片的原型验证需求。因此需要将多片fpga进行互连,搭建更大规模的原型验证系统。此时需要对大规模芯片设计进行划分,并将划分块分别映射到不同的fpga上,划分块之间的信号通过fpga之间的互连通道进行传输。

2、由于互连通道的数量远远小于划分块之间信号数量,一般采用时分复用(tdm)的方式,将多个信号在一个物理通道进行传输。传统方式采用lvds端口进行互连,lvds端口传输的最高速率为1.6gbps。而gt端口的传输带宽远远大于lvds端口,目前fpga上集成的gt端口传输速率最高可达28gbps。将系统中各fpga之间用lvds端口和gt端口进行互连,形成双模互连网络结构。因此针对该双模互连网络结构,如何实现双模互连网络的映射以充分发挥lvds端口和gt端口的传输性能,则仍然是一项亟待解决的关键技术问题。

技术实现思路

1、本发明要解决的技术问题:针对现有技术的上述问题,提供一种fpga间双模互连网络结构的映射方法及系统,本发明旨在实现双模互连网络的映射以充分发挥双模互连网络端口的传输性能,得到全局端口传输信号尽可能均衡,最终使得整体性能最高。

2、为了解决上述技术问题,本发明采用的技术方案为:

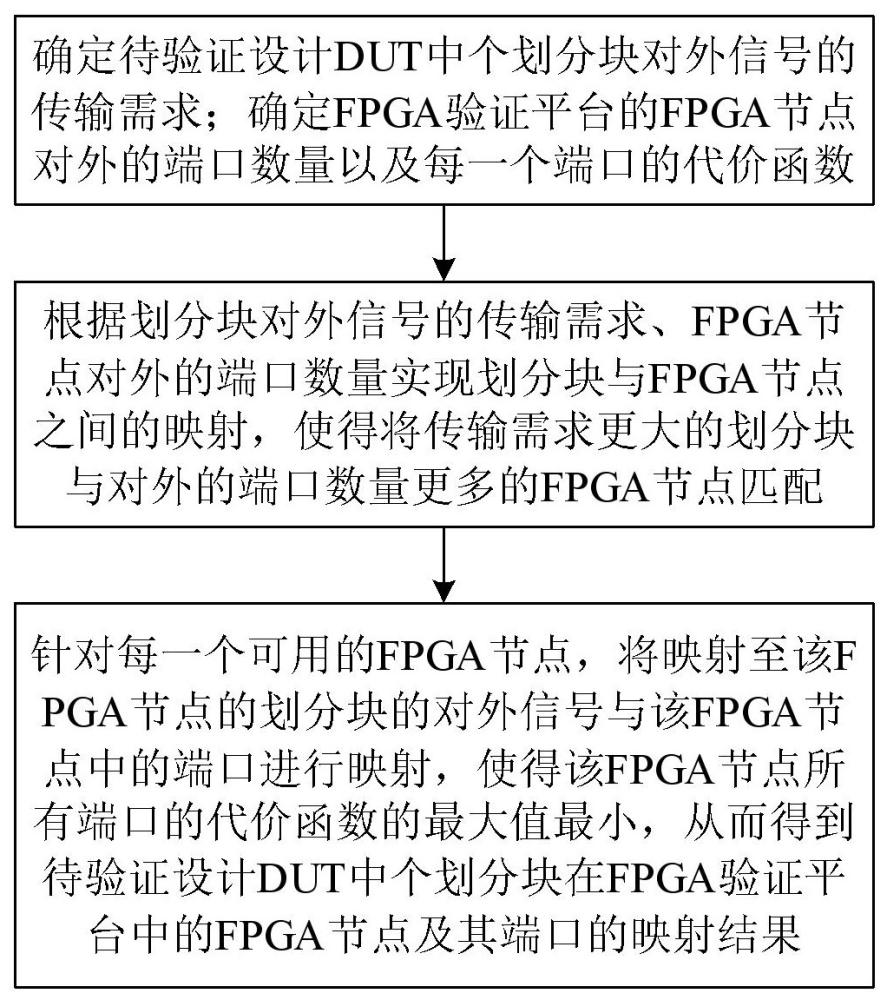

3、一种fpga间双模互连网络结构的映射方法,包括:

4、s101,确定待验证设计dut中个划分块对外信号的传输需求;确定fpga验证平台的fpga节点对外的端口数量以及每一个端口的代价函数;

5、s102,根据划分块对外信号的传输需求、fpga节点对外的端口数量实现划分块与fpga节点之间的映射,使得将传输需求更大的划分块与对外的端口数量更多的fpga节点匹配;

6、s103,针对每一个可用的fpga节点,将映射至该fpga节点的划分块的对外信号与该fpga节点中的端口进行映射,使得该fpga节点所有端口的代价函数的最大值最小,从而得到待验证设计dut中个划分块在fpga验证平台中的fpga节点及其端口的映射结果。

7、可选地,步骤s101中确定待验证设计dut中个划分块对外信号的传输需求包括:

8、s201,分别确定待验证设计dut中个划分块对外信号中任意第个划分块与第个划分块之间的传输需求;

9、s202,根据下式计算第个划分块对外信号的传输需求:

10、,

11、上式中,n为待验证设计dut中划分块的数量,为第个划分块与第个划分块之间的传输需求。

12、可选地,步骤s101中确定fpga验证平台的fpga节点对外的端口数量以及每一个端口的代价函数时,每一个端口的代价函数为该端口传输信号量的正相关函数,且双模互连网络结构中两种模式的端口的代价函数各不相同。

13、可选地,步骤s102包括:根据划分块对外信号的传输需求从大到小对划分块进行排序得到排序后的划分块列表,根据fpga节点对外的端口数量从大到小对fpga节点进行排序得到排序后的fpga节点列表,将排序后的划分块列表、fpga节点列表进行一一映射,从而使得将传输需求更大的划分块与对外的端口数量更多的fpga节点匹配。

14、可选地,步骤s103中使得该fpga节点所有端口的代价函数的最大值最小的目标函数的函数表达式为:

15、 ,

16、上式中,表示取最大值,表示该fpga节点上第个第一类端口的代价函数,,为该fpga节点上第一类端口的数量,表示该fpga上第个第二类端口的代价函数,,为该fpga节点上第二类端口的数量,表示最小的条件。

17、可选地,步骤s103中针对每一个可用的fpga节点的处理包括:

18、s301,检查映射到该fpga的划分块的对外信号中是否有已经由该对外信号的对端确定了映射端口,如果已经由对端确认了映射端口,则先将该对外信号与对端确认的映射端口进行映射,且端口的时分复用比为映射到该端口的信号位宽之和与端口可用差分对之比确定,跳转步骤s304;

19、s302,将剩余的对外信号按位宽由大到小进行排序得到排序后的对外信号队列;将可用的端口按端口的代价函数由小到大排序得到排序后的可用端口队列;

20、s303,将排序后的对外信号队列中位宽最大的信号,与排序后的可用端口队列中代价函数最小的端口进行映射,且端口的时分复用比为映射到该端口的信号位宽之和与端口可用差分对之比确定;

21、s304,检查该fpga的划分块的对外信号中是否还有对外信号未映射,如果有,则跳转步骤s302,否则跳转步骤s305;

22、s305,判定该可用的fpga节点处理完毕。

23、可选地,步骤s305中还包括在该fpga节点的所有端口中选择最大的代价函数作为该fpga节点的全局代价。

24、可选地,所述fpga间双模互连网络结构是指fpga间同时通过gt端口和lvds端口互联构成的fpga间双模互连网络结构。

25、此外,本发明还提供一种fpga间双模互连网络结构的映射系统,包括相互连接的微处理器和存储器,所述微处理器被编程或配置以执行所述fpga间双模互连网络结构的映射方法。

26、此外,本发明还提供一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,所述计算机程序用于被微处理器编程或配置以执行所述fpga间双模互连网络结构的映射方法。

27、和现有技术相比,本发明主要具有下述优点:本发明fpga间双模互连网络结构的映射方法针对双模互连网络平台提出了基于双模互连网络的映射,能够充分发挥lvds端口和gt端口的传输性能,得到全局端口传输信号尽可能均衡,最终使得整体性能最高。本发明关键在于映射过程考虑不同端口类型的代价,并作为统一衡量标准,用于对全系统整体性能的评估,从而能够得到全局端口传输信号尽可能均衡,最终使得整体性能最高。

技术特征:

1.一种fpga间双模互连网络结构的映射方法,其特征在于,包括:

2.根据权利要求1所述的fpga间双模互连网络结构的映射方法,其特征在于,步骤s101中确定待验证设计dut中个划分块对外信号的传输需求包括:

3.根据权利要求1所述的fpga间双模互连网络结构的映射方法,其特征在于,步骤s101中确定fpga验证平台的fpga节点对外的端口数量以及每一个端口的代价函数时,每一个端口的代价函数为该端口传输信号量的正相关函数,且双模互连网络结构中两种模式的端口的代价函数各不相同。

4.根据权利要求1所述的fpga间双模互连网络结构的映射方法,其特征在于,步骤s102包括:根据划分块对外信号的传输需求从大到小对划分块进行排序得到排序后的划分块列表,根据fpga节点对外的端口数量从大到小对fpga节点进行排序得到排序后的fpga节点列表,将排序后的划分块列表、fpga节点列表进行一一映射,从而使得将传输需求更大的划分块与对外的端口数量更多的fpga节点匹配。

5.根据权利要求1所述的fpga间双模互连网络结构的映射方法,其特征在于,步骤s103中使得该fpga节点所有端口的代价函数的最大值最小的目标函数的函数表达式为:

6.根据权利要求5所述的fpga间双模互连网络结构的映射方法,其特征在于,步骤s103中针对每一个可用的fpga节点的处理包括:

7.根据权利要求6所述的fpga间双模互连网络结构的映射方法,其特征在于,步骤s305中还包括在该fpga节点的所有端口中选择最大的代价函数作为该fpga节点的全局代价。

8.根据权利要求1所述的fpga间双模互连网络结构的映射方法,其特征在于,所述fpga间双模互连网络结构是指fpga间同时通过gt端口和lvds端口互联构成的fpga间双模互连网络结构。

9.一种fpga间双模互连网络结构的映射系统,包括相互连接的微处理器和存储器,其特征在于,所述微处理器被编程或配置以执行权利要求1~8中任意一项所述fpga间双模互连网络结构的映射方法。

10.一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,其特征在于,所述计算机程序用于被微处理器编程或配置以执行权利要求1~8中任意一项所述fpga间双模互连网络结构的映射方法。

技术总结

本发明公开了一种FPGA间双模互连网络结构的映射方法及系统,本发明方法包括确定待验证设计DUT中个划分块对外信号的传输需求;确定FPGA验证平台的FPGA节点对外的端口数量以及每一个端口的代价函数;根据划分块对外信号的传输需求、FPGA节点对外的端口数量实现划分块与FPGA节点之间的映射;针对每一个可用的FPGA节点,将映射至该FPGA节点的划分块的对外信号与该FPGA节点中的端口进行映射,使得该FPGA节点所有端口的代价函数的最大值最小。本发明旨在实现双模互连网络的映射以充分发挥双模互连网络端口的传输性能,得到全局端口传输信号尽可能均衡,最终使得整体性能最高。

技术研发人员:齐星云,陆亿行,赖明澈,王强,邓林,铁俊波,刘谱光,黎渊,陆平静,张磊,许超龙,曾洁,谭佳琦

受保护的技术使用者:中国人民解放军国防科技大学

技术研发日:

技术公布日:2024/8/20

- 还没有人留言评论。精彩留言会获得点赞!