用于优化数字逻辑电路的方法、计算机设备及存储介质与流程

本申请涉及数字逻辑电路,尤其涉及一种用于优化数字逻辑电路的方法、计算机设备及存储介质。

背景技术:

1、随着现代数字逻辑电路的规模越来越大,功能越来越复杂,用户对于电路的时序、功耗或者面积(performance power area,ppa)的要求越来越高,芯片设计师迫切需要数字电路的电子设计自动化(eda)工具可以高效地完成对电路的全局层面优化。因此,如何高效地对电路进行分析和优化成为了现代eda工具不可或缺的重要组成部分。

技术实现思路

1、有鉴于此,本申请的目的在于提出一种用于优化数字逻辑电路的方法、计算机设备及存储介质,以解决或部分解决上述问题。

2、基于上述目的,本申请第一方面,提供了一种用于优化数字逻辑电路的方法,包括:

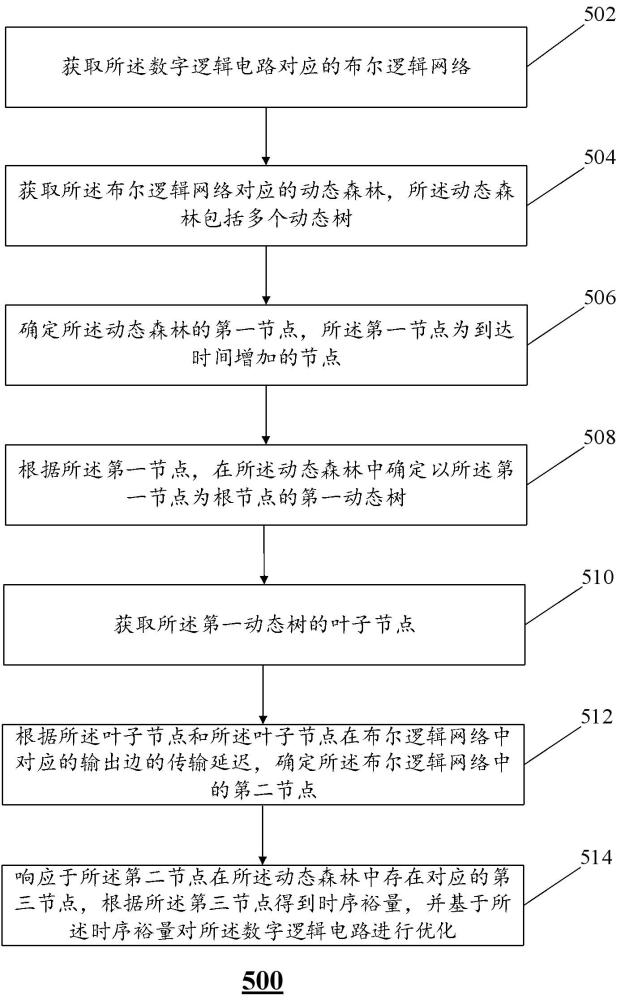

3、获取所述数字逻辑电路对应的布尔逻辑网络;

4、获取所述布尔逻辑网络对应的动态森林,所述动态森林包括多个动态树;

5、确定所述动态森林的第一节点,所述第一节点为到达时间增加的节点;

6、根据所述第一节点,在所述动态森林中确定以所述第一节点为根节点的第一动态树;

7、获取所述第一动态树的叶子节点;

8、根据所述叶子节点和所述第一节点的传输延迟,确定所述布尔逻辑网络中的第二节点;

9、响应于所述第二节点在所述动态森林中存在对应的第三节点,根据所述第三节点得到时序裕量,并基于所述时序裕量对所述数字逻辑电路进行优化。

10、本申请第二方面,提供了一种计算机设备,包括:

11、一个或者多个处理器、存储器;以及

12、一个或多个程序;

13、其中,所述一个或多个程序被存储在所述存储器中,并且被所述一个或多个处理器执行,所述程序包括用于执行如第一方面所述的方法的指令。

14、本申请第三方面,提供了一种包含计算机程序的非易失性计算机可读存储介质,当所述计算机程序被一个或多个处理器执行时,使得所述处理器执行如第一方面所述的方法。

15、从上面所述可以看出,本申请提供的一种用于优化数字逻辑电路的方法、计算机设备及存储介质。该方法通过与布尔逻辑网络对应的动态森林,确定动态森林中的到达时间增加的第一节点,根据第一节点,在动态森林中确定以第一节点为根节点的第一动态树,根据第一动态树的叶子节点以及该叶子节点的输出边的传输延迟,确定布尔逻辑网络中的第二节点,响应于第二节点在动态森林中存在对应的第三节点,根据第三节点得到时序裕量,并基于时序裕量对数字逻辑电路进行优化。该方法通过动态森林中的动态树来表征布尔逻辑网络中到达时间受到影响的节点,避免了布尔逻辑网络中的节点改动后需要重复遍历布尔逻辑网络的问题,进而可以大幅缩短eda工具对数字逻辑电路进行分析和优化的时间。

技术特征:

1.一种用于优化数字逻辑电路的方法,包括:

2.如权利要求1所述的方法,其中,所述根据所述第一节点,在所述动态森林中确定以所述第一节点为根节点的第一动态树进一步包括:

3.如权利要求2所述的方法,其中,所述根据所述第一节点,在所述动态森林中确定以所述第一节点为根节点的第一动态树进一步包括:

4.如权利要求1所述的方法,其中,所述响应于所述第二节点在所述动态森林中存在对应的第三节点,根据所述第三节点得到时序裕量进一步包括:

5.如权利要求4所述的方法,其中,所述方法还包括:

6.如权利要求3所述的方法,其中,所述断开所述第一节点和所述第一根节点的链接,以得到所述第一动态树进一步包括:

7.如权利要求1所述的方法,其中,所述根据所述第三节点得到时序裕量,并基于所述时序裕量对所述数字逻辑电路进行优化进一步包括:

8.如权利要求4所述的方法,其中,所述方法还包括:

9. 一种计算机设备,包括:

10.一种包含计算机程序的非易失性计算机可读存储介质,当所述计算机程序被一个或多个处理器执行时,使得所述处理器执行权利要求1-8中任一项所述的方法。

技术总结

本申请提供一种用于优化数字逻辑电路的方法、计算机设备及存储介质。该方法通过与布尔逻辑网络对应的动态森林,确定动态森林中的到达时间增加的第一节点,根据第一节点,在动态森林中确定以第一节点为根节点的第一动态树,根据第一动态树的叶子节点以及该叶子节点的输出边的传输延迟,确定布尔逻辑网络中的第二节点,响应于第二节点在动态森林中存在对应的第三节点,根据第三节点得到时序裕量,并基于时序裕量对数字逻辑电路进行优化。该方法通过动态森林中的动态树来表征布尔逻辑网络中到达时间受到影响的节点,避免了布尔逻辑网络中的节点改动后需要重复遍历布尔逻辑网络的问题,进而可以大幅缩短EDA工具对电路进行分析和优化的时间。

技术研发人员:邢自然

受保护的技术使用者:芯行纪科技有限公司

技术研发日:

技术公布日:2024/7/18

- 还没有人留言评论。精彩留言会获得点赞!