PCIe设备、电子组件及电子设备的制作方法

本公开涉及数据处理,尤其涉及一种pcie设备、电子组件及电子设备。

背景技术:

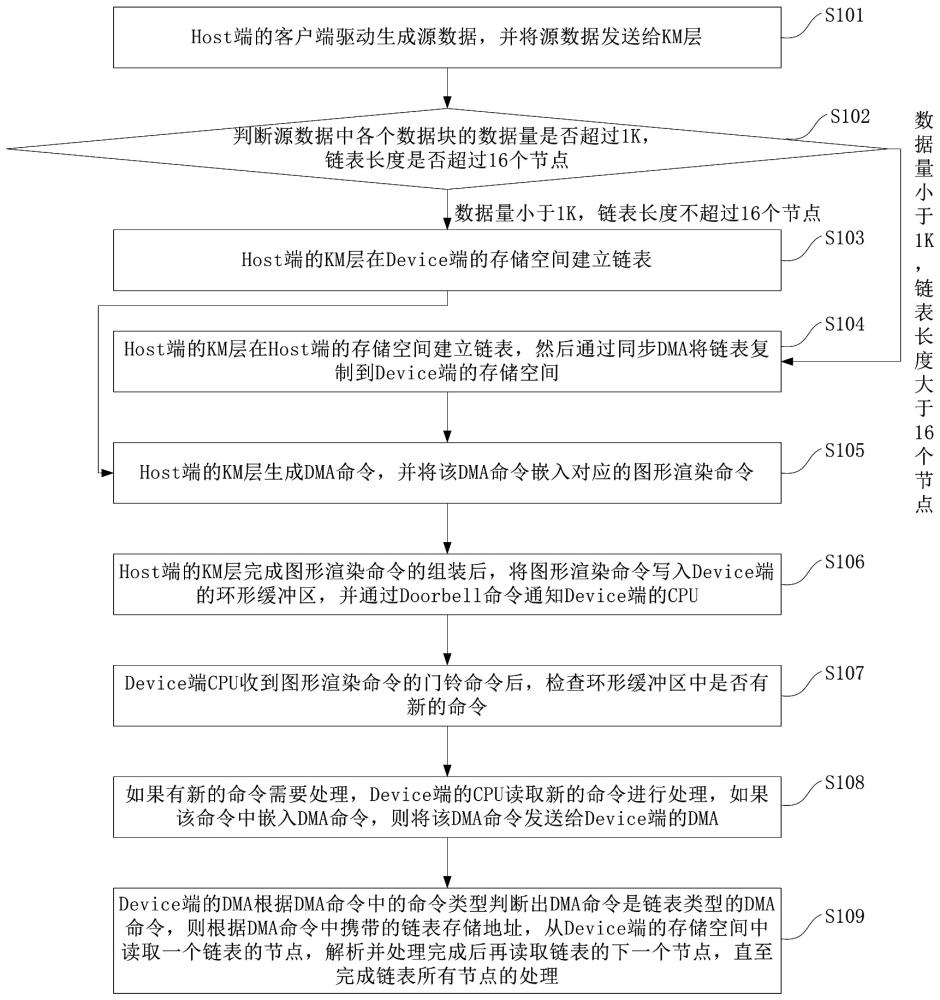

1、直接内存访问(direct memory access,dma)通常用于内存间的数据搬运,一种典型的数据搬运场景是通过pcie总线将数据从host(主机端)搬运至device(设备端)。传统搬运过程如下:host在本地存储空间中创建待传输数据的链表以及dma命令,device接收dma命令,根据dma命令进行数据搬运。具体的,device每次从host的存储空间中读取链表中一个节点对应的数据块,完成一个数据块的搬运再进行下一个数据块的搬运。当链表中一个节点对应的数据块的数据量较小时,会出现数据断断续续的传输,从而影响整个链路的传输带宽。

技术实现思路

1、本公开的目的是提供一种pcie设备、电子组件及电子设备,以提升链路传输带宽。

2、根据本公开的一个方面,提供一种电子组件,该电子组件包括存储器和处理器,存储器存储有计算机程序,处理器执行存储器中存储的计算机程序,以实现如下处理过程:判断待组装成链表数据结构的各个数据块的数据量是否超过预设数据量;在所述各个数据块的数据量均未超过预设数据量的情况下,将所述各个数据块对应的链表存储至pcie设备端的存储空间;生成dma命令,所述dma命令中携带命令类型信息和所述链表在所述pcie设备端的存储地址,所述命令类型信息用于指示所述dma命令的命令类型是否为链表命令类型;将所述dma命令关联至数据处理任务命令;将所述数据处理任务命令写入所述pcie设备端的环形缓冲区,并通过门铃机制向pcie设备发送命令通知。

3、可选的,在生成dma命令之前,所述处理器执行所述存储器中存储的计算机程序,以实现如下处理步骤:判断所述各个数据块对应的链表的链表长度是否超过预设链表长度。所述在所述各个数据块的数据量均未超过预设数据量的情况下,将所述各个数据块对应的链表存储至pcie设备端的存储空间,包括:在所述各个数据块的数据量均未超过预设数据量且所述链表长度未超过预设链表长度的情况下,在所述pcie设备端的存储空间建立所述链表;在所述各个数据块的数据量均未超过预设数据量但所述链表长度超过预设链表长度的情况下,在本端存储空间建立所述链表,并通过本端的同步dma将所述链表拷贝至所述pcie设备端的存储空间。

4、可选的,所述预设数据量为1k,所述预设链表长度为16个节点。

5、可选的,在所述各个数据块的数据量均未超过预设数据量的情况下,所述处理器执行所述存储器中存储的计算机程序,以实现如下处理步骤:将所述各个数据块嵌入所述链表中的对应节点。

6、根据本公开的另一方面,本公开提供一种pcie设备,该pcie设备包括存储器、处理器和dma,所述存储器存储有计算机程序,所述处理器执行所述存储器中存储的计算机程序,以实现如下过程:收到通过门铃机制发送的命令通知后,查找环形缓冲区中是否有新的数据处理任务命令;如果查找到新的数据处理任务命令,判断所述数据处理任务命令是否关联有dma命令;如果关联有dma命令,将所述dma命令发送给所述dma;所述dma被配置为:根据所述dma命令中携带的命令类型信息判断所述dma命令的命令类型是否为链表命令类型;如果所述dma命令的命令类型为链表命令类型,根据所述dma命令携带的链表在pcie设备端的存储地址获取所述链表,并根据所述链表获取组装成链表数据结构的各个数据块。

7、可选的,为了根据所述链表获取组装成链表数据结构的各个数据块,所述dma被配置为:从所述链表的各个节点中获取组装成链表数据结构的各个数据块。

8、可选的,所述各个数据块的数据量均未超过预设数据量,且所述链表的链表长度未超过预设链表长度。

9、可选的,所述预设数据量为1k,所述预设链表长度为16个节点。

10、根据本公开的另一方面,提供一种电子组件,包括上述任一实施例所述的pcie设备。

11、根据本公开的另一方面,提供一种电子设备,包括上述任一实施例所述的电子组件。

技术特征:

1.一种电子组件,包括存储器和处理器,所述存储器存储有计算机程序,所述处理器执行所述存储器中存储的计算机程序,以实现如下处理过程:

2.根据权利要求1所述的电子组件,在生成dma命令之前,所述处理器执行所述存储器中存储的计算机程序,以实现如下处理步骤:判断所述各个数据块对应的链表的链表长度是否超过预设链表长度;

3.根据权利要求2所述的电子组件,所述预设数据量为1k,所述预设链表长度为16个节点。

4.根据权利要求1所述的电子组件,在所述各个数据块的数据量均未超过预设数据量的情况下,所述处理器执行所述存储器中存储的计算机程序,以实现如下处理步骤:将所述各个数据块嵌入所述链表中的对应节点。

5.一种pcie设备,包括存储器、处理器和dma,所述存储器存储有计算机程序,所述处理器执行所述存储器中存储的计算机程序,以实现如下过程:

6.根据权利要求5所述的pcie设备,为了根据所述链表获取组装成链表数据结构的各个数据块,所述dma被配置为:

7.根据权利要求5所述的pcie设备,所述各个数据块的数据量均未超过预设数据量,且所述链表的链表长度未超过预设链表长度。

8.根据权利要求7所述的pcie设备,所述预设数据量为1k,所述预设链表长度为16个节点。

9.一种电子组件,包括权利要求5至8任一项所述的pcie设备。

10.一种电子设备,包括权利要求1至4任一项所述的电子组件,和/或,权利要求9所述的电子组件。

技术总结

本公开提供一种PCIe设备、电子组件及电子设备,适用于通过PCIe总线将数据从主机搬运至设备。其中,主机判断待组装成链表数据结构的各个数据块的数据量,如果数据量都小于预定数据量,则将数据块对应的链表存储至设备存储空间。生成DMA命令,将其与数据处理任务命令绑定并通过门铃通知设备。设备接收到门铃通知,检查是否有新的数据处理任务命令,如果有则执行,并检查新的数据处理任务命令是否关联有DMA命令,如果有,将DMA命令发送给DMA。DMA判断是否是链表类型的DMA命令,如果是,DMA从设备的存储空间相应的地址获取并解析链表,相对于直接访问存在于主机的存储空间中的链表,能够节省一定的延迟开销。

技术研发人员:梁建胜

受保护的技术使用者:北京象帝先计算技术有限公司

技术研发日:

技术公布日:2024/7/23

- 还没有人留言评论。精彩留言会获得点赞!