处理电路以及用于处理电路的操作方法与流程

本发明涉及一种电子电路以及用于电子电路的操作方法,尤其是涉及一种能够优化数据访问操作的处理电路以及用于处理电路的操作方法。

背景技术:

1、一般来说,现有的处理电路(如图形处理器(graphics processing unit,gpu))可利用加载/存储(ld/st)单元来传输数据。然而,加载/存储单元的带宽(bandwidth)有限。处理电路仅利用加载/存储单元很难充分利用片上网络(network-on-chip,noc)的带宽。因此,如何优化处理电路的数据访问操作,是本领域技术人员的研究重点之一。

技术实现思路

1、本发明提供一种能够优化数据访问操作的处理电路以及用于处理电路的操作方法。

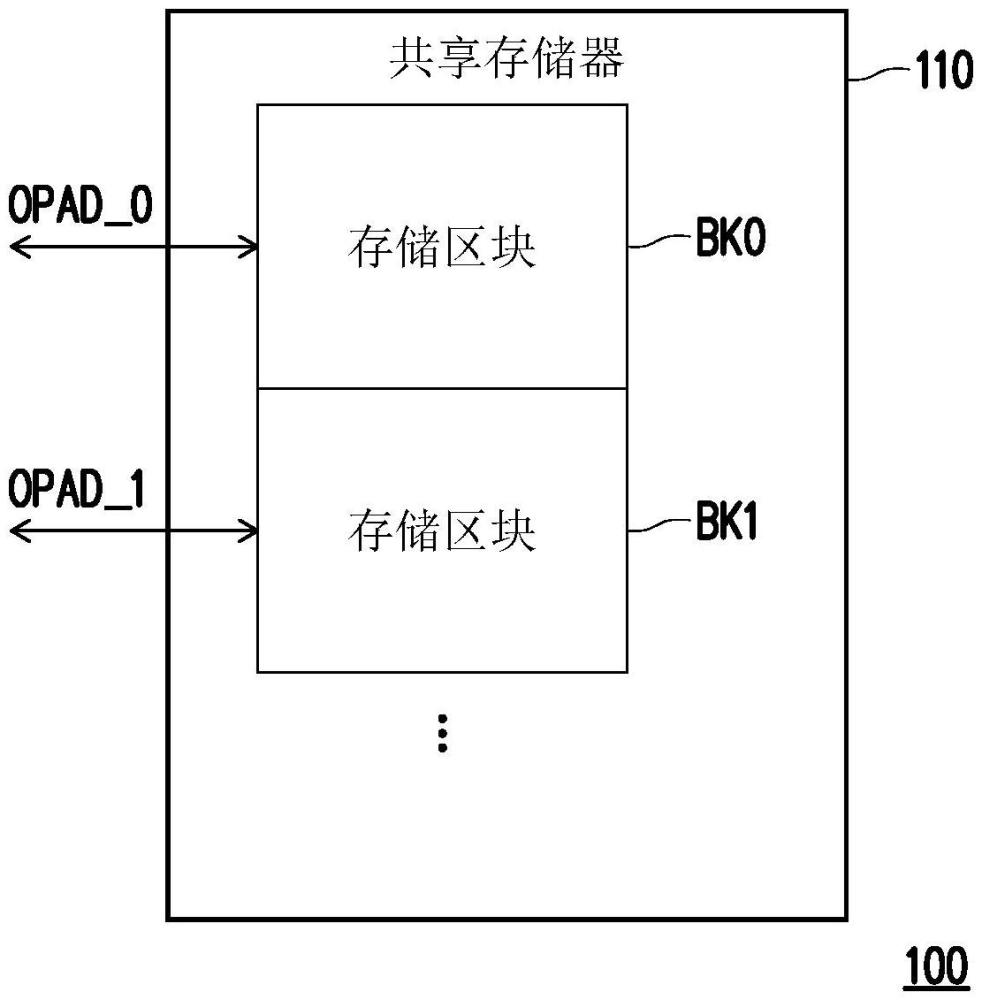

2、根据本发明的实施例,处理电路包括共享存储器。共享存储器执行多个循环的流水线(pipeline)数据访问操作。共享存储器包括第一存储区块以及第二存储区块。第一存储区块在所述多个循环当中的单一循环期间执行第一数据访问操作。第二存储区块在相同的单一循环期间执行第二数据访问操作。第一数据访问操作不同于第二数据访问操作。

3、根据本发明的实施例,操作方法适用于处理电路。处理电路包括共享存储器。操作方法包括:将共享存储器区分为多个存储区块;以及执行多个循环的流水线数据访问操作。执行所述多个循环的流水线数据访问操作包括:在所述多个循环当中的单一循环期间,由所述多个存储区块当中的第一存储区块执行第一数据访问操作;以及在相同的单一循环期间,由所述多个存储区块当中的第二存储区块执行第二数据访问操作。第一数据访问操作不同于第二数据访问操作。

4、基于上述,处理电路利用共享存储器来参与多个循环的流水线数据访问操作。此外,第一存储区块以及第二存储区块在相同的循环期间分别执行不同的数据访问操作。基于共享存储器,处理电路能够充分利用片上网络(network-on-chip,noc)的带宽。如此一来,处理电路的数据访问操作能够被优化。

技术特征:

1.一种处理电路,其特征在于,所述处理电路包括:

2.根据权利要求1所述的处理电路,其特征在于,所述处理电路还包括:

3.根据权利要求2所述的处理电路,其特征在于:

4.根据权利要求3所述的处理电路,其特征在于:

5.根据权利要求3所述的处理电路,其特征在于,所述共享存储器还包括:

6.根据权利要求5所述的处理电路,其特征在于,所述第三缓冲器是输出缓冲器。

7.根据权利要求5所述的处理电路,其特征在于,所述处理电路还包括:

8.根据权利要求7所述的处理电路,其特征在于,所述执行单元对所述第一数据以及所述第二数据执行运算以产生运算数据,并将所述运算数据提供至所述第三存储区块。

9.根据权利要求5所述的处理电路,其特征在于,所述第三存储区块与其他处理电路的全局存储器执行第四数据访问操作。

10.根据权利要求2所述的处理电路,其特征在于:

11.一种用于处理电路的操作方法,其特征在于,所述处理电路包括共享存储器,其中所述操作方法包括:

12.根据权利要求11所述的操作方法,其特征在于,所述处理电路还包括全局存储器,其中执行所述第一数据访问操作的步骤包括:

13.根据权利要求12所述的操作方法,其特征在于,由所述全局存储器与所述第一存储区块共同执行所述第一数据访问操作的步骤包括:

14.根据权利要求12所述的操作方法,其特征在于,执行所述第一数据访问操作的步骤包括:

15.根据权利要求14所述的操作方法,其特征在于,由所述全局存储器与所述第二存储区块共同执行所述第二数据访问操作的步骤包括:

16.根据权利要求15所述的操作方法,其特征在于,所述操作方法还包括:

17.根据权利要求16所述的操作方法,其特征在于,所述处理电路还包括执行单元,其中所述操作方法还包括:

18.根据权利要求17所述的操作方法,其特征在于,其中所述操作方法还包括:

19.根据权利要求16所述的操作方法,其特征在于,还包括:

20.根据权利要求12所述的操作方法,其特征在于:

技术总结

本发明提供一种处理电路以及用于处理电路的操作方法。处理电路包括共享存储器。共享存储器执行多个循环的流水线(pipeline)数据访问操作。共享存储器包括第一存储区块以及第二存储区块。第一存储区块在所述多个循环当中的单一循环期间执行第一数据访问操作。第二存储区块在相同的单一循环期间执行第二数据访问操作。第一数据访问操作不同于第二数据访问操作。处理电路能够优化数据访问操作。

技术研发人员:请求不公布姓名,请求不公布姓名

受保护的技术使用者:上海壁仞科技股份有限公司

技术研发日:

技术公布日:2024/10/10

- 还没有人留言评论。精彩留言会获得点赞!