一种基于FPGA实现Hindmarsh-Rose神经元耦合放电的方法

本发明属于神经元模型,具体涉及一种基于fpga实现hindmarsh-rose神经元耦合放电的方法。

背景技术:

1、神经元作为神经系统的基本组成部分,具有显著的非线性特征。神经系统在传递信息时,神经元通过调整电位差在单个神经元内传递信号,通过电耦合和化学耦合作用在不同神经元之间传递信号。神经元的信息传递方式吸引了许多学者的研究。在过去的几十年内,学者建立了众多的描述神经元放电活动的数学模型,用以研究其非线性动力学特征。

2、1984年,在蜗牛神经元电压钳实验的基础上,hindmarsh和rose提出了hindmarsh-rose(简称hr)神经元模型,并在之后以三个一阶非线性微分方程进行修正,使之表现出尖峰和簇放电。后续学者们通过改变神经元模型的维数和激励,对hr神经元的非线性动力学进行了多样化的研究。

3、神经元模型在外部激励下具有敏感的放电行为,在周期性激励下能表现出多种周期放电状态和混沌放电状态。通过利用hr神经元具有的激励敏感性和抗噪声能力,能够识别信号中的周期特征,为弱周期信号的检测提供依据,对于信号检测领域有重要的研究价值。

4、此外,hr神经元具有独特的的混沌放电特性。基于电耦合技术,可以实现两个神经元之间的近似同步,进而产生两个同步的混沌信号。使用混沌信号作为载波或调制成分,在输送端对通讯信号进行加密,在接收端通过同步的混沌信号进行解密,这对于信号的加密解密有重要意义。

5、考虑到hr神经元的非线性特征与模型参数等紧密相关,传统的模型电路具有固定的参数设置,较难满足变参数的需求;且大规模使用时电路的可靠性及系统的适应性难以保证。

技术实现思路

1、为了克服现有技术的不足,本发明提供了一种基于fpga实现hindmarsh-rose神经元耦合放电的方法,首先对具有周期激励的hindmarsh rose神经元进行离散处理,得到离散的神经元模型;其次将两个hindmarsh rose神经元进行电耦合连接,得到离散的双电耦合hindmarsh rose神经元模型;最后通过f pga平台实现hindmarsh rose神经元放电与耦合放电,完成耦合神经元的混沌同步现象。本发明具有参数选择性广、运算精准度高和集成度高等特点,对神经元耦合放电行为和信号加密传输的应用具有重大意义。

2、本发明解决其技术问题所采用的技术方案如下:

3、步骤1:构建单个hr神经元离散模型;

4、步骤2:构建双-电耦合hr神经元离散模型;

5、步骤3:基于fpga实现单个hr神经元的放电以及双-电耦合hr神经元的放电与混沌同步。

6、进一步地,所述步骤1具体为:

7、步骤1-1:具有周期性激励的hr神经元的微分方程数学表达式如下:

8、

9、其中,x表示神经元的膜电位,y表示恢复变量,z表示自适应变量;χ为稳态阈值平衡点,ie表示外部的周期性激励,a、b、c和d是系统常数,r和s是控制发射状态的控制参数;

10、ie=i+q0cosωt

11、其中,i为外部激励的直流分量,q0 cosωt为外部激励的交流分量,q0为交流幅值,ω为交流频率;

12、步骤1-2:使用前向欧拉方法对微分方程进行处理,得到离散hr神经元模型:

13、

14、其中,n为一个周期的离散点数;xi、yi、zi表示离散神经元方程每一步迭代的起点,xi+1、yi+1、zi+1表示离散神经元方程每一步迭代的终点。

15、进一步地,所述步骤2具体为:

16、步骤2-1:将两个离散hr神经元模型进行电耦合,构建双-电耦合hr神经元模型,其数学表达式如下:

17、

18、其中,x1、x2为两个耦合神经元的膜电位输出,y1、y2为两个耦合神经元的恢复变量输出,z1、z2为两个耦合神经元的自适应变量输出,ie1、ie2为两个神经元的外部周期激励,c为电耦合强度系数;

19、步骤2-2:使用前向欧拉方法对双-电耦合hr神经元模型进行离散化:

20、

21、其中,hr1为驱动神经元模型,hr2为响应神经元模型,表示hr1的每一步迭代起点,表示hr1的每一步迭代终点,表示hr2的每一步迭代起点,表示hr2的每一步迭代终点。

22、进一步地,所述步骤3具体为:

23、基于fpga平台,制作单个的离散hr神经元电路模型,具体描述如下:

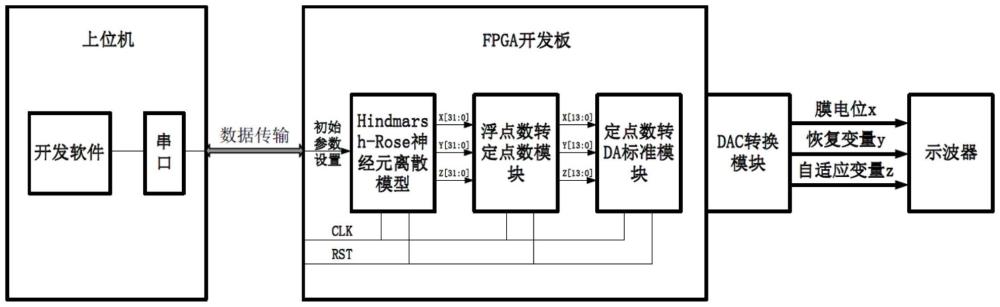

24、所述离散hr神经元电路模型包括上位机、fpga开发板、dac转换模块和示波器;fpga开发板包括hr神经元模型离散模块、浮点数转定点数模块和定点数转da标准模块;hr神经元模型离散模块包括四个浮点数乘法器、一个浮点数加法器、一个浮点数减法器和若干寄存器;

25、编写verilog形式的hr神经元的离散求解算法,通过串口下载到fpga芯片中;在开发软件中将模型的各参数设置完成;fpga运行离散求解算法,算出一次迭代的输出值后,一方面将此输出值替换为初值进行迭代运算,另一方面将输出值输送到浮点数转定点数模块;浮点数转定点数模块将32位标准浮点数转换为14位有符号定点数,并将定点数输送到定点数转da标准模块;定点数转da标准模块将14位有符号整数转换为符合da转换标准的数据;随后dac转换模块将数字量输出转换为模拟量输出,并经示波器捕捉成像在屏幕上;

26、基于单个hr神经元离散模型的实现方法,将两个hr神经元离散模型的x输出值通过减法器和乘法器关联起来,取代原输出值参与迭代运算,得到双-电耦合hr神经元模型。

27、本发明的有益效果如下:

28、本发明基于fpga技术构建hr神经元电路模型,与传统电路相比,可以自由的选择模型参数而不需要更换电路元件。模型的32位浮点数标准能够保证计算过程与结果的精度,方便进行理论验证和分析。当输入不同的周期性激励时,此模型将表现复杂的非线性动力学行为,包括短周期放电、长周期放电和混沌放电,对神经元的放电行为研究和应用有很大意义。其次,将两个单独的hr神经元进行电耦合,并在fpga平台上进行实现。通过耦合,控制两个神经元的放电活动,并使之达到完全同步。基于此,本发明可以实现精准的混沌同步,进而产生两个绝对近似的混沌数据,这在信号加密,通讯传输等领域有广泛的应用前景。

技术特征:

1.一种基于fpga实现hindmarsh-rose神经元耦合放电的方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的一种基于fpga实现hindmarsh-rose神经元耦合放电的方法,其特征在于,所述步骤1具体为:

3.根据权利要求2所述的一种基于fpga实现hindmarsh-rose神经元耦合放电的方法,其特征在于,所述步骤2具体为:

4.根据权利要求3所述的一种基于fpga实现hindmarsh-rose神经元耦合放电的方法,其特征在于,所述步骤3具体为:

技术总结

本发明公开了一种基于FPGA实现Hindmarsh‑Rose神经元耦合放电的方法,首先对具有周期激励的Hindmarsh Rose神经元进行离散处理,得到离散的神经元模型;其次将两个Hindmarsh Rose神经元进行电耦合连接,得到离散的双电耦合Hindmarsh Rose神经元模型;最后通过F PGA平台实现Hindmarsh Rose神经元放电与耦合放电,完成耦合神经元的混沌同步现象。本发明具有参数选择性广、运算精准度高和集成度高等特点,对神经元耦合放电行为和信号加密传输的应用具有重大意义。

技术研发人员:刘雁,沈英杰,毛陶恺,杨泽华

受保护的技术使用者:西北工业大学

技术研发日:

技术公布日:2024/9/23

- 还没有人留言评论。精彩留言会获得点赞!