地址生成系统的制作方法

本申请涉及处理器,具体地,涉及一种地址生成系统。

背景技术:

1、现有的agu(address generation unite,地址生成单元),通常设置在处理器的执行模块中,agu用于生成访存操作的对应的地址,执行模块的结构如图1所示。

2、相关技术中,在agu的加法器部分都是对指令的第一个寄存器索引的源操作数和符号位扩展的立即数相加,例如指令为:load x10,imm(x9);如图2所示,对于一个32位的处理器,x9的地址位宽为32位,imm立即数一般为12位,对于地址相加部分即为32位数据加上12位的数据,如果处理器的内核为64位即为64位数据加上12位数据。

3、参见图1,在经过加法器获得指令正确的访存地址之后,经过apc(addresspermission check,地址权限检查)单元,在该单元根据处理器的设置限制访存地址的访问位置,之后未通过权限的访问不访问存储器(或者不产生造成对处理器数据和状态造成改变的存储器访问),并导致处理器产生同步异常。若通过权限,对于读访问则获取对应访存地址的相应数据并返回读完成的响应,对于写访问则将数据写入对应的访存地址并返回写完成的响应。存储器访问的操作,在agu之后通过lsu(load store unit,访存单元)发往相应的存储模块。

4、agu产生读/写指令的访存地址,读/写指令需要将其第一个寄存器索引的源操作数和符号位扩展的立即数相加,得到最终的访存地址,因此,理论上需要使用到加法器。然而,现有的技术对于32位的处理器是使用32位的地址加上12位的立即数,那么,此时无论是加法器的面积,还是经过加法器的时序都是很差的。如果处理器是64位那么是使用64位的地址加上12位的立即数,那就更加影响时序。在加法器获得地址之后,使用apc进行内存保护,这也包含了一段组合逻辑。因此,在经过agu的加法器和apc的内存保护之后,生成地址的时序变得十分长,如果把agu和apc用一个时钟周期完成,会限制处理器的最高主频,从而影响处理器的性能。

技术实现思路

1、本申请实施例中提供了一种地址生成方法、装置、计算机设备和存储介质。

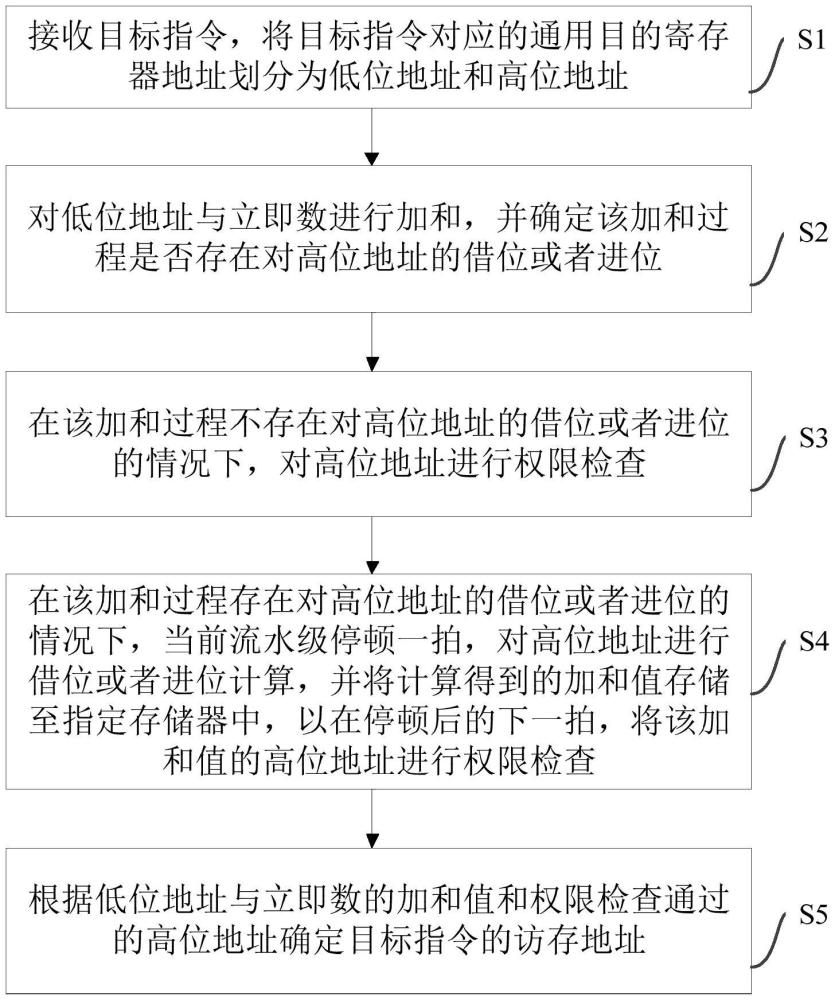

2、本申请实施例的第一个方面,提供了一种地址生成方法,包括:

3、接收目标指令,将目标指令对应的通用目的寄存器地址划分为低位地址和高位地址;

4、对低位地址与立即数进行加和,并确定该加和过程是否存在对高位地址的借位或者进位;

5、在该加和过程不存在对高位地址的借位或者进位的情况下,对高位地址进行权限检查;

6、在该加和过程存在对高位地址的借位或者进位的情况下,当前流水级停顿一拍,对高位地址进行借位或者进位计算,并将计算得到的加和值存储至指定存储器中,以在停顿后的下一拍,将该加和值的高位地址进行权限检查;

7、根据低位地址与立即数的加和值和权限检查通过的高位地址确定目标指令的访存地址。

8、在本申请一个可选的实施例中,低位地址的位数大于或等于立即数的位数。

9、在本申请一个可选的实施例中,所述对低位地址与立即数进行加和,包括:

10、在低位地址的位数与立即数的位数相等的情况下,直接对低位地址与立即数进行加和;

11、在低位地址的位数大于立即数的位数的情况下,对立即数的位数进行符号扩展,得到与低位地址的位数相等的立即数,对低位地址与扩展后的立即数进行加和。

12、在本申请一个可选的实施例中,所述确定该加和过程是否存在对高位地址的借位或者进位,包括:

13、在立即数为正数的情况下,确定该加和过程是否存在对高位地址的进位;

14、在立即数为负数的情况下,确定该加和过程是否存在对高位地址的借位。

15、在本申请一个可选的实施例中,所述根据低位地址与立即数的加和值和权限检查通过的高位地址确定目标指令的访存地址,包括:

16、对低位地址与立即数的加和值和权限检查通过的高位地址进行拼接,得到目标指令的访存地址。

17、在本申请一个可选的实施例中,所述方法还包括:

18、在高位地址未通过权限检查的情况下,生成异常标志,并将异常标志发送至异常处理单元。

19、在本申请一个可选的实施例中,所述方法还包括:

20、在目标指令为读指令的情况下,获取目标指令的访存地址的数据,并返回读完成的响应;

21、在目标指令为写指令的情况下,将目标指令中的数据写入目标指令的访存地址,并返回写完成的响应。

22、本申请实施例的第二个方面,提供了一种地址生成装置,包括:

23、划分模块,用于接收目标指令,将目标指令对应的通用目的寄存器地址划分为低位地址和高位地址;

24、第一确定模块,用于对低位地址与立即数进行加和,并确定该加和过程是否存在对高位地址的借位或者进位;

25、停顿模块,用于在该加和过程存在对高位地址的借位或者进位的情况下,当前流水级停顿一拍,对高位地址进行借位或者进位计算;

26、检查模块,用于在该加和过程不存在对高位地址的借位或者进位的情况下,对高位地址进行权限检查,在该加和过程存在对高位地址的借位或者进位的情况下,并将计算得到的加和值存储至指定存储器中,以在停顿后的下一拍,将该加和值的高位地址进行权限检查;

27、第二确定模块,用于根据低位地址与立即数的加和值和权限检查通过的高位地址确定目标指令的访存地址。

28、本申请实施例的第三个方面,提供了一种计算机设备,包括:包括存储器和处理器,存储器存储有计算机程序,处理器执行计算机程序时实现如上任一项方法的步骤。

29、本申请实施例的第四个方面,提供了一种计算机可读存储介质,其上存储有计算机程序,计算机程序被处理器执行时实现如上任一项的方法的步骤。

技术特征:

1.一种地址生成系统,其特征在于,包括依次连接的取指单元、解码单元、执行单元和异常处理单元,其中,执行单元包括算数逻辑单元和地址权限检查单元,算数逻辑单元包括地址生成单元,

2.根据权利要求1所述的地址生成系统,其特征在于,低位地址的位数大于或等于立即数的位数。

3.根据权利要求1所述的地址生成系统,其特征在于,所述根据低位地址与立即数的加和值和权限检查通过的高位地址确定目标指令的访存地址,包括:

4.根据权利要求1所述的地址生成系统,其特征在于,所述执行单元,与解码单元之间设置有其他单元,用于接收指令的通用目的寄存器地址和立即数,对指令进行派遣、执行、交付,其中,其他单元是取指单元、解码单元、执行单元中的任意一种或者任意几种。

5.根据权利要求1所述的地址生成系统,其特征在于,所述异常处理单元与执行单元之间设置有其他单元,其中,其他单元可以是取指单元、解码单元、执行单元中的任意一种或者任意几种。

技术总结

本申请实施例提供一种地址生成方法、装置、计算机设备和存储介质,所述方法包括:接收目标指令,将目标指令对应的通用目的寄存器地址划分为低位地址和高位地址;对低位地址与立即数进行加和,并确定该加和过程是否存在对高位地址的借位或者进位;若不存在,对高位地址进行权限检查;若存在,当前流水级停顿一拍,对高位地址进行借位或者进位计算,并将计算得到的加和值存储至指定存储器中,以在停顿后的下一拍,将该加和值的高位地址进行权限检查;根据低位地址与立即数的加和值和权限检查通过的高位地址确定目标指令的访存地址,仅对截断后低位和立即数进行加和,并在APC处仅对高位检查,使得AGU加法器的时序优化同时断开APC的时序。

技术研发人员:胡振波,彭剑英,梁智兵

受保护的技术使用者:芯来智融半导体科技(上海)有限公司

技术研发日:

技术公布日:2024/10/31

- 还没有人留言评论。精彩留言会获得点赞!