用于降低L1带宽要求的分布式寄存器堆缓存的制作方法

本公开一般地涉及经由图形处理器的数据处理,并且更具体地涉及用于降低对图形处理器内的第一级(l1)缓存所施加的带宽要求的分布式寄存器堆缓存。

背景技术:

1、图形处理器通常采用的大型寄存器堆能够实现大量数据元素的同时存储。然而,图形处理器内的高数据吞吐量逻辑(诸如矩阵操作加速器)可以以高速度从寄存器堆读取和写入数据。针对高吞吐量操作从存储器加载新数据以供应输入数据的过程可消耗图形处理器的缓存存储器(尤其是l1缓存存储器)的很大一部分带宽。

技术实现思路

技术特征:

1.一种图形处理器,包括:

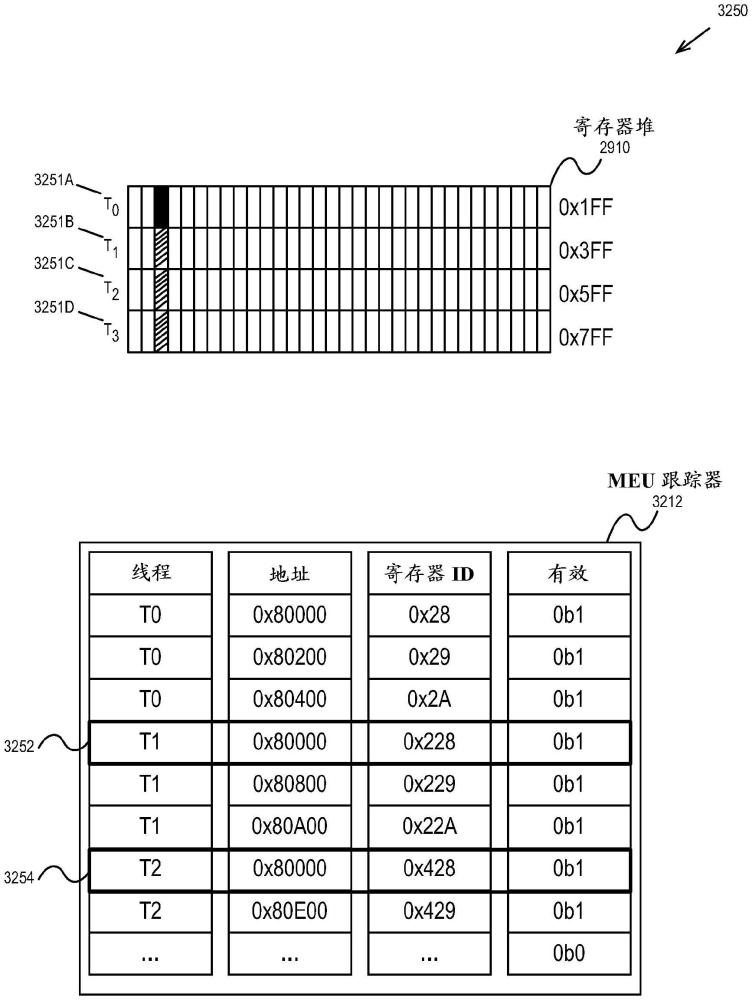

2.根据权利要求1所述的图形处理器,所述第一电路用于:接收与所述第一硬件线程相关联的用于在存储器中的地址与所述第一多个寄存器中的寄存器之间传递数据的第一存储器访问请求,处理所述第一存储器访问请求,以及将所述第一存储器访问请求的元数据存储到跟踪表中的条目。

3.根据权利要求2所述的图形处理器,其中,处理所述第一存储器访问请求包括读取与所述存储器中的地址相关联的第一数据以及将所述第一数据写入所述第一多个寄存器中的寄存器。

4.根据权利要求3所述的图形处理器,所述第一电路用于:

5.根据权利要求4所述的图形处理器,所述第一电路用于:

6.根据权利要求1-5中任一项所述的图形处理器,包括第二电路,所述第二电路被配置成执行用于对输入矩阵数据执行矩阵乘法和累加操作的单个指令。

7.根据权利要求6所述的图形处理器,所述第二电路用于经由所述第一硬件线程对所述输入矩阵数据的第一部分执行所述矩阵乘法和累加操作并且经由所述第二硬件线程对所述输入矩阵数据的第二部分执行所述矩阵乘法和累加操作。

8.根据权利要求7所述的图形处理器,其中,所述输入矩阵数据的所述第一部分包括第一多个列数据元素和第一多个行数据元素;并且其中,所述输入矩阵数据的所述第二部分包括所述第一多个列数据元素和第二多个行数据元素。

9.根据权利要求8所述的图形处理器,所述第一电路用于:

10.根据权利要求9所述的图形处理器,其中,存储器访问请求的所述元数据包括与所述存储器访问请求相关联的寄存器标识符、存储器地址和线程标识符。

11.一种方法,包括:

12.根据权利要求11所述的方法,其中,所述消息集合的所述元数据包括线程标识符、存储器地址和寄存器标识符。

13.根据权利要求11或12所述的方法,包括:

14.根据权利要求13所述的方法,其中,输入矩阵数据的所述第一子集包括第一多个列数据元素和第一多个行数据元素,并且输入矩阵数据的所述第二子集包括所述第一多个列数据元素和第二多个行数据元素。

15.一种系统,所述系统包括用于执行如权利要求11-14中任一项所述的方法的部件。

16.一种图形处理系统,包括:

17.根据权利要求16所述的图形处理系统,所述第一电路用于:接收与所述第一硬件线程相关联的用于在存储器中的地址与所述第一多个寄存器中的寄存器之间传递数据的第一存储器访问请求,处理所述第一存储器访问请求,以及将所述第一存储器访问请求的元数据存储到跟踪表中的条目。

18.根据权利要求17所述的图形处理系统,其中,处理所述第一存储器访问请求包括读取与所述存储器中的地址相关联的第一数据以及将所述第一数据写入所述第一多个寄存器中的寄存器。

19.根据权利要求18所述的图形处理系统,所述第一电路用于:

20.根据权利要求19所述的图形处理系统,所述第一电路用于:

21.根据权利要求20所述的图形处理系统,包括第二电路,所述第二电路被配置成执行用于对输入矩阵数据执行矩阵乘法和累加操作的单个指令。

22.根据权利要求21所述的图形处理系统,所述第二电路用于经由所述第一硬件线程对所述输入矩阵数据的第一部分执行所述矩阵乘法和累加操作并且经由所述第二硬件线程对所述输入矩阵数据的第二部分执行所述矩阵乘法和累加操作。

23.根据权利要求22所述的图形处理系统,其中,所述输入矩阵数据的所述第一部分包括第一多个列数据元素和第一多个行数据元素,并且其中,所述输入矩阵数据的所述第二部分包括所述第一多个列数据元素和第二多个行数据元素。

24.根据权利要求23所述的图形处理系统,所述第一电路用于:

25.根据权利要求24所述的图形处理器,其中,存储器访问请求的所述元数据包括与所述存储器访问请求相关联的寄存器标识符、存储器地址和线程标识符。

技术总结

本公开的发明名称是“用于降低L1带宽要求的分布式寄存器堆缓存”。本文中描述了一种包括与存储器接口耦合的图形处理集群的图形处理器,所述图形处理集群包括多个处理资源,所述多个处理资源中的处理资源包括:寄存器堆,所述寄存器堆包括与处理资源的多个硬件线程中的第一硬件线程相关联的第一多个寄存器以及与处理资源的多个硬件线程中的第二硬件线程相关联的第二多个寄存器;以及第一电路,所述第一电路被配置成促进代表多个硬件线程对存储器的访问以及存储来自多个硬件线程的存储器访问请求的元数据。

技术研发人员:J·E·P·奥索里奥,陈佳升,S·帕尔,J·瓦莱里奥

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2025/2/27

- 还没有人留言评论。精彩留言会获得点赞!