本发明涉及一种人工智能芯片领域,且特别涉及一种运算装置及数据存取同步方法。

背景技术:

1、在人工智能(artificial intelligence,ai)应用中,通用计算应用问题的规模愈来愈大,且通常会把问题切分成多个小的工作量(workload),然后使这些工作量通过并行处理器来执行并行计算,缩短计算所需的时间。通用图形处理器(gpgpu)是当前常用的并行处理器。

2、并行计算中需要解决的问题是数据一致性(data consistency),也就是,存储于内存中的数据对于并行执行的生产者(producer)及消费者(consumer)间的可见性。通常是通过对数据设置缓存就绪旗标与数据就绪旗标来使作为生产者及消费者的计算单元能够相互告知数据是否可被存取,但前述旗标的设置主要是由计算单元来实施,使得前述旗标的设置会产生延迟和通讯的时间开销。

技术实现思路

1、本发明是针对一种运算装置及数据存取同步方法,可降低缓存就绪与数据就绪所耗费的时间开销。

2、根据本发明的实施例,运算装置包括第一运算单元、第二运算单元、总线、第二总线接口装置以及内存装置。所述第一运算单元耦接所述总线。所述第二运算单元通过所述第二总线接口装置耦接所述总线。所述内存装置通过所述第二总线接口装置耦接所述总线。所述内存装置包括数据存储区域及对应于所述数据存储区域的同步旗标。所述第二总线接口装置基于所述第一运算单元及所述第二运算单元中的其中一者所发出的对所述内存装置的存储指令或读取指令而设置所述同步旗标,以使所述第一运算单元及所述第二运算单元中的其中另一者读取或存储所述数据存储区域。

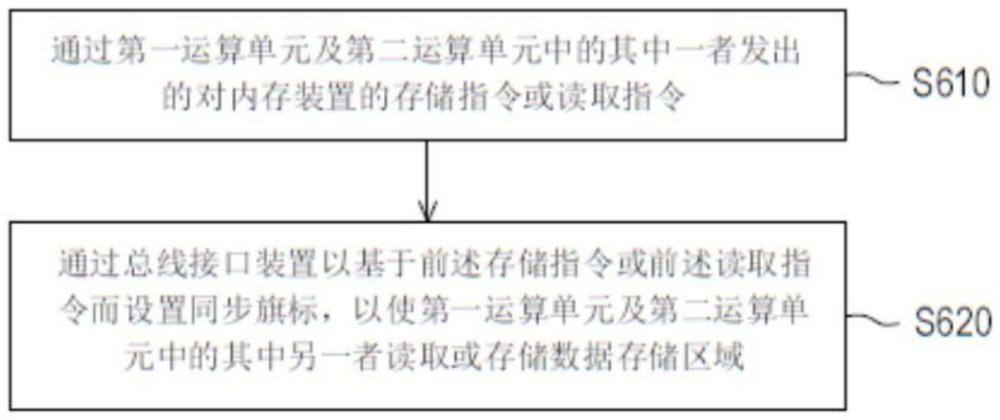

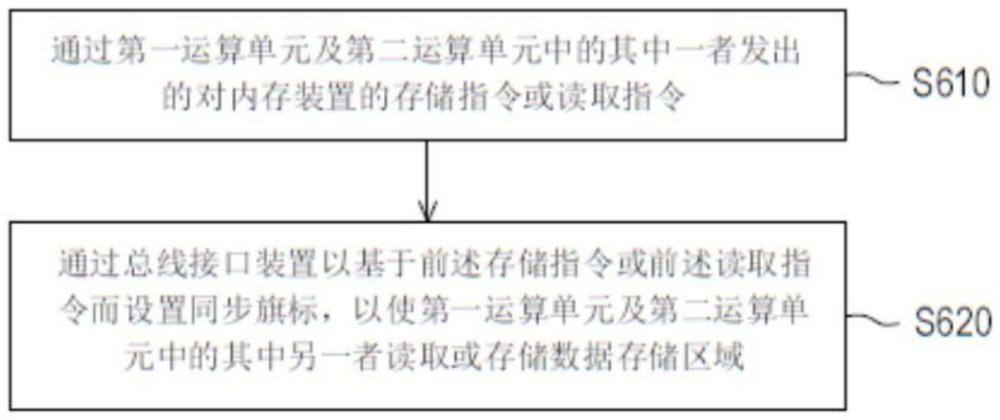

3、根据本发明的实施例,数据存取同步方法包括:通过第一运算单元及第二运算单元中的其中一者发出的对内存装置的存储指令或读取指令,其中所述第一运算单元耦接所述总线,所述第二运算单元通过第二总线接口装置耦接所述总线,所述内存装置通过所述第二总线接口装置耦接所述总线,且所述内存装置包括数据存储区域及对应于所述数据存储区域的同步旗标;以及,通过所述第二总线接口装置以基于所述存储指令或所述读取指令而设置所述同步旗标,以使所述第一运算单元及所述第二运算单元中的其中另一者读取或存储所述数据存储区域。

4、基于上述,本发明实施例所述的运算装置及数据存取同步方法,通过由第二总线接口装置负责同步旗标的设置,以降低缓存就绪与数据就绪所耗费的时间开销。并且,本发明实施例将缓存同步操作与数据同步操作相互融合为一种同步操作,此同步操作仅具备数据地址,且由第二总线接口装置通过地址偏移来获得与前述数据地址相对应的同步旗标的旗标地址,以减少缓存就绪与数据就绪的同步操作中生产者及消费者间的来回同步,降低时间开销以外,又能够符合常规的总线协议。

技术特征:1.一种运算装置,其特征在于,包括:

2.根据权利要求1所述的运算装置,其特征在于,

3.根据权利要求2所述的运算装置,其特征在于,所述旗标基础地址设置于所述运算装置的寄存器。

4.根据权利要求1所述的运算装置,其特征在于,所述第一运算单元及所述第二运算单元是两个线程、两个计算核、两个人工智能处理器、两个人工智能板卡、两个计算机或是两个人工智能板卡集群。

5.根据权利要求1所述的运算装置,其特征在于,

6.根据权利要求1所述的运算装置,其特征在于,

7.一种数据存取同步方法,其特征在于,包括:

8.根据权利要求7所述的数据存取同步方法,其特征在于,

9.根据权利要求7所述的数据存取同步方法,其特征在于,

10.根据权利要求7所述的数据存取同步方法,其特征在于,

技术总结本发明提供一种运算装置及数据存取同步方法。运算装置包括第一运算单元、第二运算单元、总线、总线接口装置以及内存装置。第一运算单元耦接总线。第二运算单元及内存装置通过总线接口装置耦接总线。内存装置包括数据存储区域及同步旗标。总线接口装置基于第一运算单元及第二运算单元中的其中一者所发出的对内存装置的存储指令或读取指令而设置同步旗标,以使第一运算单元及第二运算单元中的其中另一者读取或存储数据存储区域。本发明运算装置及数据存取同步方法通过由总线接口装置负责同步旗标的设置,可降低缓存就绪与数据就绪所耗费的时间开销。

技术研发人员:请求不公布姓名,请求不公布姓名,请求不公布姓名

受保护的技术使用者:上海壁仞科技股份有限公司

技术研发日:技术公布日:2024/11/4