缓存访问装置、协处理器、异构计算系统、以及缓存访问方法与流程

本发明实施例涉及计算机,尤其涉及一种缓存访问装置、协处理器、异构计算系统、以及缓存访问方法。

背景技术:

1、随着人工智能的迅速发展,诸如chat gpt,llama等语言类大模型对于底层芯片的算力需求越来越大。对于目前的主流gpu/ai芯片,ddr(double data rate dram,双倍数据速率同步动态随机存取内存)/hbm(high bandwidth memory,高带宽存储)的访问带宽是整个芯片的性能设计瓶颈。同时,随着gpu/ai芯片的发展,诸如cpu的主处理器和诸如gpu的协处理器之间的数据交互需求也日益增长。

2、在主处理器与协处理器之间交互的数据量比较小的时候,主处理器与协处理器之间具有共享内存空间,主处理器与协处理器可以不通过各自的缓存来访问共享内存空间(即,非缓存访问)来避免缓存数据一致性问题。

3、如果将主处理器与协处理器之间的非缓存访问变更为缓存访问,则可以提升主处理器与协处理器之间数据交互的效率,同时也会导致缓存数据一致性的问题。

技术实现思路

1、有鉴于此,本发明实施例提供一种缓存访问装置、协处理器、异构计算系统、以及缓存访问方法,以解决上述问题。

2、根据本发明实施例的第一方面,提供了一种缓存访问装置,包括:第一缓存管理单元,根据协处理器发起的缓存请求中的目标内存地址,查询第一缓存管理表,得到所述目标内存地址对应的第一缓存状态,其中,所述第一缓存管理表指示内存空间的每个内存地址范围在所述主处理器中的第一缓存空间是否存在缓存数据的第一缓存状态;第二缓存管理单元,如果所述第一缓存状态指示所述第一缓存空间中不存在缓存数据,则所述第二缓存管理单元根据所述协处理器发起的缓存请求,查找第二缓存管理表,得到所述目标内存地址与所述协处理器对应的缓存行的第二缓存状态,其中,所述第二缓存管理表指示不同内存地址在所述协处理器中的多个第二缓存空间中是否存在缓存数据的第二缓存状态;缓存访问执行单元,根据所述第二缓存状态执行所述缓存请求的访问。

3、在本发明的另一实现方式中,所述缓存访问装置还包括队列管理单元,所述队列管理单元管理针对目标内存地址的缓存请求队列,将所述目标内存地址对应的缓存状态指示存在所述缓存数据的处理器发起的缓存请求确定为从缓存请求队列中优先出队。

4、在本发明的另一实现方式中,所述队列管理单元具体用于:如果所述第一缓存状态指示所述第一缓存空间中存在缓存数据,则将所述缓存请求队列中所述主处理器发起的缓存请求确定为优先出队;如果所述第二缓存状态指示对应的第二缓存空间中存在缓存数据,则将所述缓存请求队列中所述协处理器发起的缓存请求确定为优先出队。

5、在本发明的另一实现方式中,所述第一缓存管理表包括多个比特位,每个比特位指示不同的内存地址范围,每个比特位的比特值指示该比特位对应的内存地址范围的第一缓存状态。

6、在本发明的另一实现方式中,所述第二缓存管理表包括多个缓存行,每个缓存行的缓存属性至少包括该缓存行的缓存数据所对应的内存地址范围、以及该缓存行在对应的第二缓存空间是否存在所述缓存数据的第二缓存状态。

7、在本发明的另一实现方式中,所述第二缓存状态包括该缓存行的命中状态、以及该缓存行的缓存数据的可用状态。所述缓存访问执行单元具体用于:如果该缓存行的命中状态指示命中,且该缓存行的缓存数据的可用状态指示可用,则针对该缓存行执行所述缓存请求的访问;如果该缓存行的命中状态指示未命中,则针对所述目标内存地址执行所述缓存请求的访问;如果该缓存行的命中状态指示命中,且该缓存行的缓存数据的可用状态指示不可用,则暂停执行所述缓存请求的访问,直到该缓存行的缓存数据的可用状态指示可用。

8、在本发明的另一实现方式中,所述第一缓存管理单元还用于:如果所述第一缓存状态指示所述第一缓存空间中存在缓存数据,则向所述主处理器发送第一刷新请求,并且变更所述目标内存地址所在的内存地址范围的第一缓存状态,其中,所述第一刷新请求用于对所述目标内存地址所在的内存地址范围在所述第一缓存空间的缓存数据刷新到内存地址范围中。

9、在本发明的另一实现方式中,所述第一缓存管理单元还用于:根据所述主处理器发起的缓存请求的目标内存地址,查询所述第一缓存管理表,得到所述目标内存地址对应的第一缓存状态;如果所述第一缓存状态指示所述第一缓存空间中存在缓存数据,则所述缓存访问执行单元针对所述目标内存地址在内存空间中的数据,执行所述主处理器发起的缓存请求。

10、在本发明的另一实现方式中,所述第二缓存管理单元还用于:如果所述第一缓存状态指示所述第一缓存空间中不存在缓存数据,则判断所述第二缓存状态是否指示对应的第二缓存空间中存在缓存数据;如果为是,则所述缓存访问执行单元针对所述协处理器的第二缓存空间执行所述主处理器发起的缓存请求。

11、根据本发明实施例的第二方面,提供了一种协处理器,包括:多个处理单元,每个处理单元包括:运算单元,发起缓存请求;根据第一方面所述的缓存访问装置。

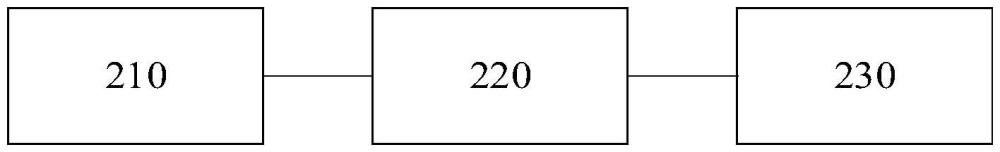

12、根据本发明实施例的第三方面,提供了一种异构计算系统,包括:主处理器;根据第二方面所述的协处理器;互联总线,连接在所述主处理器与所述协处理器之间。

13、根据本发明实施例的第四方面,提供了一种缓存访问方法,包括:根据协处理器发起的缓存请求中的目标内存地址,查询第一缓存管理表,得到所述目标内存地址对应的第一缓存状态,其中,所述第一缓存管理表指示内存空间的每个内存地址范围在所述主处理器中的第一缓存空间是否存在缓存数据的第一缓存状态;如果所述第一缓存状态指示所述第一缓存空间中不存在缓存数据,则所述第二缓存管理单元根据所述协处理器发起的缓存请求,查找第二缓存管理表,得到所述目标内存地址与所述协处理器对应的缓存行的第二缓存状态,其中,所述第二缓存管理表指示不同内存地址在所述协处理器中的多个第二缓存空间中是否存在缓存数据的第二缓存状态;根据所述第二缓存状态执行所述缓存请求的访问。

14、在本发明实施例的方案中,第一缓存管理单元通过第一缓存管理表实现了主处理器的第一缓存空间与协处理器之间的多个第二缓存空间进行一致性管理,将第一缓存空间与第二缓存空间解耦,另外,第二缓存管理单元通过第二缓存管理表实现了协处理器的多个第二缓存空间进行一致性管理,实现了多个第二缓存空间之间的解耦,因此,在包括主处理器和协处理器构成的异构计算系统中,在保持数据交互效率的同时提升了缓存数据一致性。

技术特征:

1.一种缓存访问装置,包括:

2.根据权利要求1所述的缓存访问装置,其中,所述缓存访问装置还包括队列管理单元,所述队列管理单元管理针对目标内存地址的缓存请求队列,将所述目标内存地址对应的缓存状态指示存在所述缓存数据的处理器发起的缓存请求确定为从缓存请求队列中优先出队。

3.根据权利要求2所述的缓存访问装置,其中,所述队列管理单元具体用于:

4.根据权利要求1所述的缓存访问装置,其中,所述第一缓存管理表包括多个比特位,每个比特位指示不同的内存地址范围,每个比特位的比特值指示该比特位对应的内存地址范围的第一缓存状态。

5.根据权利要求1所述的缓存访问装置,其中,所述第二缓存管理表包括多个缓存行,每个缓存行的缓存属性至少包括该缓存行的缓存数据所对应的内存地址范围、以及该缓存行在对应的第二缓存空间是否存在所述缓存数据的第二缓存状态。

6.根据权利要求5所述的缓存访问装置,其中,所述第二缓存状态包括该缓存行的命中状态、以及该缓存行的缓存数据的可用状态;

7.根据权利要求1所述的缓存访问装置,其中,所述第一缓存管理单元还用于:

8.根据权利要求1所述的缓存访问装置,其中,所述第一缓存管理单元还用于:

9.根据权利要求1所述的缓存访问装置,其中,所述第二缓存管理单元还用于:

10.一种协处理器,包括:

11.一种异构计算系统,包括:

12.一种缓存访问方法,包括:

技术总结

本发明实施例提供了一种缓存访问装置、协处理器、异构计算系统、以及缓存访问方法。所述缓存访问装置包括:第一缓存管理单元,根据协处理器发起的缓存请求,查询第一缓存管理表,得到第一缓存状态,第一缓存管理表指示内存空间的每个内存地址范围在主处理器中的第一缓存空间是否存在缓存数据的第一缓存状态;第二缓存管理单元,如果第一缓存状态指示第一缓存空间中不存在缓存数据,则第二缓存管理单元根据协处理器发起的缓存请求,查找第二缓存管理表,得到第二缓存状态,第二缓存管理表指示不同内存地址在协处理器中的多个第二缓存空间中是否存在缓存数据的第二缓存状态;缓存访问执行单元,根据第二缓存状态执行缓存请求的访问。

技术研发人员:李寅,朱韵鹏,陈洁君,杜汉平,涂家铭

受保护的技术使用者:平头哥(上海)半导体技术有限公司

技术研发日:

技术公布日:2024/12/26

- 还没有人留言评论。精彩留言会获得点赞!