一种大规模集成电路版图密度检查并行处理方法与流程

本发明属于集成电路计算机辅助设计,涉及一种大规模集成电路版图密度检查并行处理方法。

背景技术:

1、近30年来,集成电路技术一直按照“摩尔定律”向前发展。芯片的特征尺寸越来越小,单个芯片的集成度也越来越高。随着芯片规模的扩大,在集成电路设计的各个阶段所需验证的设计规则也在不断增。其中集成电路版图的设计规则检查(drc)变得越来越重要,它们对于消除错误、降低设计成本和减少设计失败的风险具有重要作用。在超大规模集成电路设计中,版图规模急剧膨胀,如何在有效时间内完成设计方案的验证工作成为各大eda厂商急需解决的问题。

2、密度检查是规则检查中的重要一项。密度检查需要进行窗口的移动,对于大规模继承电路版图,是一个非常耗时的操作。减少密度检查的耗时,可以显著的提高设计方案的验证工作的效率。

3、线程是并发处理的关键技术之一。使用线程可以更好的利用cpu的资源,如果只有一个线程,则第二个任务必须等到第一个任务结束后才能进行,如果使用线程则在主线程执行任务的同时可以执行其他任务,而不需要等待;线程中间可以共享数据,方便业务的处理;系统创建进程需要为该进程重新分配系统资源,创建线程代价比较小。

4、大规模集成电路版图检测中的密度检测耗时时间长,影响版图检测工作,导致了版图验证最终不可解的问题。

技术实现思路

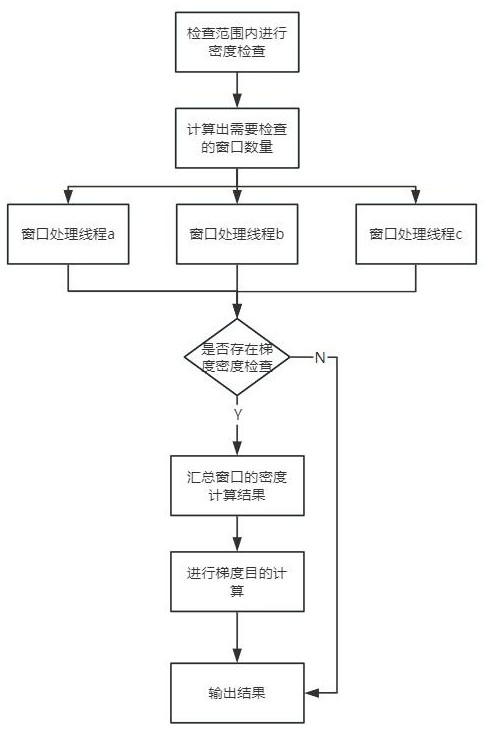

1、本发明为了弥补现有技术的不足,提供了一种大规模集成电路版图密度检查并行处理方法,实现了加速版图中密度检查的运行速度,提高了可验证版图规模。本发明是通过如下技术方案实现的:本发明提供了一种大规模集成电路版图密度检查并行处理方法;包括检查范围并发处理:密度检查可能存在多个检查范围,如果存在多个检查范围,使用多线程并发检查,最后汇总所有检查范围的输出结果,作为密度检查的结果;具体步骤为:

2、(1) 集成电路版图的设计规则检查软件drc中,根据密度校验的规则和集成电路数据,获得检查范围;

3、(2) 如果存在多个检查范围,则使用线程进行并发处理:开启线程池,将检查范围平均分配到不同的线程中进行处理;

4、(3) 每个线程只处理被分配到的搜索范围,并做如下处理;

5、a)按照检查规则的参数,将检查范围划分成窗口;

6、b)遍历处理每个窗口,计算出窗口中的密度表达式的结果,保存密度表达式结果,并校验密度表达式结果是否满足密度约束条件;

7、(4) 全部线程处理完成后,获得全部窗口中的密度值、是否满足密度约束条件;

8、(5) 如果规则中要求进行密度梯度检查,则通过相邻窗口之间的密度,计算出密度梯度,并校验密度梯度是否满足密度梯度约束条件;

9、(6) 遍历窗口的检查结果,输出同时满足密度约束条件和密度梯度约束条件的窗口;

10、一个检查范围可能包含大量的窗口;在检查范围的处理中,并发处理窗口;具体步骤为;

11、(1) 根据检查范围、窗口的大小、窗口的移动步长、边缘处理方式划分出窗口;

12、(2) 将窗口平均分配到线程中,每个线程中处理分配给本线程的窗口;

13、(3) 每个窗口处理中,计算出密度表达式的结果,判断是否符合密度约束条件,并记录密度表达式结果和密度约束条件校验结果。

14、本发明的有益效果是:

15、本发明基于检查范围并发和检查窗口并发的方式,使用线程池,同时对检查范围和检查范围内的窗口进行并发处理,提高密度检查的效率,来解决大规模集成电路版图验证过程中面临检查耗时过长,验证效率低的问题。实际应用中表明,该并行处理方案能够在用户可接受的时间内解决超大规模版图进行密度检查的问题。

16、本发明使用线程池,同时并发处理检查范围和窗口,使得密度检查效率最大化。

技术特征:

1.一种大规模集成电路版图密度检查并行处理方法,其特征在于:包括检查范围并发处理:密度检查可能存在多个检查范围,如果存在多个检查范围,使用多线程并发检查,最后汇总所有检查范围的输出结果,作为密度检查的结果;具体步骤为:

2.根据权利要求1所述的大规模集成电路版图密度检查并行处理方法,其特征在于,密度检查规则中检查范围的设置主要包括以下情况:

3.根据权利要求1所述的大规模集成电路版图密度检查并行处理方法,其特征在于,所有窗口处理完成后,如果密度检查规则中要求检查密度梯度,则进行密度梯度检查;密度梯度检查需要计算窗口和相邻窗口之间的最大密度差,然后和密度梯度约束条件进行校验,并将校验结果保存到窗口中。

4.根据权利要求1所述的大规模集成电路版图密度检查并行处理方法,其特征在于,窗口设置规则包括:

5.根据权利要求1所述的大规模集成电路版图密度检查并行处理方法,其特征在于,密度检查包含以下流程:

技术总结

本发明公开了一种大规模集成电路版图密度检查并行处理方法,所属的技术领域是集成电路计算机辅助设计领域,尤其是涉及集成电路版图的设计规则检查(DRC)和版图与原理图的一致性检查(LVS)领域。本发明创造性地提出了基于检查范围和窗口并行法,用于解决大规模集成电路版图验证过程中面临检查耗时过长,验证效率低的问题。实际应用中表明,该并行处理方案能够在用户可接受的时间内解决超大规模版图进行密度检查的问题。

技术研发人员:解志阳,李庆昌

受保护的技术使用者:济南日观科技有限公司

技术研发日:

技术公布日:2024/9/23

- 还没有人留言评论。精彩留言会获得点赞!