用于分析逻辑系统设计的时序的方法及相关设备与流程

本申请涉及芯片验证,尤其涉及一种用于分析逻辑系统设计的时序的方法及相关设备。

背景技术:

1、硬件仿真工具(例如,可编程逻辑器件或硬件仿真器(emulator))可以原型化(prototype)并且调试一个包括一个或多个模块的逻辑系统设计。所述逻辑系统设计可以是,例如,用于供专门应用的集成电路(application specific integrated circuit,简称asic)或者片上系统芯片(system-on-chip,简称soc)的设计。因此,在仿真工具中被测试的逻辑系统设计又可以称为待测设计(design under test,简称dut)。仿真工具可以通过一个或多个可配置组件(例如,现场可编程逻辑门阵列(field programmable gate array,简称fpga))来仿真该待测设计,包括执行该待测设计的各种操作,从而在制造之前就测试并验证待测设计的各个模块的功能。通过在仿真工具上外接多种外设子卡还可以测试待测设计与各种外设作为一个完整系统进行运行的效果。

2、当使用了多个可编程逻辑器件来仿真待测设计时,静态时序分析是必要的设计步骤,以便于准确估算各个可编程逻辑器件内的延迟和各个可编程逻辑器件之间的延迟。然而,静态时序分析工具可以用于分析可编程逻辑器件内的延迟,但无法对各个可编程逻辑器件之间的延迟进行分析。

技术实现思路

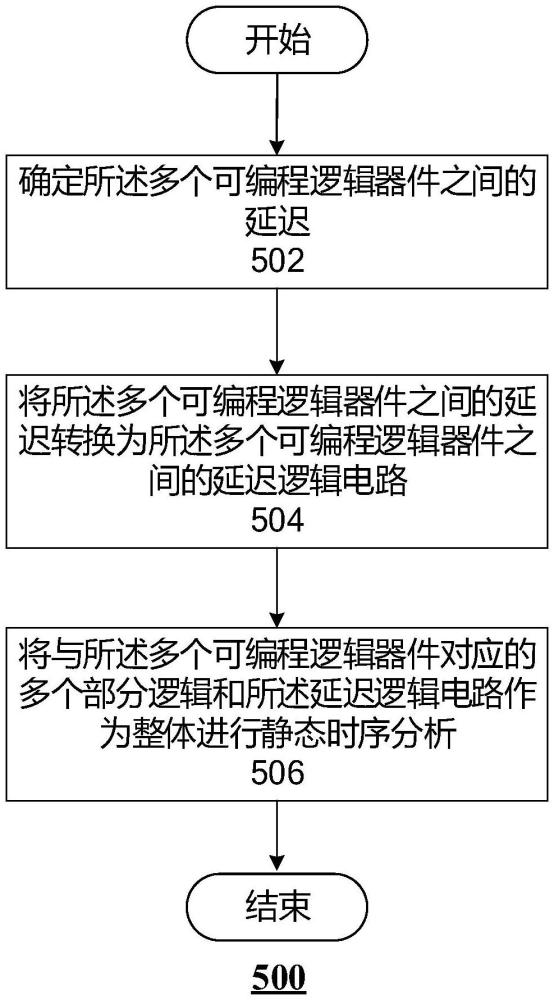

1、本申请的第一方面提供一种用于分析逻辑系统设计的时序的方法,所述逻辑系统设计在硬件仿真工具上实现,所述硬件仿真工具包括多个可编程逻辑器件,所述多个可编程逻辑器件分别包括所述逻辑系统设计的多个部分逻辑,所述方法包括:确定所述多个可编程逻辑器件之间的延迟;将所述多个可编程逻辑器件之间的延迟转换为所述多个可编程逻辑器件之间的延迟逻辑电路;将与所述多个可编程逻辑器件对应的多个部分逻辑和所述延迟逻辑电路作为整体进行静态时序分析。

2、本申请的第二方面提供一种电子设备,包括:存储器,用于存储一组指令;以及至少一个处理器,配置为执行所述一组指令以使得所述电子设备执行如第一方面所述的方法。

3、本申请的第三方面提供一种非暂态计算机可读存储介质,所述非暂态计算机可读存储介质存储计算机的一组指令,该组指令用于在被执行时使所述计算机执行如第一方面所述的方法。

4、本申请提供的一种用于分析逻辑系统设计的时序的方法及相关设备,通过将多个可编程逻辑器件之间的延迟转换为多个可编程逻辑器件之间的延迟逻辑电路,并将与多个可编程逻辑器件对应的多个部分逻辑和延迟逻辑电路作为整体进行静态时序分析,从而解决了无法对各个可编程逻辑器件之间的延迟进行分析的问题,进而实现了对整个逻辑系统设计的时序分析。

技术特征:

1.一种用于分析逻辑系统设计的时序的方法,所述逻辑系统设计在硬件仿真工具上实现,所述硬件仿真工具包括多个可编程逻辑器件,所述多个可编程逻辑器件分别包括所述逻辑系统设计的多个部分逻辑,所述方法包括:

2.如权利要求1所述的方法,其中,所述确定所述多个可编程逻辑器件之间的延迟进一步包括:

3.如权利要求1所述的方法,进一步包括:

4.如权利要求1所述的方法,其中,所述将与所述多个可编程逻辑器件对应的多个部分逻辑和所述延迟逻辑电路作为整体进行静态时序分析进一步包括:

5.如权利要求2所述的方法,其中,所述线缆延迟包括所述线缆的延迟和所述线缆连接的两个可编程逻辑器件的接口的延迟。

6.如权利要求1所述的方法,其中,所述将所述多个可编程逻辑器件之间的延迟转换为所述多个可编程逻辑器件之间的延迟逻辑电路进一步包括:

7.如权利要求6所述的方法,进一步包括:

8.如权利要求7所述的方法,其中,所述将与所述多个可编程逻辑器件对应的多个部分逻辑和所述延迟逻辑电路作为整体进行静态时序分析进一步包括:

9.一种电子设备,包括:

10.一种非暂态计算机可读存储介质,所述非暂态计算机可读存储介质存储计算机的一组指令,该组指令用于在被执行时使所述计算机执行如权利要求1至8的任一项所述的方法。

技术总结

本申请提供一种用于分析逻辑系统设计的时序的方法及相关设备,通过将多个可编程逻辑器件之间的延迟转换为多个可编程逻辑器件之间的延迟逻辑电路,并将与多个可编程逻辑器件对应的多个部分逻辑和延迟逻辑电路作为整体进行静态时序分析,从而解决了无法对各个可编程逻辑器件之间的延迟进行分析的问题,进而实现了对整个逻辑系统设计的时序分析。

技术研发人员:瞿亿帆,张赛,苏成清

受保护的技术使用者:芯华章科技股份有限公司

技术研发日:

技术公布日:2024/12/23

- 还没有人留言评论。精彩留言会获得点赞!