内存访存控制方法、装置和设备与流程

本发明涉及计算机 ,尤其涉及一种内存访存控制方法、装置和设备。

背景技术:

1、内存的层次架构特点决定了内存控制器对物理地址的分时复用行为。也就是内存控制器依据物理地址,依次寻址bank group、bank、row及column。由于行(row)地址处于相对地位,连续的读写操作之后,地址信号优先低位跳转,数据优先分布于同一bank group或同一bank中。也就是说系统需要对同一bank的不同行频繁的进行读写访问。由内存的时序特点可知,这将导致内存需要重复执行激活及预充电命令,增大延迟。

2、相关技术针对内存时序特点优化了地址映射机制,减小了读写过程中的冗余操作,提高了访存速度。但内存连续读写过程中访存地址的调度同样会影响访存速度,因此如何针对访存调度机制进行改进,以减小延迟,提升访存速度,是本领域技术人员亟需解决的技术问题。

技术实现思路

1、本发明提供一种内存访存控制方法、装置和设备,用以解决现有技术中内存访存时延较高的问题。

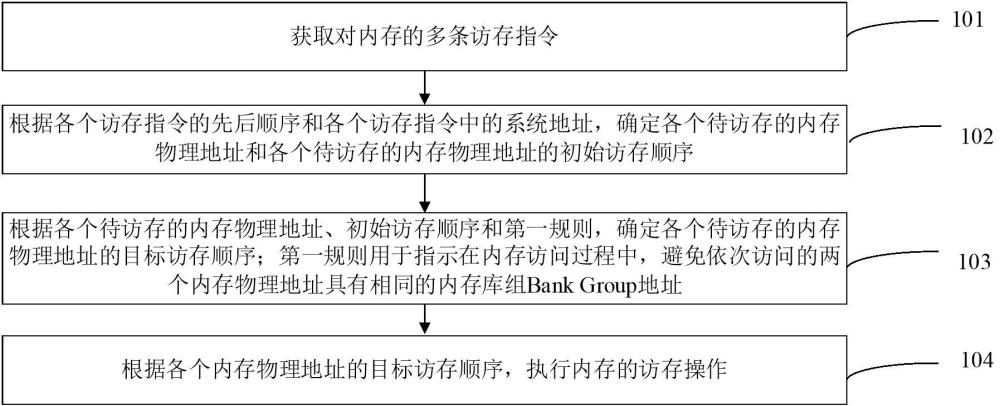

2、本发明提供一种内存访存控制方法,包括如下步骤。

3、获取对内存的多条访存指令;

4、根据各个访存指令的先后顺序和各个访存指令中的系统地址,确定各个待访存的内存物理地址和各个待访存的内存物理地址的初始访存顺序;

5、根据各个待访存的内存物理地址、初始访存顺序和第一规则,确定各个待访存的内存物理地址的目标访存顺序;第一规则用于指示在内存访问过程中,避免依次访问的两个内存物理地址具有相同的内存库组bank group地址;

6、根据各个内存物理地址的目标访存顺序,执行内存的访存操作。

7、根据本发明提供的一种内存访存控制方法,所述根据各个访存指令的先后顺序和各个访存指令中的系统地址,确定各个待访存的内存物理地址和各个待访存的内存物理地址的初始访存顺序,包括:

8、根据各个访存指令的先后顺序,确定各个访存指令中的系统地址所对应的内存物理地址的访存顺序。

9、根据本发明提供的一种内存访存控制方法,所述根据各个待访存的内存物理地址、各个待访存的内存物理地址的初始访存顺序和第一规则,确定各个待访存的内存物理地址的目标访存顺序,包括:

10、根据各个待访存的内存物理地址的初始访存顺序、第一内存物理地址和第一规则,确定第二内存物理地址;第一内存物理地址为当前访存的内存物理地址;第二内存物理地址为第一访存物理地址执行访存操作之后,需进行访存操作的内存物理地址;第二内存物理地址与第一内存物理地址对应不同的bank group地址;

11、根据第二内存物理地址、各个待访存的内存物理地址的初始访存顺序和第一规则,确定剩余的待访存的内存物理地址的访问顺序。

12、根据本发明提供的一种内存访存控制方法,所述根据各个待访存的内存物理地址的初始访存顺序、第一内存物理地址和第一规则,确定第二内存物理地址,包括:

13、根据各个待访存的内存物理地址的初始访存顺序和第一内存物理地址,确定第二候选内存物理地址;第二候选内存物理地址为初始访存顺序中第一内存物理地址之后相邻的待执行访问操作的内存物理地址;

14、根据第二候选内存物理地址对应的bank group地址与第一内存物理地址对应的bank group地址,确定第二内存物理地址。

15、根据本发明提供的一种内存访存控制方法,所述根据第二候选内存物理地址对应的bank group地址与第一内存物理地址对应的bank group地址,确定第二内存物理地址,包括:

16、在第二候选内存物理地址与第一内存物理地址对应不同的bank group地址的情况下,则将第二候选内存物理地址,确定为第二内存物理地址;

17、在第二候选内存物理地址与第一内存物理地址对应相同的bank group地址的情况下,则根据初始访存顺序和第一规则,从第二候选内存物理地址之外的内存物理地址中确定第二内存物理地址。

18、根据本发明提供的一种内存访存控制方法,还包括:确定待访存的内存物理地址对应的访存任务的等待时长;若待访存的内存物理地址对应的访存任务的等待时长大于预设值,则更新待访存的内存物理地址对应的访存任务的执行顺序。

19、本发明还提供一种内存访存控制装置,包括如下模块:

20、获取模块,用于获取对内存的多条访存指令;

21、第一确定模块,用于根据各个访存指令的先后顺序和各个访存指令中的系统地址,确定各个待访存的内存物理地址和各个待访存的内存物理地址的初始访存顺序;

22、第二确定模块,用于根据各个待访存的内存物理地址、初始访存顺序和第一规则,确定各个待访存的内存物理地址的目标访存顺序;第一规则用于指示在内存访问过程中,避免依次访问的两个内存物理地址具有相同的内存库组bank group地址;

23、访存模块,用于根据各个内存物理地址的目标访存顺序,执行内存的访存操作。

24、本发明还提供一种电子设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现如上述任一种所述内存访存控制方法。

25、本发明还提供一种非暂态计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现如上述任一种所述内存访存控制方法。

26、本发明还提供一种计算机程序产品,包括计算机程序,所述计算机程序被处理器执行时实现如上述任一种所述内存访存控制方法。

27、本发明提供的内存访存控制方法、装置和设备,根据第一规则,对内存物理地址的初始访存顺序进行调整,得到各个内存物理地址的目标访存顺序;也就是通过对内存物理地址访问顺序的调整和优化,实现了将原本的两次相同bank group的连续访存变成两次不同bank group访存,避免了依次访问的两个内存物理地址具有相同的内存库组bank group地址,从而有效地降低了内存访问时延,提高了内存数据的存取速率。

技术特征:

1.一种内存访存控制方法,其特征在于,包括:

2.根据权利要求1所述的内存访存控制方法,其特征在于,所述根据各个所述访存指令的先后顺序和各个所述访存指令中的系统地址,确定各个待访存的内存物理地址和各个待访存的内存物理地址的初始访存顺序,包括:

3.根据权利要求1所述的内存访存控制方法,其特征在于,所述根据各个所述待访存的内存物理地址、各个所述待访存的内存物理地址的初始访存顺序和第一规则,确定各个待访存的内存物理地址的目标访存顺序,包括:

4.根据权利要求3所述的内存访存控制方法,其特征在于,所述根据各个所述待访存的内存物理地址的初始访存顺序、第一内存物理地址和第一规则,确定第二内存物理地址,包括:

5.根据权利要求4所述的内存访存控制方法,其特征在于,所述根据所述第二候选内存物理地址对应的bank group地址与所述第一内存物理地址对应的bank group地址,确定所述第二内存物理地址,包括:

6.根据权利要求3-5任一项所述的内存访存控制方法,其特征在于,所述根据各个所述待访存的内存物理地址、各个所述待访存的内存物理地址的初始访存顺序和第一规则,确定各个待访存的内存物理地址的目标访存顺序之后,还包括:

7.一种内存访存控制装置,其特征在于,包括:

8.一种电子设备,包括存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,其特征在于,所述处理器执行所述程序时实现如权利要求1至6任一项所述内存访存控制方法。

9.一种非暂态计算机可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现如权利要求1至6任一项所述内存访存控制方法。

10.一种计算机程序产品,包括计算机程序,其特征在于,所述计算机程序被处理器执行时实现如权利要求1至6任一项所述内存访存控制方法。

技术总结

本发明提供一种内存访存控制方法、装置和设备,该方法包括:获取对内存的多条访存指令;根据各个访存指令的先后顺序和各个访存指令中的系统地址,确定各个待访存的内存物理地址和各个待访存的内存物理地址的初始访存顺序;根据各个待访存的内存物理地址、初始访存顺序和第一规则,确定各个待访存的内存物理地址的目标访存顺序;第一规则用于指示在内存访问过程中,避免依次访问的两个内存物理地址具有相同的内存库组Bank Group地址;根据各个内存物理地址的目标访存顺序,执行内存的访存操作。本申请实施例的方法降低了内存访问时延,提高了内存数据的存取速率。

技术研发人员:林方成,贾钦茹,周二龙

受保护的技术使用者:山东云海国创云计算装备产业创新中心有限公司

技术研发日:

技术公布日:2024/12/2

- 还没有人留言评论。精彩留言会获得点赞!