PCIeMSIX中断生成方法与流程

本发明涉及通信领域,具体涉及一种pcie msix中断生成方法。

背景技术:

1、计算机系统硬件架构的核心组成部分是系统总线,它负责将处理器、主存储器以及外围设备连接在一起,以实现数据、控制和状态信息的传输。系统总线的发展经历了从第一代和第二代的并行总线到现今的第三代串行总线,即外围组件快速互联总线(peripheral component interconnect express,pcie)。

2、pcie主要用于将计算机与各种外部高速设备相连,例如网卡、显卡、硬盘和通用串行总线(universal serial bus,usb)主机控制器等,均可通过pcie与计算机的中央处理器相连。

3、随着用户需求的不断增长,为了提升中央处理器对pcie事件的响应速度,pcie引入了中断机制。最初采用的是传统的中断请求(interrupt request,intx)中断机制,但由于intx需要占用专门的中断引脚,且对于多功能的pcie设备,每个功能最多仅有一个中断引脚,因此在具体事件发生时,驱动程序需要查询设备才能确定哪个事件被触发,这降低了中断处理的效率。因此,传统的intx中断机制已被消息信号中断(message signalinterrupt,msi)所取代。

4、然而,msi也存在一些局限性:首先,msi机制仅允许每个pcie function拥有最多32个中断向量,对于某些应用场景来说可能不足够;其次,msi机制下,每个pcie function的所有中断向量共享一个消息地址,无法将其分配到不同的中央处理器以实现中断服务在中央处理器间的均衡分配;最后,在msi机制下,所有pcie function的中断向量都是连续的,无法满足区分中断优先级的需求。

5、为了解决这些问题,消息信号中断扩展(message signaled interrupt express,msix)中断机制应运而生。msix支持高达2048个中断向量,每个中断向量对应的消息和地址存储在专门的msix 表中,每个中断向量与msix表中的一个条目相对应。

6、尽管msix支持高达2048个中断向量,但当大量中断同时触发时,pcie知识产权(intellectual property,ip)核中msix模块可能无法同时发送如此多的msix中断消息,从而导致部分中断丢失,这可能会影响pcie设备的性能甚至导致功能异常。

7、在含有pcie接口的pcie芯片或pcie设备中,会有专门的pcie ip核来处理pcie的通信事务,并设有专门的msix中断接口用于接收应用层发送的中断请求。msix中断接口每次只能接收一个中断请求,而应用层可以发送多达2048个中断请求,大量的中断请求可能导致中断请求丢失问题。

8、换言之,现有技术中直接将中断信号连接到中断处理模块,当多个中断消息同时触发时,存在因来不及响应而丢失中断消息的风险。

9、本发明提供一种pcie msix中断生成方法,解决了多个中断向量同时触发时,导致中断消息存在丢失风险问题,提升可靠性。

技术实现思路

1、为了缓解或部分缓解上述技术问题,本发明的解决方案如下所述:

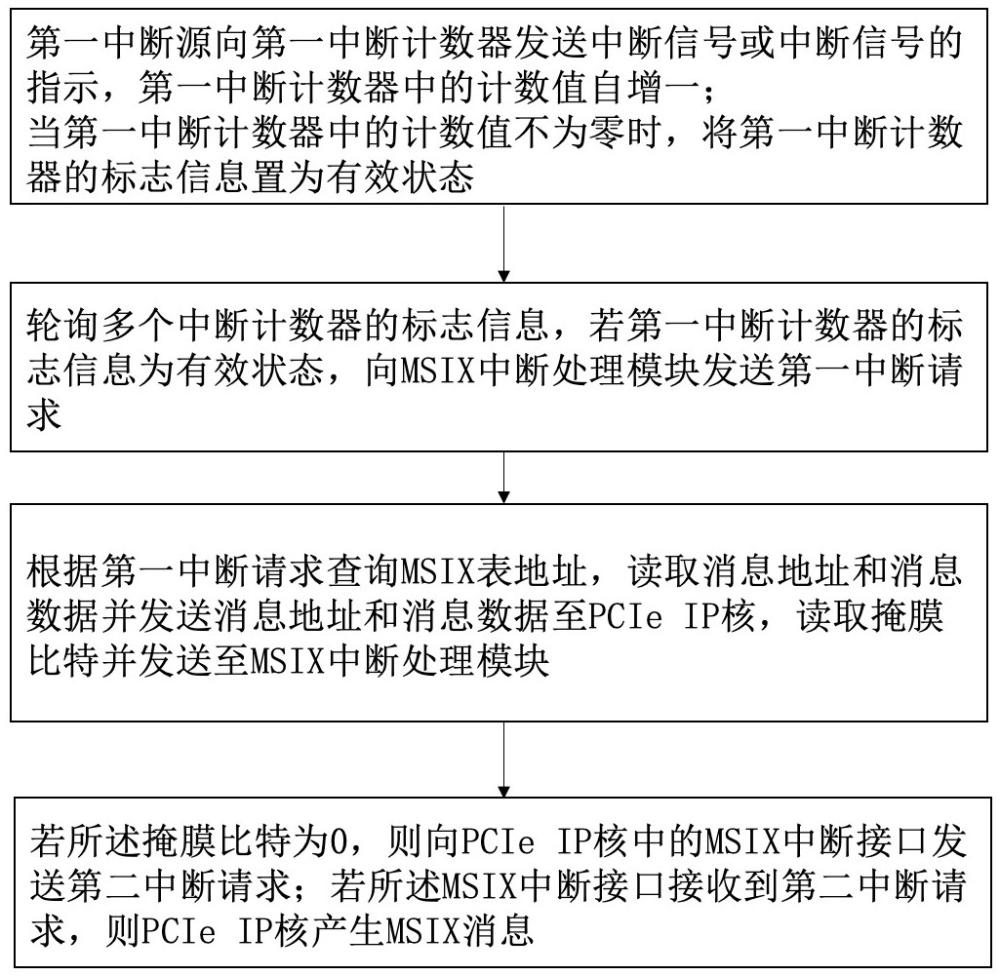

2、一种pcie msix中断生成方法,包括如下步骤:第一中断源向第一中断计数器发送中断信号或中断信号的指示,第一中断计数器中的计数值自增一;当第一中断计数器中的计数值不为零时,将第一中断计数器的标志信息置为有效状态;其中,所述第一中断源是应用层中多个中断源中的一个,第一中断计数器是多个中断计数器中的一个,且所述多个中断源和所述多个中断计数器一一对应;轮询多个中断计数器的标志信息,若第一中断计数器的标志信息为有效状态,向msix中断处理模块发送第一中断请求;根据第一中断请求查询msix表地址,读取消息地址和消息数据并发送消息地址和消息数据至pcie ip核,读取掩膜比特并发送至msix中断处理模块;若所述掩膜比特为0,则msix中断处理模块向pcie ip核中的msix中断接口发送第二中断请求;若所述msix中断接口接收到第二中断请求,则pcie ip核产生msix消息。

3、进一步地,若pcie ip核接收第二中断请求,则所述msix中断接口向所述msix中断处理模块发送第二确认信息。

4、进一步地,轮询多个中断计数器的标志信息是由中断查询与处理模块执行;所述msix中断处理模块接收到第二确认信息后,向中断查询与处理模块发送第一确认信息。

5、进一步地,中断查询与处理模块接收到第一确认信息后,则控制第一中断计数器中的计数值执行减一操作。

6、进一步地,所述掩膜比特是msix表中控制向量的一个比特。

7、进一步地,所述第一中断请求包括中断号。

8、进一步地,所述方法运行于pcie芯片之中。

9、本发明技术方案,具有如下有益的技术效果:

10、在不显著增加功耗的前提下,本发明通过插入的中断计数器暂存触发中断的信号,然后依次在msix中断接口中发送这些中断,使得msix中断接口可以同时接收大量的、同时触发的中断信号,且不会丢失这些中断信号。

11、此外,本发明还具有的其它有益效果将在具体实施例中提及。

技术特征:

1.一种pcie msix中断生成方法,其特征在于,包括如下步骤:

2.根据权利要求1所述的pcie msix中断生成方法,其特征在于:

3.根据权利要求2所述的pcie msix中断生成方法,其特征在于:

4.根据权利要求3所述的pcie msix中断生成方法,其特征在于:

5.根据权利要求4所述的pcie msix中断生成方法,其特征在于:

6.根据权利要求5所述的pcie msix中断生成方法,其特征在于:

7.根据权利要求6所述的pcie msix中断生成方法,其特征在于:

技术总结

本发明公开了一种PCIe MSIX中断生成方法。为解决中断消息存在丢失风险问题,本发明PCIe MSIX中断生成方法,包括:第一中断源向第一中断计数器发送中断信号或中断信号的指示,第一中断计数器中的计数值自增一;当第一中断计数器中的计数值不为零时,将第一中断计数器的标志信息置为有效状态;轮询多个中断计数器的标志信息,若第一中断计数器的标志信息为有效状态,向MSIX中断处理模块发送第一中断请求;根据第一中断请求查询MSIX表地址,读取消息地址和消息数据并发送消息地址和消息数据至PCIe IP核,读取掩膜比特并发送至MSIX中断处理模块;然后根据掩膜比特确定PCIe IP核产生MSIX消息。本发明中MSIX中断接口可以同时接收大量的中断信号,且不造成丢失。

技术研发人员:请求不公布姓名,请求不公布姓名,请求不公布姓名,请求不公布姓名,请求不公布姓名

受保护的技术使用者:成都电科星拓科技有限公司

技术研发日:

技术公布日:2024/9/23

- 还没有人留言评论。精彩留言会获得点赞!