一种同步FIFO的验证方法及装置与流程

本发明涉及芯片验证,且特别是有关于一种同步fifo的验证方法及装置。

背景技术:

1、fifo (first in first out)是一种用寄存器或者随机访问存储器(ram)实现的存储结构,采用先入先出的方式存储数据通道中的数据流,承担着数据缓冲和存储的功能。在芯片设计的过程中,fifo常见于芯片内部不同的模块之间,当芯片中的某个下游模块无法及时处理上游模块输出的数据时,需要用fifo暂存数据,防止数据丢失。当fifo中存满数据时,会向上游模块发起反压信号,此时上游模块会停止对下游模块发送数据,直到fifo的反压信号撤销。

2、根据fifo工作的时钟域,可以分为同步fifo和异步fifo,同步fifo的读写操作与系统时钟同步,而异步fifo具有独立的读写时钟信号,适用于跨时钟域的数据传输。

3、同步fifo通常会由信用控制,具体为,同步fifo中接收上游模块一个数据,信用值计数加一;每发送给后级模块一个数据,信用值计数减一。当信用值计数达到约定的信用上限时会产生反压信号,当信用值计数小于约定的信用上限时,反压信号撤销。对于芯片验证工作来说,主要需要验证fifo的空、满、中断三种状态,其中中断又涉及到数据上溢、数据下溢、数据校验三种场景,以下分别称为中断上溢、中断下溢、中断校验。

4、当前,基于通用验证方法学(uvm)对芯片进行验证时,如果芯片的各模块中使用多个同步fifo,需要在模块内部对每个同步fifo的空、满、中断状态依次单独验证,耗时较长且操作繁琐;尤其是在fifo数量很多时,验证耗时更长。

技术实现思路

1、本发明旨在提供一种同步fifo的验证方法及装置,将同步fifo空、满状态的检测融入到中断上下溢验证中,确保同步fifo验证工作的完备性。

2、为达到上述目的,本发明技术方案是:

3、一种同步fifo的验证方法,包括,按照命名规则对多个同步fifo进行命名;抓取所有同步fifo的名称,依次找到所有同步fifo的路径;将单个同步fifo的验证步骤封装在一个宏中,在宏内定义多个参数,使用所述宏将同步fifo的对应参数传递至宏内的各参数中,运行所述宏,依次验证所有的同步fifo。

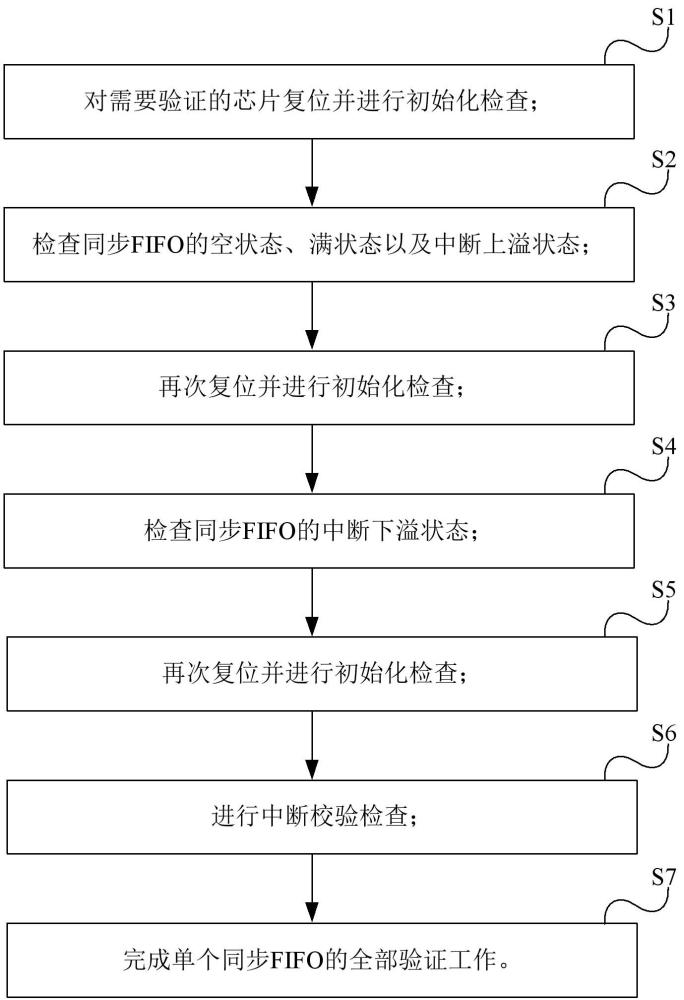

4、进一步地,单个同步fifo的验证步骤包括,

5、步骤s1,对需要验证的芯片复位并进行初始化检查;

6、步骤s2,检查同步fifo的空状态、满状态以及中断上溢状态;

7、步骤s3,再次复位并进行初始化检查;

8、步骤s4,检查同步fifo的中断下溢状态;

9、步骤s5,再次复位并进行初始化检查;

10、步骤s6,进行中断校验检查;

11、步骤s7,完成单个同步fifo的全部验证工作,结束。

12、进一步地,复位并进行初始化检查,具体为,对需要验证的芯片进行逻辑复位和配置复位,初始化内部信号和寄存器,使用后门读取对应fifo的空满状态寄存器和中断上下溢寄存器,检查fifo空信号fifo_empty是否为1,fifo上溢信号fifo_overflow、fifo下溢信号fifo_underflow是否为0,fifo计数fifo_counter是否为0。

13、进一步地,上述步骤s2包括,

14、步骤s21,输入一个数据,检查同步fifo的空状态;

15、步骤s22,再次输入n-1个数据,检查同步fifo的满状态,n为同步fifo的深度;

16、步骤s23,同时给同步fifo输入一个数据并输出一个数据,检查同步fifo是否无中断上溢状态;

17、步骤s24,再次输入一个数据,检查同步fifo是否有中断上溢状态。

18、进一步地,上述步骤s4包括,

19、步骤s41,同时给同步fifo输入一个数据并输出一个数据,检查同步fifo是否无中断下溢状态;

20、步骤s42,让同步fifo输出一个数据,检查同步fifo是否有中断下溢状态。

21、进一步地,上述步骤s6包括,

22、步骤s61,根据表项宽度对数据进行分组,计算校验数据分组数,在校验位插入错误校验数据,检查校验错误信号是否拉高;

23、步骤s62,等一拍之后,检查同步fifo有无中断校验错误状态,即校验错误信号是否能正确传递到中断校验寄存器当中;

24、步骤s63,判断校验次数是否小于校验分组数,若是,进入步骤s7;若否,返回步骤s61,校验次数加1,检验下一组数据。

25、本发明还提供一种同步fifo的验证装置,应用如上述一种同步fifo的验证方法,包括同步fifo与uvm验证环境,所述uvm验证环境连接所述同步fifo。

26、上述uvm验证环境包括数据驱动模块、数据比较模块与参考模型模块,所述数据驱动模块用于向所述同步fifo和所述参考模型模块发送数据,所述同步fifo和所述参考模型模块接收所述数据驱动模块发送的数据并进行逻辑处理,处理完的数据送入所述数据比较模块比对。

27、本发明一种同步fifo的验证方法及装置,相比于以往对每个同步fifo单独检测空、满、中断状态,将同步fifo所要验证的内容整合成一套完成的方法,提高了fifo验证效率,保证了fifo模块设计的正确性;能够解决芯片内同步fifo模块数量多,验证fifo耗时长且操作繁琐的问题,在一定程度上提升了uvm验证的工作效率,并且确保验证同步fifo的完备性。

28、为让发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附图式作详细说明如下。

技术特征:

1.一种同步fifo的验证方法,其特征在于,包括,按照命名规则对多个同步fifo进行命名;抓取所有同步fifo的名称,依次找到所有同步fifo的路径;将单个同步fifo的验证步骤封装在一个宏中,在宏内定义多个参数,使用所述宏将同步fifo的对应参数传递至宏内的各参数中,运行所述宏,依次验证所有的同步fifo。

2.如权利要求1所述一种同步fifo的验证方法,其特征在于,单个同步fifo的验证步骤包括,

3.如权利要求2所述一种同步fifo的验证方法,其特征在于,包括,复位并进行初始化检查,具体为,对需要验证的芯片进行逻辑复位和配置复位,初始化内部信号和寄存器,使用后门读取对应fifo的空满状态寄存器和中断上下溢寄存器,检查fifo空信号fifo_empty是否为1,fifo上溢信号fifo_overflow、fifo下溢信号fifo_underflow是否为0,fifo计数fifo_counter是否为0。

4.如权利要求3所述一种同步fifo的验证方法,其特征在于,所述步骤s2包括,

5.如权利要求4所述一种同步fifo的验证方法,其特征在于,所述步骤s4包括,

6.如权利要求5所述一种同步fifo的验证方法,其特征在于,所述步骤s6包括,

7.一种同步fifo的验证装置,其特征在于,应用如权利要求1-6任一项所述一种同步fifo的验证方法,包括同步fifo与uvm验证环境,所述uvm验证环境连接所述同步fifo。

8.如权利要求7所述一种同步fifo的验证装置,其特征在于,所述uvm验证环境包括数据驱动模块、数据比较模块与参考模型模块,所述数据驱动模块用于向所述同步fifo和所述参考模型模块发送数据,所述同步fifo和所述参考模型模块接收所述数据驱动模块发送的数据并进行逻辑处理,处理完的数据送入所述数据比较模块比对。

技术总结

本发明公开了一种同步FIFO的验证方法及装置,属于芯片验证技术领域,包括,按照命名规则对多个同步FIFO进行命名;抓取所有同步FIFO的名称,依次找到所有同步FIFO的路径;将单个同步FIFO的验证步骤封装在一个宏中,在宏内定义多个参数,使用所述宏将同步FIFO的对应参数传递至宏内的各参数中,运行所述宏,依次验证所有的同步FIFO。本发明将同步FIFO所要验证的内容整合成一套完成的方法,提高了FIFO验证效率,保证了FIFO模块设计的正确性。

技术研发人员:李思源,莫祖贵,朱荽,张征,杨彪,曹敬,杨清

受保护的技术使用者:成都市楠菲微电子有限公司

技术研发日:

技术公布日:2024/9/26

- 还没有人留言评论。精彩留言会获得点赞!