用于嵌入式ECC保护的方法及系统与流程

本申请涉及存储器领域。

背景技术:

1、在计算系统中,存储在存储器(例如,动态随机存取存储器(dram)或双数据速率(ddr)同步动态随机存取存储器(sdram))中的数据在写入或读取操作期间可受到控制器、物理接口(phy)或电路板中的错误影响,或者当数据存储于存储器阵列中时受到存储器阵列自身中的错误影响。此外,外部存储器通常由第三方制作及/或可未针对功能安全性应用评级或对于应用而言不够可靠。来自存储器的错误数据或指令可导致系统错误地操作。系统的错误操作是不期望的,尤其在其中功能安全性或可靠性至关重要的系统或应用中。

2、通常存在三种类型的存储器错误:永久性、暂时性及系统性。永久性错误通常是存储器或相关联电路系统的物理损坏或降级的结果,或可为硅或导线中的短路。暂时性错误可归因于粒子撞击且通常导致位翻转状态(例如,在触发器中)。系统性错误是逻辑中的错误,举例来说,系统按设计正确地工作,只是在硬件或软件中存在错误。

技术实现思路

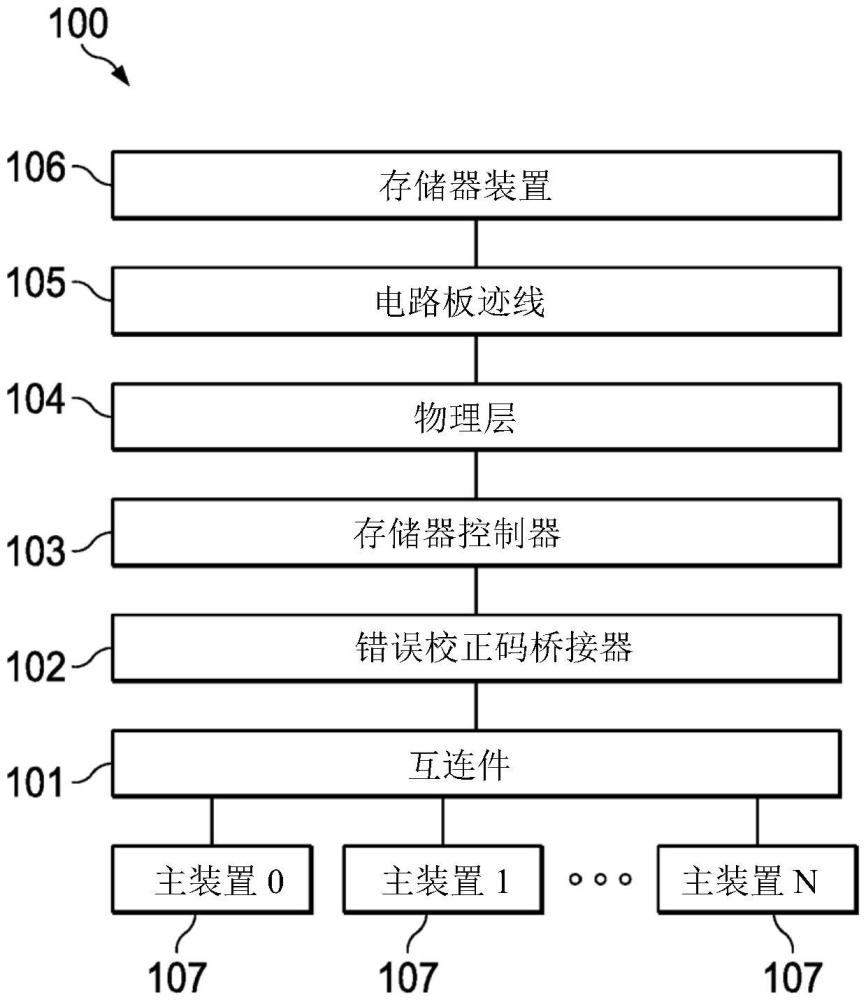

1、本文中所描述的实例包含一种集成电路,所述集成电路包含互连件,所述互连件经配置以从系统接收命令,以从存储器装置的物理地址读取数据及/或将数据写入到存储器装置的物理地址。所述集成电路进一步包含桥接器,所述桥接器经配置以从所述互连件接收所述命令并通过以下操作在系统地址与所述物理地址之间执行地址翻译:计算用于在具有第一数据地址的第一数据块之后且邻近于所述第一数据块的第一ecc数据块的第一错误校正码(ecc)存储器地址,计算在所述第一ecc块之后且邻近于所述第一ecc块的第二ecc存储器地址,以及计算在所述第二ecc块之后且邻近于所述第二ecc块的第二数据地址。

2、本文中所描述的另一例示性集成电路包含互连件,所述互连件经配置以从系统接收命令,用于读取及/或写入数据的一部分。所述集成电路进一步包含桥接器,所述桥接器经配置以从所述互连件接收所述命令并检查及计算包含数据的所述部分的数据突发的ecc数据。

3、本文中所描述的另一例示性集成电路包含互连件,所述互连件经配置以从系统接收命令,用于读取及/或写入数据的一部分。所述集成电路进一步包含桥接器,所述桥接器经配置以从所述互连件接收所述命令并检查及计算ecc数据,所述桥接器进一步经配置以缓存包含数据的所述部分的完整数据突发的ecc数据。

4、本文中所描述的实例还包含存储器系统,所述存储器系统具有存储器装置、处理器及互连件,所述互连件经配置以从所述处理器接收命令,以从所述存储器装置的物理地址读取数据及/或将数据写入到所述存储器装置的物理地址。所述存储器装置进一步包含桥接器,所述桥接器经配置以从所述互连件接收所述命令并通过以下操作在系统地址与所述物理地址之间执行地址翻译:计算用于在具有第一数据地址的第一数据块之后且邻近于所述第一数据块的第一ecc数据块的第一ecc存储器地址,计算在所述第一ecc块之后且邻近于所述第一ecc块的第二ecc存储器地址,以及计算在所述第二ecc块之后且邻近于所述第二ecc块的第二数据地址。

5、本文中所描述的另一例示性存储器装置包含存储器系统,所述存储器系统具有存储器装置、处理器及互连件,所述互连件经配置以从所述处理器接收命令,用于读取数据的一部分及/或将数据的一部分写入到所述存储器装置;以及桥接器,其经配置以从所述互连件接收所述命令并检查及计算ecc数据,所述桥接器进一步经配置以缓存包含数据的所述部分的完整数据突发的ecc数据。

6、本文中所描述的实例还包含一种将数据写入到外部存储器或从外部存储器读取数据的方法。所述方法包含:从系统接收命令,用于读取及/或写入数据的一部分;及缓存包含数据的所述部分的完整数据突发的ecc数据。

7、本文中还描述将数据写入到外部存储器或从外部存储器读取数据的例示性方法。所述方法包含:从系统接收命令,用于读取及/或写入数据的一部分,并检查包含数据的所述部分的完整数据突发的ecc数据。

8、本文中还描述将系统存储器地址翻译成物理存储器地址的例示性方法。所述方法包含:提供与第一数据块相关联的第一ecc块及提供与第二数据块相关联的第二ecc块。所述方法进一步包含:计算用于在具有第一数据地址的所述第一数据块之后且邻近于所述第一数据块的所述第一ecc数据块的第一ecc存储器地址,计算在所述第一ecc块之后且邻近于所述第一ecc块的第二ecc存储器地址,以及计算用于在所述第二ecc块之后且邻近于所述第二ecc块的所述第二数据块的第二数据地址。

技术特征:

1.一种集成电路,其包括:

2.根据权利要求1所述的集成电路,其中所述第一数据地址在所述存储器的所述地址空间中与第二数据地址相邻。

3.根据权利要求2所述的集成电路,其中:

4.根据权利要求1所述的集成电路,其中:

5.根据权利要求4所述的集成电路,其中:

6.根据权利要求1所述的集成电路,其中:

7.根据权利要求6所述的集成电路,其中所述ecc电路进一步包括ecc编码器电路,所述ecc编码器电路耦合到所述仲裁电路并且经配置以,当所述存储器命令与所述第一数据单元的所述写入相关联时:

8.根据权利要求7所述的集成电路,其中所述ecc编码器电路经配置以对以下中的至少一者进行编码:所述第一数据地址或者所述ecc数据中的所述第一ecc地址。

9.根据权利要求1所述的集成电路,其进一步包括:

10.根据权利要求1所述的集成电路,其进一步包括:

11.根据权利要求1所述的集成电路,其进一步包括:

12.一种方法,其包括:

13.根据权利要求12所述的方法,其中所述确定所述第一数据地址以使得在所述存储器的所述地址空间中所述第一数据地址与第二数据地址相邻。

14.根据权利要求13所述的方法,其中所述第二数据地址与第四数据单元相关联,所述第四数据单元不与所述第一ecc数据相关联。

15.根据权利要求12所述的方法,其中:

16.根据权利要求15所述的方法,其中:

17.根据权利要求12所述的方法,其进一步包括:

18.根据权利要求12所述的方法,其进一步包括:

19.根据权利要求18所述的方法,其中所述生成所述第一ecc数据包括对以下中的至少一者进行编码:所述第一数据地址或者所述ecc数据中的所述第一ecc地址。

20.根据权利要求12所述的方法,其进一步包括:

21.一种装置,其包括:

22.根据权利要求21所述的装置,其中所述电路经配置以:

23.根据权利要求21所述的装置,其中:

24.根据权利要求21所述的装置,其中所述存储器是随机存取存储器。

25.根据权利要求21所述的装置,其中所述第一组ecc数据是单错误校正双错误检测secded数据。

26.根据权利要求21所述的装置,其中所述第一组ecc数据对以下中的至少一者进行编码:所述第一组数据的地址或所述第一组ecc数据的地址。

27.根据权利要求21所述的装置,其中:

28.一种装置,其包括:

29.根据权利要求28所述的装置,其中所述存储器控制电路包括ecc计算电路,所述ecc计算电路经配置以生成所述第一组ecc数据和所述第二组ecc数据。

30.根据权利要求28所述的装置,其中:

31.根据权利要求28所述的装置,其中所述存储器是随机存取存储器。

32.根据权利要求28所述的装置,其中所述第一组ecc数据是单错误校正双错误检测secded数据。

33.根据权利要求28所述的装置,其中所述第一组ecc数据对以下中的至少一者进行编码:所述第一组数据的地址或所述第一组ecc数据的地址。

34.根据权利要求28所述的装置,其中:

35.一种方法,其包括:

36.根据权利要35所述的方法,其中所述接收所述第一组数据包括:

37.根据权利要求35所述的方法,其中所述存储器是随机存取存储器。

38.根据权利要求35所述的方法,其中所述第一组ecc数据是单错误校正双错误检测secded数据。

39.根据权利要求35所述的方法,其中所述第一组ecc数据对以下中的至少一者进行编码:所述第一组数据的地址或所述第一组ecc数据的地址。

40.根据权利要求35所述的方法,其中:

技术总结

本发明涉及用于嵌入式ECC保护的方法及系统,并具体提出了一种存储器系统,其具有互连件,所述互连件经配置以从系统接收命令,以从存储器装置读取数据及/或将数据写入到存储器装置。所述存储器系统还具有桥接器,所述桥接器经配置以从所述互连件接收所述命令以管理ECC数据,并通过以下操作在系统地址与物理存储器装置地址之间执行地址翻译:计算用于在具有第一数据地址的第一数据块之后且邻近于所述第一数据块的第一ECC数据块的第一ECC存储器地址,计算在所述第一ECC块之后且邻近于所述第一ECC块的第二ECC存储器地址,以及计算在所述第二ECC块之后且邻近于所述第二ECC块的第二数据地址。

技术研发人员:D·R·博杜安,R·D·索吉特拉,S·P·维萨利

受保护的技术使用者:德州仪器公司

技术研发日:

技术公布日:2024/12/17

- 还没有人留言评论。精彩留言会获得点赞!