存储装置以及用于存储错误管理的方法与流程

本说明内容涉及存储器纠错,且更具体来说涉及高带宽存储器(hbm)可靠性、可存取性及可服务性(ras)高速缓存架构。

背景技术:

1、高带宽存储器(high bandwidth memory,hbm)是用于堆叠的动态随机存取存储器(dynamic random-access memory,dram)的高性能随机存取存储器(random-accessmemory,ram)接口。高带宽存储器通常结合高性能图形加速器及网络器件一起使用。使用hbm的第一器件是图形处理单元(graphical processing unit,gpu)。

2、与双倍数据速率第四代同步dram(doubledata rate fourth-generationsynchronous dram,ddr4)或双倍数据速率类型五同步图形随机存取存储器(doubledatarate type five synchronous graphics random-access memory,gddr5)相比,hbm以实质上较小的形状因子在使用较小的功率的同时实现较高的带宽。这常常是通过堆叠许多(例如,8个)dram裸片来实现的,所述许多dram裸片包括具有存储器控制器的可选的基础裸片且通过硅通孔(through-silicon via,tsv)及微凸块来进行互连。

3、hbm存储器总线与其他dram存储器(例如ddr4或gddr5)相比非常宽。四个dram裸片的hbm堆叠(4-hi)的每个裸片通常具有两个128位信道以实现总共8个信道以及总共1024位的宽度。具有四个4-hi hbm堆叠的图形卡/gpu因此将具有宽度为4096位的存储器总线。相比之下,gddr存储器的总线宽度是32位,对于具有512位存储器接口的图形卡来说具有16个信道。

4、相对于ddr4或gddr5,对存储器的较大数目的连接需要将hbm存储器连接到gpu(或其他处理器)的新的方法。一些公司使用特制硅芯片(被称为插入件)来连接存储器与gpu。这种插入件(interposer)已增加需要使存储器与处理器实体接近的优点,从而减少存储路径。然而,由于半导体器件制作明显比印刷电路板制造更昂贵,因此,这会使最终产品的成本增加。

技术实现思路

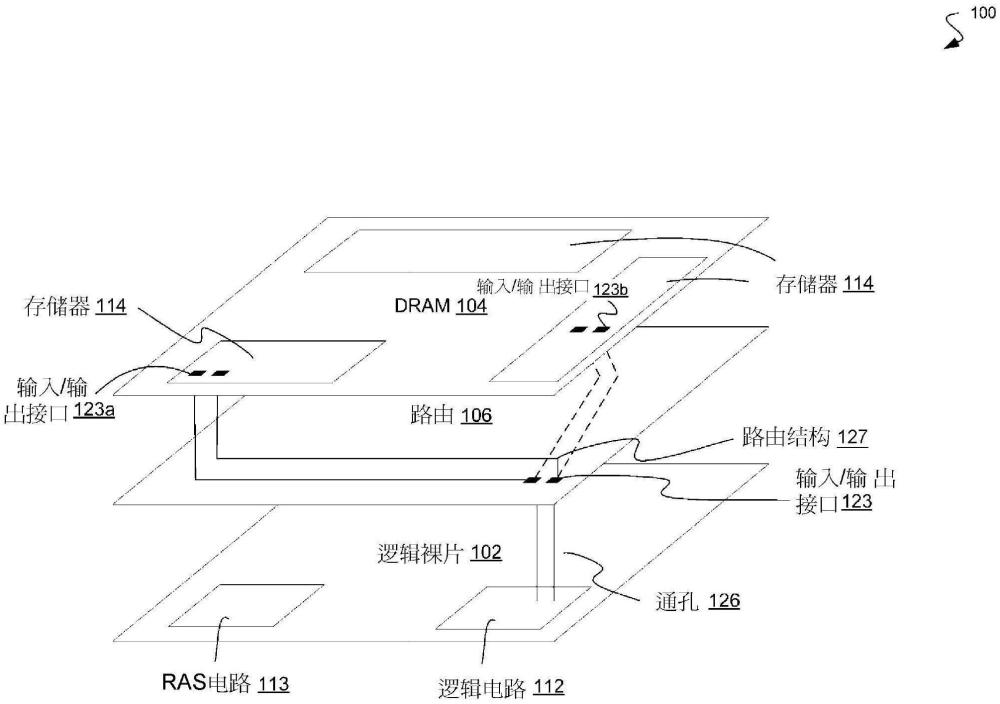

1、根据一个一般方面,一种存储装置可包括多个堆叠的集成电路裸片。所述堆叠的集成电路裸片可包括存储单元裸片及逻辑裸片。所述存储单元裸片可被配置成以基于存储地址的随机存取方式来存储数据。所述逻辑裸片可包括与所述多个堆叠的集成电路裸片的接口,且所述接口被配置成在所述存储单元裸片与至少一个外部器件之间传送存储器存取。所述逻辑裸片可包括可靠性电路,所述可靠性电路被配置成改善所述存储单元裸片内的数据错误。所述可靠性电路可包括备用存储器以及地址表,所述备用存储器被配置成以随机存取方式来存储数据,所述地址表被配置成将与错误相关联的存储地址映射到所述备用存储器的一部分。所述可靠性电路可被配置成当进行对所述多个堆叠的集成电路裸片的存储器存取时,判断所述存储器存取是否与错误相关联,且如果是,则至少部分地利用所述备用存储器来完成所述存储器存取。

2、根据另一一般方面,一种多芯片系统可包括处理器,所述处理器包括存储器控制器以及纠错电路,所述存储器控制器被配置成管理往来于所述处理器的数据流,所述纠错电路被配置成检测所存储的数据中是否出现错误。所述系统可包括集成电路的高带宽存储堆叠,所述集成电路的高带宽存储堆叠包括:高带宽存储单元,被配置成基于存储地址而存储数据;以及可靠性电路,被配置成改善所述高带宽存储单元内的数据错误。所述可靠性电路可包括备用存储器以及地址表,所述备用存储器被配置成存储数据,所述地址表被配置成将与所述错误相关联的存储地址映射到所述备用存储器的一部分。所述可靠性电路被配置成当进行对集成电路的所述高带宽存储堆叠的存储器存取时,判断所述存储器存取是否与错误相关联,且如果是,则至少部分地利用所述备用存储器来完成所述存储器存取。

3、根据另一一般方面,一种存储装置可包括逻辑裸片,所述逻辑裸片包括与高带宽存储器裸片的内部接口,其中所述高带宽存储器裸片被配置成基于存储地址而存储数据。所述逻辑裸片可包括外部接口,所述外部接口被配置成在所述高带宽存储器裸片与至少一个外部器件之间传送存储器存取。所述逻辑裸片可包括可靠性电路,所述可靠性电路被配置成改善所述高带宽存储器裸片内的数据错误。所述可靠性电路可包括备用存储器以及地址表,所述备用存储器被配置成存储数据,所述地址表被配置成将与错误相关联的存储地址映射到所述备用存储器的一部分。所述可靠性电路可被配置成当进行对所述高带宽存储器裸片的存储器存取时,判断所述存储器存取是否与错误相关联,且如果是,则至少部分地利用所述备用存储器来完成所述存储器存取。

4、在附图及以下说明内容中阐述一种或多种实施方式的详细情况。通过阅读说明内容及图式以及阅读权利要求书,其他特征将显而易见。

5、实质上在各图中的至少一个图中示出了和/或结合各图中的至少一个图阐述了用于存储器纠错的系统和/或方法,且更具体来说高带宽存储器(hbm)可靠性、可存取性及可服务性(reliability,accessibility,and serviceability,ras)高速缓存架构,如在权利要求书中更完整地阐述。

技术特征:

1.一种存储装置,包括:

2.根据权利要求1所述的存储装置,其中与所述错误相关联的所述存储地址存储于地址数据结构中,所述地址数据结构包括:

3.根据权利要求1所述的存储装置,其中所述逻辑裸片被配置成:

4.根据权利要求1所述的存储装置,其中与所述错误相关联的所述存储地址存储于地址数据结构中,且所述逻辑裸片被配置成通过以下步骤来确定所述存储地址与错误相关联:

5.根据权利要求1所述的存储装置,其中所述逻辑裸片被配置成:

6.根据权利要求1所述的存储装置,其中与所述错误相关联的所述存储地址存储于地址数据结构中,且所述逻辑裸片被配置成:

7.根据权利要求6所述的存储装置,其中所述逻辑裸片被配置成通过以下步骤接收指示存储地址与错误相关联的消息:

8.根据权利要求1所述的存储装置,其中所述逻辑裸片被配置成:

9.根据权利要求1所述的存储装置,其中所述逻辑裸片被配置成基于所述第一器件的操作状态而提供关于所述逻辑裸片的地址映射操作的信息。

10.一种用于存储错误管理的方法,所述方法包括:

11.根据权利要求10所述的方法,其中所述第一指示包括与所述存储器裸片的所述一部分相关联的地址。

12.根据权利要求11所述的方法,还包括由所述可靠性电路将与所述存储器裸片的所述一部分相关联的所述地址映射到所述备用存储器的所述一部分。

13.根据权利要求12所述的方法,其中:

14.根据权利要求12所述的方法,其中:

15.根据权利要求11所述的方法,还包括将所述地址存储于非易失性存储器中。

16.根据权利要求10所述的方法,其中所述第一器件包括主机器件。

17.根据权利要求10所述的方法,其中所述可靠性电路被设置于逻辑裸片上。

18.一种存储装置,包括:

19.根据权利要求18所述的存储装置,其中所述逻辑裸片被配置成:

20.根据权利要求18所述的存储装置,其中所述逻辑裸片被配置成:

技术总结

根据一个一般方面,提供了一种存储装置以及多芯片系统。存储装置可包括多个堆叠的集成电路裸片,所述多个堆叠的集成电路裸片包括存储单元裸片及逻辑裸片。存储单元裸片可被配置成将数据存储在存储地址处。逻辑裸片可包括与所述堆叠的集成电路裸片的接口且所述接口被配置成在存储单元裸片与至少一个外部器件之间传送存储器存取。逻辑裸片可包括可靠性电路,可靠性电路被配置成改善存储单元裸片内的数据错误。可靠性电路可包括备用存储器以及地址表,备用存储器被配置成存储数据,地址表被配置成将与错误相关联的存储地址映射到备用存储器。可靠性电路可被配置成判断存储器存取是否与错误相关联,且如果是,则利用备用存储器来完成存储器存取。

技术研发人员:牛迪民,克里希纳·马拉迪,郑宏忠

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2025/1/28

- 还没有人留言评论。精彩留言会获得点赞!