PCIe测试系统、方法、设备及介质与流程

本申请涉及fpga测试,尤其是涉及一种pcie测试系统、方法、设备及介质。

背景技术:

1、随着技术的发展,传统pcie芯片在fpga中的应用日益广泛。传统的测试手段在测试过程中,通常对rp和ep分别进行独立测量,这不仅增加了设备投入,延长了测试周期。

2、目前测试流程中,为了全面验证功能,需要对rp和ep分别进行详细的测试,但对同一芯片而言,既要测试rp模式也要测试ep模式,测试设备需要频繁的切换测试配置与测试环境,这导致了资源的合理利用率极低,造成不必要的资源浪费,甚至影响测试效率,使得测试耗费的时间较长,上述问题有待解决。

技术实现思路

1、为了减少对fpag内pcie的测试耗时,提升测试效率,本申请提供一种pcie测试系统、方法、设备及介质,采用如下技术方案:

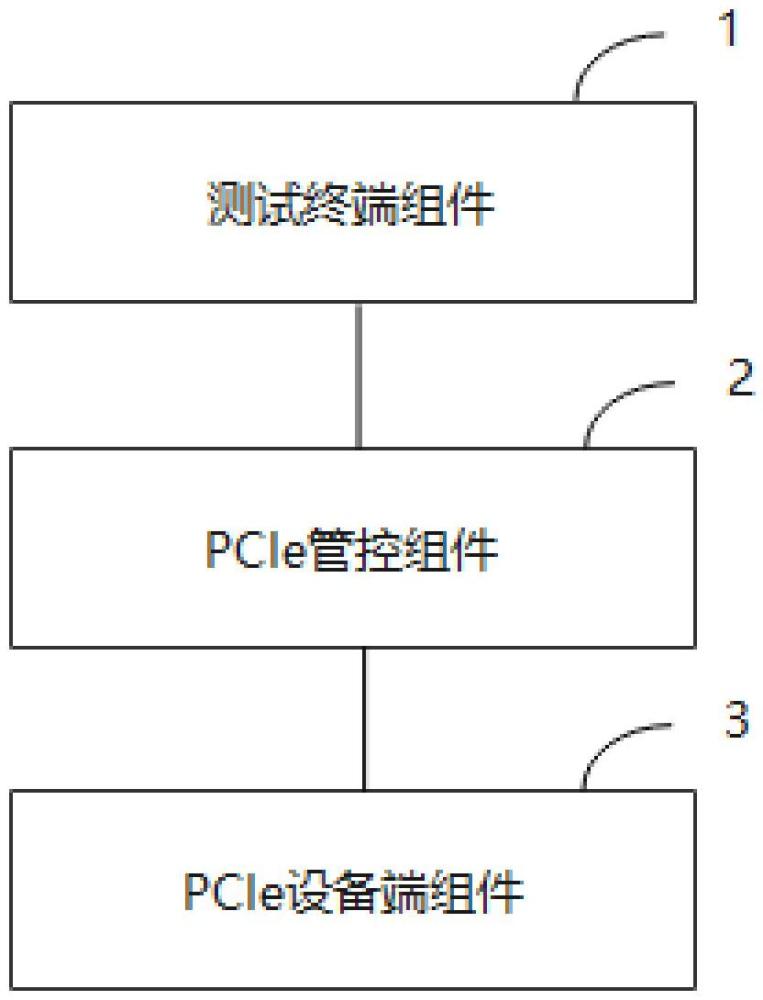

2、第一方面,本申请提供一种pcie测试系统,包括:

3、pcie管控组件,用于获取测试终端组件的测试数据,对测试数据进行解析得到第一tlp报文信息和第二tlp报文信息,根据第一tlp报文信息执行第一测试操作,得到第一完成标志信息;

4、pcie设备端组件,用于获取pcie管控组件的第二tlp报文信息,根据第二tlp报文信息执行第二测试操作,得到第二完成标志信息;

5、测试终端组件,用于获取连接状态信息,在连接状态信息为连接成功的情况下,对pcie管控组件发送测试数据;获取第一完成标志信息,对第一完成标志信息进行第一预期分析,在分析得到的第一分析结果为符合预期的情况下,获取第二完成标志信息;对第二完成标志信息进行第二预期分析,得到用于反映rp和ep测试情况的第二分析结果。

6、优选的,所述pcie管控组件包括:

7、串口解析模块,用于根据串口协议对测试数据进行解析,得到串口有效信息;

8、指令转换模块,用于根据内部定义用户寄存器控制tlp的读写,得到指令信息。

9、优选的,所述pcie管控组件还包括:

10、rp tlp发送处理模块,用于根据指令信息向rp控制器发送对应的第一tlp报文信息和第二tlp报文信息;

11、rp控制器,用于将第二tlp报文信息发送至对端ep设备,且获取对端ep设备的处理状态信息。

12、优选的,所述pcie管控组件还包括:

13、rp tlp接收处理模块,用于获取处理状态信息,根据处理状态信息校验得到第一完成标志信息。

14、优选的,所述pcie设备端组件包括:

15、ep tlp发送与接受处理模块,用于获取ep控制器的第二tlp报文信息,对第二tlp报文信息进行解析操作,在解析的过程中得到第二完成标志信息,第二完成标志信息包括cpl报文信息和cpld报文信息;

16、ep控制器,用于获取pcie管控组件的第二tlp报文信息,将第二tlp报文信息传输至ep tlp发送与接收处理模块,将接收的cpl报文信息和cpld报文信息发送至对端rp设备。

17、优选的,还包括:

18、时钟分频模块,用于获取25mhz系统时钟信号,根据25mhz系统时钟信号构建用于数据处理的串口处理时钟和用户时钟。

19、优选的,所述pcie管控组件还包括:

20、时钟配置模块,用于初始化和配置时钟芯片。

21、第二方面,本申请提供一种pcie测试方法,包括:

22、获取连接状态信息,在连接状态信息为连接成功的情况下,对pcie管控组件发送测试数据;

23、获取第一完成标志信息,对第一完成标志信息进行第一预期分析,在分析得到的第一分析结果为符合预期的情况下,获取第二完成标志信息;

24、对第二完成标志信息进行第二预期分析,得到用于反映rp和ep测试情况的第二分析结果。

25、第三方面,本申请提供一种测试终端设备,包括存储器和处理器,所述存储器存储计算机程序,所述处理器被设置为运行所述计算机程序以执行如前所述的pcie测试方法。

26、第四方面,本申请提供一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,其中,所述计算机程序被设置为运行时执行如前所述的pcie测试方法。

27、综上所述,与现有技术相比,本申请提供的技术方案带来的有益效果至少包括:

28、本申请通过将测试终端组件和pcie管控组件连接,pcie管控组件和pcie设备端组件连接,通过测试终端组件控制pcie管控组件和pcie设备端组件执行测试步骤,使得测试系统的组件均在同一运行环境中运行,同时完成对pcie管控组件和pcie设备端组件的测试,在测试后测试终端组件对测试得到标志信息进行分析,得到的第一分析结果和第二分析结果,从而判断pcie系统的测试情况,完成数据测试与验证,在同一测试环境下,无需频繁切换硬件或软件设置,减少对fpag内pcie的测试耗时,提升测试效率。

技术特征:

1.一种pcie测试系统,其特征在于,包括:

2.根据权利要求1所述的pcie测试系统,其特征在于,所述pcie管控组件包括:

3.根据权利要求2所述的pcie测试系统,其特征在于,所述pcie管控组件还包括:

4.根据权利要求3所述的pcie测试系统,其特征在于,所述pcie管控组件还包括:

5.根据权利要求1所述的pcie测试系统,其特征在于,所述pcie设备端组件包括:

6.根据权利要求1所述的pcie测试系统,其特征在于,还包括:

7.根据权利要求1所述的pcie测试系统,其特征在于,所述pcie管控组件还包括:

8.一种pcie测试方法,其特征在于,包括:

9.一种测试终端设备,其特征在于,包括存储器和处理器,所述存储器存储计算机程序,所述处理器被设置为运行所述计算机程序以执行权利要求8中所述的pcie测试方法。

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质中存储有计算机程序,其中,所述计算机程序被设置为运行时执行权利要求8中所述的pcie测试方法。

技术总结

本申请涉及FPGA测试技术领域,尤其是涉及一种PCIe测试系统、方法、设备及介质,方法包括获取连接状态信息,在连接状态信息为连接成功的情况下,对PCIe管控组件发送测试数据;获取第一完成标志信息,对第一完成标志信息进行第一预期分析,在分析得到的第一分析结果为符合预期的情况下,获取第二完成标志信息;对第二完成标志信息进行第二预期分析,得到用于反映RP和EP测试情况的第二分析结果,减少对FPAG内PCIe的测试耗时,提升测试效率。

技术研发人员:葛洪,郭德鑫

受保护的技术使用者:上海安路信息科技股份有限公司

技术研发日:

技术公布日:2025/1/16

- 还没有人留言评论。精彩留言会获得点赞!