一种指令存储器和电子设备的制作方法

本申请涉及集成电路,具体涉及一种指令存储器和电子设备。

背景技术:

1、指令存储器是用于存储处理器(cpu)要执行的指令,为了提升报文处理性能,处理器通常会设置多个处理器核(cpu核)进行负载分担,同时多个处理器核运行相同的报文处理程序,以提升pps(中文全称为:每秒钟处理的报文数量,英文全称为:packet persecond),例如32核、64核、96核等,每个处理器核都设置了专属的指令存储器,每个处理器核运行时都固定从各自专属的指令存储器中取指令进行执行。这些指令存储器一般会使用芯片中的片上sram(中文全称为:静态随机存取存储器,英文全称为:static random-access memory)实现,由于每个处理器核都设置一个专属的指令存储器,会增大指令存储器的芯片面积和功耗消耗,特别是处理器核的数量比较多的情况,芯片面积和功耗消耗的增大比较明显。

技术实现思路

1、本申请的目的在于提供一种指令存储器和电子设备,解决每个处理器核都设置一个专属的指令存储器,会增大指令存储器的芯片面积和功耗消耗的技术问题。

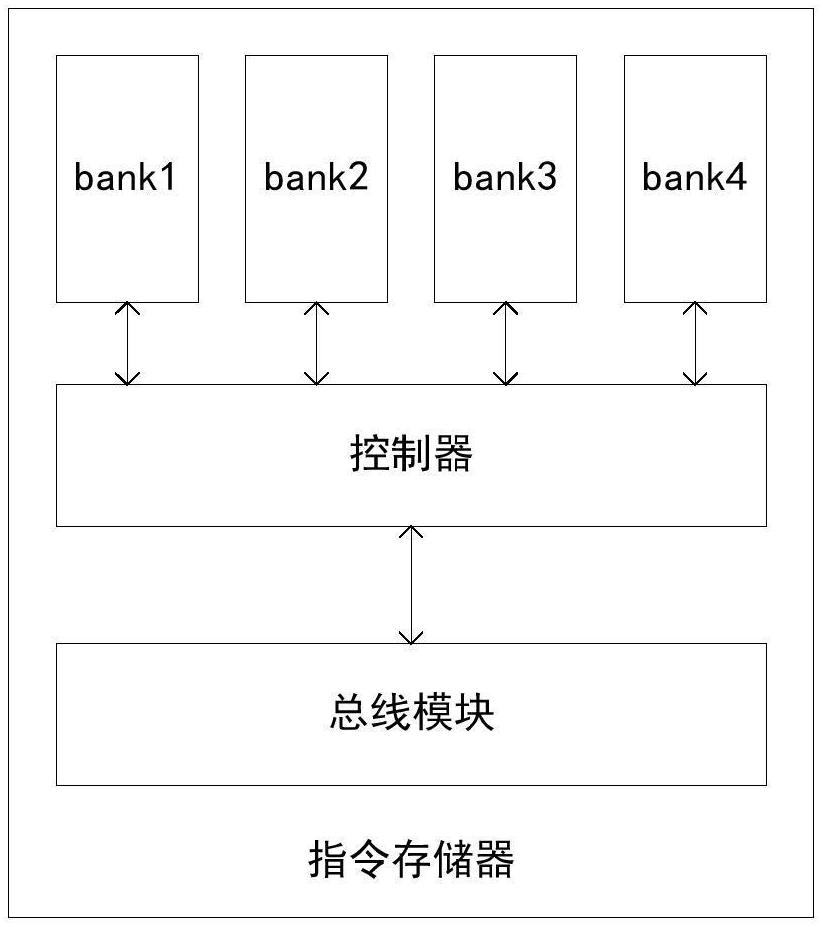

2、根据本申请第一方面,提供一种指令存储器,所述指令存储器为多存储体存储器,包括n个存储体、控制器和总线模块,所述n个存储体均与所述控制器连接,所述总线模块与所述控制器连接,所述总线模块还与m个处理器核连接;n和m为预设的值;

3、所述总线模块,用于将所述读命令发送给所述控制器,并接收所述控制器返回的指令,将所述控制器返回的指令通过对应的核接口发送给对应的处理器核;

4、所述控制器,用于根据所述读命令从对应的存储体读取指令,并将读取的指令返回给总线模块。

5、在一具体实施方式中,所述总线模块包括控制器接口和m个核接口,所述总线通过所述控制器接口与所述控制器连接,所述总线通过所述m个核接口分别与所述m个处理器核连接,所述m个核接口与所述m个处理器核一一对应;所述读命令携带有接口id和读地址;

6、所述控制器,具体用于解析所述读命令得到接口id和读地址,根据所述读地址从对应的存储体读取指令,并将读取的指令和所述接口id生成读数据,将所述读数据返回给总线模块;

7、所述总线模块,具体用于根据所述读地址将所述读命令发送给所述控制器,以及,对所述读数据进行解析得到所述接口id和所述返回的指令,并根据所述接口id将所述返回的指令通过对应的核接口发送给对应的处理器核。

8、在一具体实施方式中,所述控制器包括n个控制单元,所述n个控制单元与所述n个存储体一一对应连接;所述控制器接口包括n个控制单元接口,所述总线通过所述n个控制单元接口分别与所述n个控制单元连接,所述n个控制单元接口与所述n个控制单元一一对应;

9、所述控制单元,用于当其接收到所述读命令时,解析所述读命令得到接口id和读地址,根据所述读地址从与其对应的存储体读取指令,并将读取的指令和所述接口id生成读数据,将所述读数据返回给总线模块;

10、所述总线模块,具体用于根据所述读地址将所述读命令发送给对应的控制单元,以及,对所述对应的控制单元返回的所述读数据进行解析得到所述接口id和所述返回的指令,并根据所述接口id将所述返回的指令通过对应的核接口发送给对应的处理器核。

11、在一具体实施方式中,所述总线模块,具体用于同一时钟周期接收到多个处理器核的读指令,且所述多个处理器核的读指令请求访问同一个存储体时,采用轮询调度策略处理所述多个处理器核的读指令。

12、在一具体实施方式中,所述指令存储器包括写接口,所述控制器均与所述写接口连接;

13、所述写接口,用于接收写命令,并将所述写命令发送给所述控制器;

14、所述控制器,还用于根据所述写命令获得待写指令和写地址,并根据所述写地址将所述待写指令写入对应的存储体。

15、在一具体实施方式中,所述控制器包括n个控制单元,所述n个控制单元与所述n个存储体一一对应连接;所述读命令携带有接口id和读地址;

16、所述写接口,用于接收写命令,解析所述写命令得到写地址和待写指令,根据所述写地址将所述写地址和待写指令发送给对应的控制单元;

17、所述控制单元,用于当其接收到所述写地址和待写指令时,根据所述写地址将所述待写指令写入与其对应的存储体。

18、在一具体实施方式中,所述总线模块为交叉开关矩阵。

19、在一具体实施方式中,所述指令存储器用于存储二进制执行程序,所述二进制执行程序按执行顺序依次划分多段程序,所述多段程序均分到所述n个存储体进行存储,每段程序包括至少一条指令,每个存储体的一个深度地址的存储空间存储一段程序。

20、根据本申请第二方面,提供一种电子设备,包括网络处理器和如上所述的指令存储器,所述网络处理器包括所述m个处理器核。

21、在一具体实施方式中,所述网络处理器还包括n个读指令缓存器,所述n个读指令缓存器与所述m个处理器核一一对应;

22、所述读指令缓存器,用于暂时存放与其对应的cpu核的预取指。

23、本申请实施例提供了一种指令存储器和电子设备,m个处理器核共享一个指令存储器,其中,该一个指令存储器划分为n个存储体(bank),即由n个存储体拼接形成一个指令存储器,n个存储体均存储有指令,在访问指令存储器时,m个处理器核将读指令发送给总线模块,总线模块将读指令发给控制器,控制器根据读指令从对应的存储体中读取相应的指令,并通过总线模块将读取的指令发送给对应的处理器核,n个存储体都可以响应m个处理器核的读访问,因此有利于指令存储器的带宽跑满,相对于为每一个处理器核设置一个专属的指令存储器而言,减少了指令存储器的数量,有利于减少芯片面积和功耗消耗,将使指令存储器所占用的芯片面积减小到原有的1/m,节约了用户成本。

技术特征:

1.一种指令存储器,其特征在于,所述指令存储器为多存储体存储器,包括n个存储体、控制器和总线模块,所述n个存储体均与所述控制器连接,所述总线模块与所述控制器连接,所述总线模块还与m个处理器核连接;n和m为预设的值;

2.根据权利要求1所述的指令存储器,其特征在于,所述总线模块包括控制器接口和m个核接口,所述总线通过所述控制器接口与所述控制器连接,所述总线通过所述m个核接口分别与所述m个处理器核连接,所述m个核接口与所述m个处理器核一一对应;所述读命令携带有接口id和读地址;

3.根据权利要求2所述的指令存储器,其特征在于,所述控制器包括n个控制单元,所述n个控制单元与所述n个存储体一一对应连接;所述控制器接口包括n个控制单元接口,所述总线通过所述n个控制单元接口分别与所述n个控制单元连接,所述n个控制单元接口与所述n个控制单元一一对应;

4.根据权利要求3所述的指令存储器,其特征在于,所述总线模块,具体用于同一时钟周期接收到多个处理器核的读指令,且所述多个处理器核的读指令请求访问同一个存储体时,采用轮询调度策略处理所述多个处理器核的读指令。

5.根据权利要求1所述的指令存储器,其特征在于,所述指令存储器包括写接口,所述控制器均与所述写接口连接;

6.根据权利要求5所述的指令存储器,其特征在于,所述控制器包括n个控制单元,所述n个控制单元与所述n个存储体一一对应连接;所述读命令携带有接口id和读地址;

7.根据权利要求6所述的指令存储器,其特征在于,所述总线模块为交叉开关矩阵。

8.根据权利要求1~7中任一项所述的指令存储器,其特征在于,所述指令存储器用于存储二进制执行程序,所述二进制执行程序按执行顺序依次划分多段程序,所述多段程序均分到所述n个存储体进行存储,每段程序包括至少一条指令,每个存储体的一个深度地址的存储空间存储一段程序。

9.一种电子设备,其特征在于,包括网络处理器和权利要求1~8中任一项所述的指令存储器,所述网络处理器包括所述m个处理器核。

10.根据权利要求9所述的电子设备,其特征在于,所述网络处理器还包括n个读指令缓存器,所述n个读指令缓存器与所述m个处理器核一一对应;

技术总结

本申请涉及一种指令存储器和电子设备,所述指令存储器为多存储体存储器,包括n个存储体、控制器和总线模块,n个存储体均与控制器连接,总线模块与控制器连接,总线模块还与m个处理器核连接;n和m为预设的值;总线模块,用于当其接收到任意一个处理器核的读命令时,将读命令发送给控制器,并接收控制器返回的指令,将控制器返回的指令通过对应的核接口发送给对应的处理器核;控制器,用于根据读命令从对应的存储体读取指令,并将读取的指令返回给总线模块。所述电子设备包括所述指令存储器,所述方法基于所述指令存储器实现,通过本申请,能够减少指令存储器的芯片面积和功耗消耗。

技术研发人员:张学利,秦增杰,董德吉

受保护的技术使用者:深圳云豹智能有限公司

技术研发日:

技术公布日:2024/12/19

- 还没有人留言评论。精彩留言会获得点赞!