基于FPGA的Cholesky矩阵分解求逆方法与流程

本发明涉及信号处理,尤其涉及一种基于fpga的cholesky矩阵分解求逆方法。

背景技术:

1、在基于fpga的信号处理算法中,常需要对计算过程中的协方差矩阵进行求逆运算,为了使用fpga实现矩阵求逆算法,需要将矩阵求逆的过程分解为基本的加减乘除运算。一般的矩阵求逆的方法如初等变换法、伴随矩阵法、高斯消元法等需要用到大量的行列式计算,计算量大、存储空间需求大、资源消耗多的缺点令其不适用于fpga,而矩阵分解法实现矩阵求逆的运算量小且易于实现,因此,在fpga中一般选择矩阵分解法来实现矩阵求逆。

2、矩阵分解法是将矩阵分解为一些简单矩阵的乘积,如三角矩阵或酉矩阵,他们都具有某种特性,较容易得到逆矩阵。常用的矩阵分解方法有:奇异值分解、lu分解、qr分解和cholesky分解。其中,前三种分解方法是对所有可逆的复数矩阵进行求逆计算的,算法较为复杂不易实现且资源使用较多,而cholesky分解适用于共轭对称正定矩阵。在信号处理算法中,当需要求逆的矩阵为自相关后的协方差矩阵时,有共轭对称特性,符合cholesky分解的适用范围。

3、但是,现有的基于fpga的cholesky矩阵分解求逆方法仍然存在分解计算运算量巨大,硬件资源消耗大的问题。

技术实现思路

1、本发明的目的在于解决背景技术中的至少一个技术问题,提供一种基于fpga的cholesky矩阵分解求逆方法。

2、为实现上述目的,本发明提供一种基于fpga的cholesky矩阵分解求逆方法,包括:

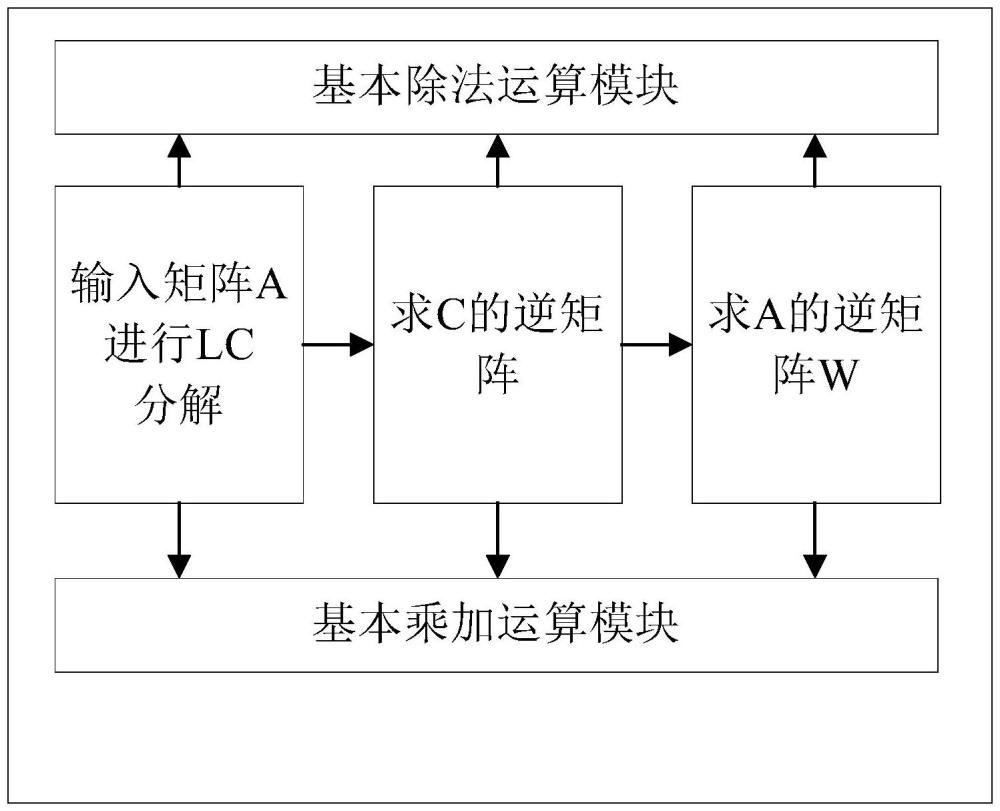

3、将矩阵分解求逆过程分为三个状态机,三个状态机分别进行lc矩阵分解、求矩阵c的逆矩阵y、求协方差矩阵a的逆矩阵w;

4、第一状态机按照矩阵l、矩阵c中元素的地址顺序,对输入的协方差矩阵a进行cholesky分解,得到下三角矩阵c与下三角矩阵l,计算完成后将结果存储到对应矩阵l、矩阵c的ram中存储,完成lc矩阵分解;

5、完成lc矩阵分解后,切换至第二状态机,第二状态机按照矩阵c、矩阵y中元素的地址顺序,对矩阵c进行求逆计算,将计算结果存储到矩阵y,,计算存储完所有y矩阵的元素数据后,完成求矩阵c的逆矩阵y;

6、完成求矩阵c的逆矩阵y后,切换至第三状态机,第三状态机按照矩阵l、矩阵w中元素的地址顺序,对矩阵l进行求逆计算,将计算结果存储到矩阵w,计算存储所有协方差矩阵a的逆矩阵w元素数据,最后输出矩阵w。

7、根据本发明的一个方面,所述第一状态机对输入的协方差矩阵a进行cholesky分解,得到下三角矩阵c与下三角矩阵l,具体公式为:

8、

9、其中,协方差矩阵a=ry cholesky分解后ry=ldlh=clh。

10、

11、根据本发明的一个方面,所述第二状态机根据以下计算公式完成求矩阵c的逆矩阵y:

12、

13、根据本发明的一个方面,由aw=clhw=e=cy可得lhw=y,第三状态机计算协方差矩阵ry的逆矩阵具体公式为:

14、

15、为实现上述目的,本发明还提供一种基于fpga的cholesky矩阵分解求逆系统,包括:

16、状态机划分模块,将矩阵分解求逆过程分为三个状态机,三个状态机分别进行lc矩阵分解、求矩阵c的逆矩阵y、求矩阵a的逆矩阵w;

17、lc矩阵分解模块,第一状态机按照矩阵l、c中元素的地址顺序,对输入的协方差矩阵a进行cholesky分解,得到下三角矩阵c与l,计算完成后将结果存储到对应矩阵l、c的ram中存储,完成lc矩阵分解;

18、逆矩阵y求解模块,完成lc矩阵分解后,切换至第二状态机,第二状态机按照矩阵c、矩阵y中元素的地址顺序,对矩阵c进行求逆计算,将计算结果存储到矩阵y,计算存储完所有y矩阵的元素数据后,完成求矩阵c的逆矩阵y;

19、逆矩阵w求解模块,完成求矩阵c的逆矩阵y后,切换至第三状态机,第三状态机按照矩阵l、矩阵w中元素的地址顺序,对矩阵l进行求逆计算,将计算结果存储到矩阵w,计算存储所有协方差矩阵a的逆矩阵w元素数据,最后输出矩阵w。

20、为实现上述目的,本发明还提供一种电子设备,包括处理器、存储器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述计算机程序被所述处理器执行时实现如上所述的基于fpga的cholesky矩阵分解求逆方法。

21、为实现上述目的,本发明还提供一种计算机可读存储介质,所述计算机可读存储介质上存储计算机程序,所述计算机程序被处理器执行时实现如上所述的基于fpga的cholesky矩阵分解求逆方法。

22、根据本发明的方案,本发明通过参数化设计实现矩阵阶数与数据位宽的自定义,便于日后的修改工作;通过分时复用ram与乘加除法的ip核,节约了fpga的硬件资源;通过元素地址索引使运算状态流水减少了运算时间。

技术特征:

1.基于fpga的cholesky矩阵分解求逆方法,其特征在于,包括:

2.根据权利要求1所述的基于fpga的cholesky矩阵分解求逆方法,其特征在于,所述第一状态机对输入的协方差矩阵a进行cholesky分解,得到下三角矩阵c与下三角矩阵l,具体公式为:

3.根据权利要求2所述的基于fpga的cholesky矩阵分解求逆方法,其特征在于,所述第二状态机根据以下计算公式完成求矩阵c的逆矩阵y:

4.根据权利要求3所述的基于fpga的cholesky矩阵分解求逆方法,其特征在于,由aw=clhw=e=cy可得lhw=y,第三状态机计算协方差矩阵ry的逆矩阵具体公式为:

5.基于fpga的cholesky矩阵分解求逆系统,其特征在于,包括:

6.电子设备,其特征在于,包括处理器、存储器及存储在所述存储器上并可在所述处理器上运行的计算机程序,所述计算机程序被所述处理器执行时实现如权利要求1-4中任一项所述的基于fpga的cholesky矩阵分解求逆方法。

7.计算机可读存储介质,其特征在于,所述计算机可读存储介质上存储计算机程序,所述计算机程序被处理器执行时实现如权利要求1-4中任一项所述的基于fpga的cholesky矩阵分解求逆方法。

技术总结

本发明涉及信号处理技术领域,尤其涉及一种基于FPGA的Cholesky矩阵分解求逆方法,包括:第一状态机按照矩阵L、C中元素的地址顺序,索引此时需要进行乘、加或除法计算的对应元素,对输入的协方差矩阵A进行Cholesky分解,得到下三角矩阵C与L,计算完成后将结果存储到对应矩阵L、C的RAM中存储,完成LC矩阵分解;完成LC矩阵分解后,切换至第二状态机,重复以上步骤并计算存储完所有Y矩阵的元素数据后,完成求矩阵C的逆矩阵Y;完成求矩阵C的逆矩阵Y后,切换至第三状态机,计算并存储矩阵A的逆矩阵W,最后输出矩阵W。本发明节约了FPGA的硬件资源;通过元素地址索引使运算状态流水减少了运算时间。

技术研发人员:梁沛涵,温富光,邹军,周锋,陈殿军

受保护的技术使用者:南京国电南自电网自动化有限公司

技术研发日:

技术公布日:2025/2/20

- 还没有人留言评论。精彩留言会获得点赞!