测试数据处理板卡、方法和测试机与流程

本申请涉及半导体测试,特别是涉及一种测试数据处理板卡、方法和测试机。

背景技术:

1、半导体自动化测试,指的是利用自动测试设备(automatic test equipment,ate)对被测器件(device under test,dut)的各项参数指标进行检测,剔除残次品以控制半导体的出厂品质。在实际测试中,测试机中数字板卡根据时序设置的采样点和比较电压,获取实际跑完码型数据对应的每个站点(site)的芯片/每个芯片的引脚(pin)的实际通道输出的电压比较值,并存储于存储装置,再由数字板卡中的捕获模块对存储于存储装置中的数据读取并进行数据处理,上传至上位机。传统的捕获模块数据处理方式,是采用软件单线程逐步提取存储的数据进行处理。随着小数据量到大数据量的需求变更,传统处理方式的处理速度已经无法满足对时间效率上的要求,存在数据处理效率低的缺点。

技术实现思路

1、基于此,有必要针对上述问题,提供一种可提高数据处理效率的测试数据处理板卡、方法和测试机。

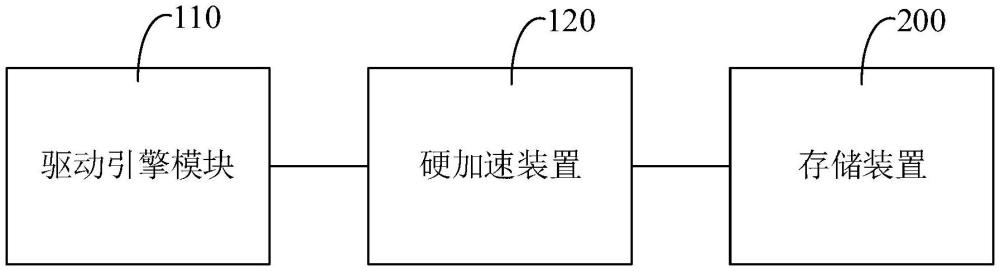

2、本申请第一方面提供一种测试数据处理板卡,包括驱动引擎模块和硬加速装置,所述硬加速装置与所述驱动引擎模块和存储装置连接;

3、所述硬加速装置用于根据所述驱动引擎模块下发的指令确认配置参数,根据所述配置参数从所述存储装置读取相应的原始捕获数据,对读取的原始捕获数据进行过滤和拼接处理,生成处理后的捕获数据发送至所述驱动引擎模块;

4、所述驱动引擎模块用于在需要处理的数据总量满足设定的异步线程开启条件时,通过异步线程对接收的捕获数据进行并行加速处理。

5、在其中一个实施例中,所述硬加速装置包括通信模块、参数解析模块、参数处理模块、读写控制模块、缓存模块和数据处理模块,所述通信模块连接驱动引擎模块、所述参数解析模块和所述数据处理模块,所述参数解析模块连接所述参数处理模块和所述数据处理模块,所述读写控制模块连接所述参数处理模块、所述缓存模块和所述存储装置,所述缓存模块连接所述数据处理模块;

6、所述参数解析模块通过所述通信模块接收所述驱动引擎模块下发的指令,对所述指令进行解析,获取配置参数发送至所述参数处理模块和所述数据处理模块;

7、所述参数处理模块对接收的配置参数进行解析,获取数据读取信息发送至所述读写控制模块;所述读写控制模块根据所述数据读取信息,从所述存储装置中读取相应的原始捕获数据,将读取的原始捕获数据发送至所述缓存模块进行缓存;

8、所述数据处理模块根据接收的配置参数,从所述缓存模块中读取对应的原始捕获数据进行数据过滤和拼接,生成处理后的捕获数据并通过所述通信模块上传至所述驱动引擎模块。

9、在其中一个实施例中,所述参数处理模块接收的配置参数包括读请求参数,所述数据读取信息包括读请求地址和读请求长度;所述参数处理模块对所述读请求参数进行解析,得到读请求地址和读请求长度发送至所述读写控制模块;所述读写控制模块根据所述读请求地址和读请求长度从所述存储装置中读取相应的原始捕获数据。

10、在其中一个实施例中,所述数据处理模块接收的配置参数包括有效位比特位和帧头信息;所述数据处理模块根据所述有效位比特位对从所述缓存模块中读取的原始捕获数据进行过滤和拼接,得到上行数据,以及根据所述帧头信息对所述上行数据进行重新组帧,得到单比特的捕获数据并通过所述通信模块上传至所述驱动引擎模块。

11、在其中一个实施例中,所述数据处理模块包括读取控制单元、单比特转换单元和单比特上传单元,所述读取控制单元连接所述缓存模块,所述单比特转换单元连接所述缓存模块和所述单比特上传单元,所述单比特上传单元连接所述通信模块;

12、所述读取控制单元用于输出读使能信号至所述缓存模块,以使所述缓存模块逐行输出原始捕获数据,所述单比特转换单元接收所述缓存模块输出的一行原始捕获数据,并根据所述有效位比特位进行过滤重新拼接,将一行原始捕获数据压缩成上行数据发送至所述单比特上传单元;所述单比特上传单元根据所述帧头信息对接收的上行数据进行重新组帧,得到单比特的捕获数据输出至所述通信模块。

13、在其中一个实施例中,所述数据处理模块还包括单比特控制单元,所述单比特控制单元连接所述参数解析模块、所述读取控制单元、所述单比特转换单元和所述单比特上传单元;所述单比特控制单元控制所述读取控制单元输出读使能信号,对所述单比特转换单元配置有效位比特位,以及对所述单比特上传单元配置帧头信息。

14、在其中一个实施例中,所述驱动引擎模块中加载有驱动,所述驱动在需要处理的数据总量满足设定的异步线程开启条件时,通过主线程发送指令至所述硬加速装置,控制所述硬加速装置从存储装置读取相应的原始捕获数据进行过滤和拼接处理;所述驱动还将所述硬加速装置上传处理后的捕获数据存储至消息队列中,所述驱动的多个从线程轮询所述消息队列中数据进行并行加速处理,直至所述消息队列为空。

15、在其中一个实施例中,所述驱动引擎模块基于上位机下发的测试参数确定需要处理的数据总量,若需要处理的数据总量大于或等于预设阈值,则满足异步线程开启条件。

16、在其中一个实施例中,所述需要处理的数据总量为数据总行数,所述预设阈值为预设行数阈值;所述驱动引擎模块在判断满足异步线程开启条件时,结合所述预设行数阈值下发指令至所述硬加速装置,控制所述硬加速装置从所述存储装置中读取与所述预设行数阈值对应行数的原始捕获数据进行过滤和拼接处理,并上传处理后的捕获数据至所述驱动引擎模块。

17、本申请第二方面提供一种测试数据处理方法,包括:

18、硬加速装置根据驱动引擎模块下发的指令确认配置参数;

19、所述硬加速装置根据所述配置参数从存储装置读取相应的原始捕获数据,对读取的原始捕获数据进行过滤和拼接处理,生成处理后的捕获数据发送至驱动引擎模块;

20、所述驱动引擎模块在需要处理的数据总量满足设定的异步线程开启条件时,通过异步线程对接收的捕获数据进行并行加速处理。

21、本申请第三方面提供一种测试机,包括上位机和上述的测试数据处理板卡。

22、上述测试数据处理板卡、方法和测试机,硬加速装置根据驱动引擎模块下发的指令确认配置参数,根据配置参数从存储装置读取相应的原始捕获数据,对读取的原始捕获数据进行过滤和拼接处理,生成处理后的捕获数据发送至驱动引擎模块,完成数据的硬加速处理。驱动引擎模块在需要处理的数据总量满足设定的异步线程开启条件时,通过异步线程对接收的捕获数据进行并行加速处理,实现数据的软加速处理。通过将硬加速和软加速结合的方式进行数据处理,有效提高了数据处理效率。

技术特征:

1.一种测试数据处理板卡,其特征在于,包括驱动引擎模块和硬加速装置,所述硬加速装置与所述驱动引擎模块和存储装置连接;

2.根据权利要求1所述的测试数据处理板卡,其特征在于,所述硬加速装置包括通信模块、参数解析模块、参数处理模块、读写控制模块、缓存模块和数据处理模块,所述通信模块连接驱动引擎模块、所述参数解析模块和所述数据处理模块,所述参数解析模块连接所述参数处理模块和所述数据处理模块,所述读写控制模块连接所述参数处理模块、所述缓存模块和所述存储装置,所述缓存模块连接所述数据处理模块;

3.根据权利要求2所述的测试数据处理板卡,其特征在于,所述参数处理模块接收的配置参数包括读请求参数,所述数据读取信息包括读请求地址和读请求长度;所述参数处理模块对所述读请求参数进行解析,得到读请求地址和读请求长度发送至所述读写控制模块;所述读写控制模块根据所述读请求地址和读请求长度从所述存储装置中读取相应的原始捕获数据。

4.根据权利要求2所述的测试数据处理板卡,其特征在于,所述数据处理模块接收的配置参数包括有效位比特位和帧头信息;所述数据处理模块根据所述有效位比特位对从所述缓存模块中读取的原始捕获数据进行过滤和拼接,得到上行数据,以及根据所述帧头信息对所述上行数据进行重新组帧,得到单比特的捕获数据并通过所述通信模块上传至所述驱动引擎模块。

5.根据权利要求4所述的测试数据处理板卡,其特征在于,所述数据处理模块包括读取控制单元、单比特转换单元和单比特上传单元,所述读取控制单元连接所述缓存模块,所述单比特转换单元连接所述缓存模块和所述单比特上传单元,所述单比特上传单元连接所述通信模块;

6.根据权利要求5所述的测试数据处理板卡,其特征在于,所述数据处理模块还包括单比特控制单元,所述单比特控制单元连接所述参数解析模块、所述读取控制单元、所述单比特转换单元和所述单比特上传单元;所述单比特控制单元控制所述读取控制单元输出读使能信号,对所述单比特转换单元配置有效位比特位,以及对所述单比特上传单元配置帧头信息。

7.根据权利要求1-6任意一项所述的测试数据处理板卡,其特征在于,所述驱动引擎模块中加载有驱动,所述驱动在需要处理的数据总量满足设定的异步线程开启条件时,通过主线程发送指令至所述硬加速装置,控制所述硬加速装置从存储装置读取相应的原始捕获数据进行过滤和拼接处理;所述驱动还将所述硬加速装置上传处理后的捕获数据存储至消息队列中,所述驱动的多个从线程轮询所述消息队列中数据进行并行加速处理,直至所述消息队列为空。

8.根据权利要求1-6任意一项所述的测试数据处理板卡,其特征在于,所述驱动引擎模块基于上位机下发的测试参数确定需要处理的数据总量,若需要处理的数据总量大于或等于预设阈值,则满足异步线程开启条件。

9.根据权利要求8所述的测试数据处理板卡,其特征在于,所述需要处理的数据总量为数据总行数,所述预设阈值为预设行数阈值;所述驱动引擎模块在判断满足异步线程开启条件时,结合所述预设行数阈值下发指令至所述硬加速装置,控制所述硬加速装置从所述存储装置中读取与所述预设行数阈值对应行数的原始捕获数据进行过滤和拼接处理,并上传处理后的捕获数据至所述驱动引擎模块。

10.一种测试数据处理方法,其特征在于,包括:

11.一种测试机,其特征在于,包括上位机和权利要求1-9任意一项所述的测试数据处理板卡。

技术总结

本申请涉及一种测试数据处理板卡、方法和测试机,硬加速装置根据驱动引擎模块下发的指令确认配置参数,根据配置参数从存储装置读取相应的原始捕获数据,对读取的原始捕获数据进行过滤和拼接处理,生成处理后的捕获数据发送至驱动引擎模块;驱动引擎模块在需要处理的数据总量满足设定的异步线程开启条件时,通过异步线程对接收的捕获数据进行并行加速处理。通过将硬加速和软加速结合的方式进行数据处理,有效提高了数据处理效率。

技术研发人员:姜帅,赵飞,马鹤鸣,王宇先

受保护的技术使用者:杭州长川科技股份有限公司

技术研发日:

技术公布日:2025/4/14

- 还没有人留言评论。精彩留言会获得点赞!