一种存储器地址的生成方法、存储控制方法和生成装置与流程

本申请涉及存储控制,具体涉及一种存储器地址的生成方法、存储控制方法和生成装置。

背景技术:

1、现有的车辆soc芯片内部的系统存储器子系统需要有功能安全保护,通常把数据存储到数据存储器的同时,将对应产生的ecc校验码存储到ecc存储器内部。当处理器读取数据存储器内部的数据时,存储控制器同时读取数据存储器和ecc存储器内部的数据和ecc校验码,进行ecc校验。

2、目前,数据存储器的地址是基于总线的地址信号得到的,ecc存储器的地址是基于数据存储器的地址进行逻辑处理得到的,然而,本申请发现,一旦数据存储器和ecc存储器的地址线存在共因失效问题,但是由于存储在ecc存储器中的ecc校验码是基于数据存储器中的数据匹配得到的,因此,很可能存储控制器基于从数据存储器中读取的数据和在ecc存储器中存储的ecc校验码虽然是匹配的,但是由于是从错误的地址取出的数据和ecc校验码,这依然不符合功能安全保护的要求,无法及时地识别出错误数据并进行校正。

技术实现思路

1、针对现有技术中存在的上述技术问题,提出了本申请。本申请旨在提供一种存储器地址的生成方法、存储控制方法和生成装置,其能够避免地址线共因失效的问题,提高功能安全保护的效果。

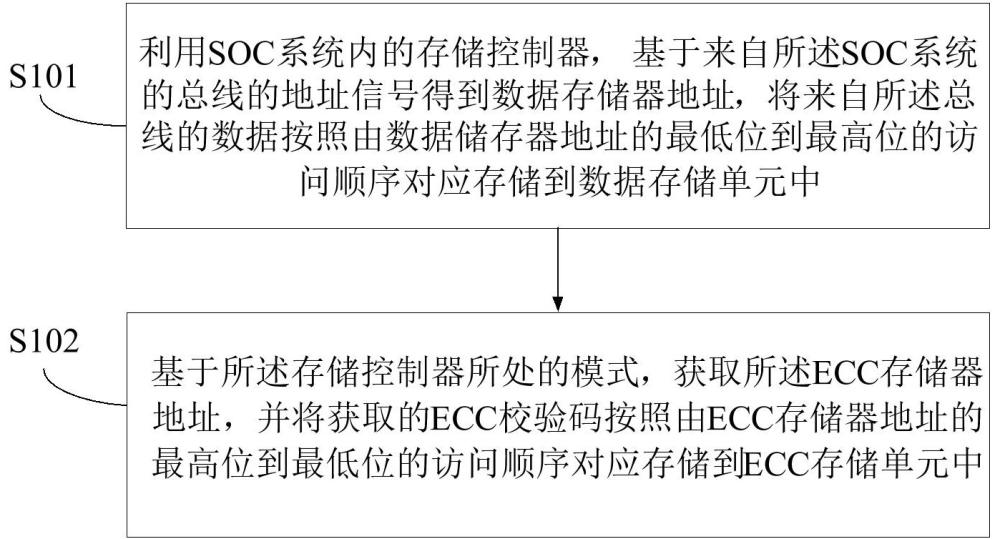

2、根据本申请的第一方案,提供一种存储器地址的生成方法,所述存储器地址包括数据存储器地址和ecc存储器地址,所述生成方法包括:利用soc系统内的存储控制器,基于来自所述soc系统的总线的地址信号得到数据存储器地址,将来自所述总线的数据按照由数据储存器地址的最低位到最高位的访问顺序对应存储到数据存储单元中;基于所述存储控制器所处的模式,获取所述ecc存储器地址,并将获取的ecc校验码按照由ecc存储器地址的最高位到最低位的访问顺序对应存储到ecc存储单元中。

3、根据本申请的第二方案,提供一种基于soc系统的存储控制方法,所述存储控制方法包括:利用soc系统内的存储控制器,基于来自所述soc系统的总线的地址信号得到数据存储器地址,将来自所述总线的数据按照由数据储存器地址的最低位到最高位的访问顺序对应存储到数据存储单元中;基于所述存储控制器所处的模式,获取ecc存储器地址,并将获取的ecc校验码按照由ecc存储器地址的最高位到最低位的访问顺序对应存储到ecc存储单元中;按照由数据储存器地址的最低位到最高位的访问顺序从所述数据存储单元中读取目标数据,并基于读取到的目标数据生成第二ecc校验码;按照由ecc存储器地址的最高位到最低位的访问顺序从所述ecc存储单元中读取第一ecc校验码,通过比较所述第二ecc校验码和第一ecc校验码,来判断所述数据是否存在错误。

4、根据本申请的第三方案,提供一种存储器地址的生成装置,所述存储器地址包括数据存储器地址和ecc存储器地址,所述生成装置包括存储控制器,所述存储控制器包括第一地址译码模块、第二地址译码模块和第二反相器,所述存储控制器配置为:利用所述第一地址译码模块,基于来自所述soc系统的总线的地址信号得到数据存储器地址,将来自所述总线的数据按照由数据储存器地址的最低位到最高位的访问顺序对应存储到数据存储单元中;利用所述第二地址译码模块,根据存储控制器所处的模式,获取所述ecc存储器地址,并利用所述第二反相器,并将获取的ecc校验码按照由ecc存储器地址的最高位到最低位的访问顺序对应存储到ecc存储单元中。

5、根据本申请的第四方案,提供一种soc芯片,所述soc芯片包括存储控制器,所述存储控制器配置为执行本申请各个实施例所述的存储器地址的生成方法。

6、与现有技术相比,本申请实施例的有益效果在于:

7、本申请实施例提供的存储器地址的生成方法,利用存储控制器基于地址信号得到数据存储器地址,该数据存储器地址作为数据存储单元的物理地址,将来自所述总线的数据按照由数据储存器地址的最低位到最高位的访问顺序对应存储到数据存储单元中。并且,利用存储控制器获取ecc存储器地址,并将获取的ecc校验码按照由ecc存储器地址的最高位到最低位的访问顺序对应存储到ecc存储单元中。

8、将ecc校验码按照由ecc存储器地址的最高位到最低位的访问顺序对应存储到ecc存储单元中,相当于将ecc存储器地址取反,如此,通过控制数据存储单元和ecc存储单元的物理地址线的生成阶段,将ecc校验码存储到取反后的ecc存储器地址对应的ecc存储单元中,能够有效避免地址线共因失效问题。

9、而且,存储控制器在访问ecc存储单元时,按照由高位到低位的访问顺序读取ecc校验码,通过比较基于从数据存储单元读取的数据和从ecc存储单元中读取出的ecc校验码,能够准确地判断出存入到数据存储单元中的数据是否存在错误,从而及时地识别出出错的数据,提高功能安全保护的效果。

10、此外,基于本申请的生成方法,将ecc存储器地址取反用于ecc校验码存储,能够使得存储控制器在使能ecc模式和不使能ecc模式之间自由切换,而无需因为两种模式的切换带来额外的处理步骤,增加处理繁琐度。

11、上述说明仅是本申请技术方案的概述,为了能够更清楚了解本申请的技术手段,而可依照说明书的内容予以实施,并且为了让本申请的上述说明和其它目的、特征和优点能够更明显易懂,以下特举本申请的具体实施方式。

技术特征:

1.一种存储器地址的生成方法,其特征在于,所述存储器地址包括数据存储器地址和ecc存储器地址,所述生成方法包括:

2.根据权利要求1所述的生成方法,其特征在于,所述存储控制器支持使能ecc模式和不使能ecc模式,所述生成方法还包括:

3.根据权利要求2所述的生成方法,其特征在于,所述生成方法还包括:

4.根据权利要求2所述的生成方法,其特征在于,在所述存储控制器处于使能ecc模式的情况下,所述存储控制器生成所述数据存储器地址的第一电路,与生成取反的ecc存储器地址的第二电路不能复用。

5.根据权利要求1所述的生成方法,其特征在于,所述生成方法还包括:

6.一种基于soc系统的存储控制方法,其特征在于,所述存储控制方法包括:

7.一种存储器地址的生成装置,其特征在于,所述存储器地址包括数据存储器地址和ecc存储器地址,所述生成装置包括存储控制器,所述存储控制器包括第一地址译码模块、第二地址译码模块和第二反相器,

8.根据权利要求7所述的生成装置,其特征在于,所述存储控制器还配置为:

9.根据权利要求7所述的生成装置,其特征在于,所述存储控制器还包括第一反相器,还配置为:

10.一种soc芯片,其特征在于,所述soc芯片包括存储控制器,所述存储控制器配置为执行权利要求1-4任一项所述的存储器地址的生成方法。

技术总结

本申请提供了一种存储器地址的生成方法、存储控制方法和生成装置。所述生成方法包括利用SOC系统内的存储控制器,基于来自SOC系统的总线的地址信号得到数据存储器地址,将来自总线的数据按照由数据储存器地址的最低位到最高位的访问顺序对应存储到数据存储单元中;基于存储控制器所处的模式,获取ECC存储器地址,并将获取的ECC校验码按照由ECC存储器地址的最高位到最低位的访问顺序对应存储到ECC存储单元中。如此,能够避免地址线的共因失效问题,提高功能安全保护的效果。

技术研发人员:张杰

受保护的技术使用者:深圳砺驰半导体科技有限公司

技术研发日:

技术公布日:2024/12/19

- 还没有人留言评论。精彩留言会获得点赞!