一种仿真验证的加速系统的制作方法

本发明涉及仿真验证,特别是涉及一种仿真验证的加速系统。

背景技术:

1、现有技术中的仿真验证系统包括待测设计和验证组件,待测设计包括1个寄存器通道和若干被测模块,寄存器通道包括若干输入接口和若干输出接口,寄存器通道的每一输出接口连接1个被测模块。在对待测设计进行uvm(universal verificationmethodology,即通用验证方法学)仿真验证时,寄存器通道的每一输入接口连接一个验证组件,每一验证组件发出的请求通过与其连接的输入接口进入寄存器通道,然后经寄存器通道内部的路由之后再从某一输出接口出来,最后发送给与输出接口连接的测试模块。寄存器通道是硬件电路结构,其内包括延时单元等单元,导致验证组件发出的请求从进入寄存器通道至从寄存器通道出来的时间往往较长,导致对测试组件进行仿真验证花费的时间较长。如何减少对待测设计进行仿真验证的时间,进而提高对待测设计进行仿真验证的效率,是亟待解决的问题。

技术实现思路

1、本发明目的在于,提供一种仿真验证的加速系统,以减少对待测设计进行仿真验证的时间,进而提高对待测设计进行仿真验证的效率。

2、根据本发明,提供了一种仿真验证的加速系统,所述系统包括待测设计dut、第一验证组件uvc1和第二验证组件uvc2;uvc1=(uvc1,1,uvc1,2,…,uvc1,k,…,uvc1,m),uvc1,k为第k个第一验证组件,k的取值范围为1到m,m为第一验证组件的数量;uvc2=(uvc2,1,uvc2,2,…,uvc2,i,…,uvc2,n),uvc2,i为第i个第二验证组件,i的取值范围为1到n,n为第二验证组件的数量。

3、dut包括寄存器通道rnoc和被测模块engine,engine=(engine1,engine2,…,enginei,…,enginen),enginei为dut包括的第i个被测模块,enginei与uvc2,i连接;rnoc的输入接口为iniu,iniu=(iniu1,iniu2,…,iniuk,…,inium),iniuk为rnoc的第k个输入接口;rnoc的输出接口为tniu,tniu=(tniu1,tniu2,…,tniui,…,tniun),tniui为rnoc的第i个输出接口,tniui与enginei连接。

4、每一uvc1,k和每一uvc2,i均包括1个序列器。

5、每一uvc1,k的序列器用于在对dut进行仿真验证的过程中发出请求,且在对dut进行仿真验证的过程中每一uvc1,k的序列器发出的请求经序列器映射处理后发送给匹配的第二验证组件的序列器,以使匹配的第二验证组件的序列器在接收到请求之后将请求发送给与匹配的第二验证组件连接的被测模块。

6、本发明与现有技术相比至少具有以下有益效果:

7、本发明的仿真验证的加速系统包括待测设计,还包括第一验证组件和第二验证组件,待测设计包括寄存器通道和被测模块,寄存器通道包括输入接口和输出接口,输出接口的数量等于被测模块的数量,输入接口的数量等于第一验证组件的数量;本发明的加速系统中被测模块的数量还等于第二验证组件的数量,每一被测模块连接1个第二验证组件,不同被测模块连接的第二验证组件不同;本发明的加速系统在对待测设计进行仿真验证时,每一第一验证组件发出的请求不再进入寄存器模块的输入接口,而是经序列器映射处理后发送给匹配的第二验证组件的序列器,再由匹配的第二验证组件的序列器发送给与匹配的第二验证组件连接的被测模块;由此,本发明的加速系统在对待测设计进行仿真验证时不再经过待测设计中的寄存器通道,可以省去请求在寄存器通道中路由的时间;而且,本发明在每一被测模块上连接了第二验证组件,以实现请求从第一验证组件到第二验证组件的传输,进而到与第二验证组件连接的被测模块的传输,该传输路径不再受到寄存器通道中延时单元的影响,对应的传输时间较短,进而减少了对待测设计进行仿真验证的时间,进而提高对待测设计进行仿真验证的效率。

技术特征:

1.一种仿真验证的加速系统,其特征在于,所述系统包括待测设计dut、第一验证组件uvc1和第二验证组件uvc2;uvc1=(uvc1,1,uvc1,2,…,uvc1,k,…,uvc1,m),uvc1,k为第k个第一验证组件,k的取值范围为1到m,m为第一验证组件的数量;uvc2=(uvc2,1,uvc2,2,…,uvc2,i,…,uvc2,n),uvc2,i为第i个第二验证组件,i的取值范围为1到n,n为第二验证组件的数量;

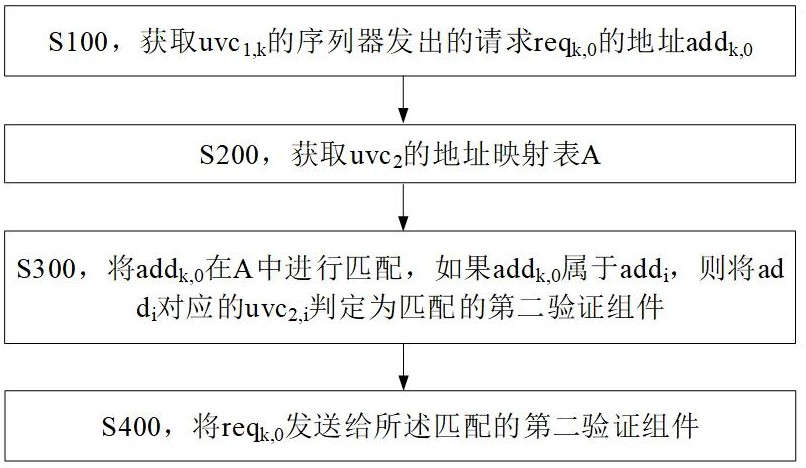

2.根据权利要求1所述的仿真验证的加速系统,其特征在于,所述且在对dut进行仿真验证的过程中每一uvc1,k的序列器发出的请求经序列器映射处理后发送给匹配的第二验证组件的序列器包括:

3.根据权利要求2所述的仿真验证的加速系统,其特征在于,a根据rnoc的地址映射关系得到,rnoc的地址映射关系包括uvc1的序列器发出的请求的地址与tniu的映射关系,如果rnoc的地址映射关系指示某一请求的地址add’与tniui具有映射关系,则a中uvc2,i对应的地址集合addi中包括add’。

4.根据权利要求2所述的仿真验证的加速系统,其特征在于,m≥2,s100还包括:获取reqk,0的保序标签tagk,0,根据tagk,0判断reqk,0是否需要保序,若需要,则将发出reqk,0的序列器判定为目标序列器,且s400还包括:在将reqk,0发送给所述匹配的第二验证组件之后的预设保序时间段内只允许目标序列器向engine发出请求。

5.根据权利要求4所述的仿真验证的加速系统,其特征在于,所述根据tagk,0判断reqk,0是否需要保序包括:如果tagk,0为第一预设值,则判断reqk,0需要保序;如果tagk,0为第二预设值,则判断reqk,0不需要保序。

6.根据权利要求4所述的仿真验证的加速系统,其特征在于,s100还包括:若不需要,则s400还包括:在将reqk,0发送给所述匹配的第二验证组件之后的预设保序时间段内允许任一uvc1,k的序列器向engine发出请求。

7.根据权利要求1所述的仿真验证的加速系统,其特征在于,uvc1,k的序列器sequencerk用于控制sequencek生成的请求是否发出,sequencek为对dut进行仿真验证时用于生成请求并经sequencerk发出的序列,sequencek=(sequencek,1,sequencek,2,…,sequencek,j,…,sequencek,z),sequencek,j为对dut进行仿真验证时用于生成请求并经sequencerk发出的第j个序列,j的取值范围为1到z,z为对dut进行仿真验证时用于生成请求并经sequencerk发出的序列的数量。

技术总结

本申请涉及仿真验证技术领域,特别是涉及一种仿真验证的加速系统。其包括待测设计dut、第一验证组件和第二验证组件;dut包括寄存器通道rnoc和被测模块engine,rnoc的输入接口为iniu,rnoc的输出接口为tniu;每一第一验证组件和每一第二验证组件均包括1个序列器;每一第一验证组件的序列器用于在对dut进行仿真验证的过程中发出请求,且在对dut进行仿真验证的过程中每一第一验证组件的序列器发出的请求经序列器映射处理后发送给匹配的第二验证组件的序列器,以使匹配的第二验证组件的序列器在接收到请求之后将请求发送给与匹配的第二验证组件连接的被测模块。本发明能提高对待测设计进行仿真验证的效率。

技术研发人员:黄建,邹俊俊,陈磊

受保护的技术使用者:沐曦集成电路(上海)有限公司

技术研发日:

技术公布日:2024/12/30

- 还没有人留言评论。精彩留言会获得点赞!