一种提高信号可靠性的方法、电路、设备以及介质与流程

本公开一般涉及航空计算机,具体涉及一种提高信号可靠性的方法、电路、设备以及介质。

背景技术:

1、离散量信号在航空领域中扮演着至关重要的角色,因为它们以数字形式传输,能够提供稳定、可靠的信号,用于控制和监测飞机的各种系统和功能。

2、同时,离散量信号属于机载常用的数字信号,接收端通过高低电平以及事先约定的含义判断事件是否有效,该方法电路简单、电路成本低,被大量应用于设备内部或设备之间通信。

3、一般离散量通过1bit数据进行发送或接收,由于传输线间相互耦合或外部干扰,通过单独一个信号判断事件是否有效显然不是十分可靠,尤其针对涉及人员安全或任务安全的关键重要信号时,所以亟需一种提高信号可靠性的方法,保证离散量信号的安全可靠。

技术实现思路

1、鉴于现有技术中的上述缺陷或不足,期望提供一种提高信号可靠性的方法、电路、设备以及介质。

2、第一方面,本申请提供一种提高信号可靠性的方法,包括:

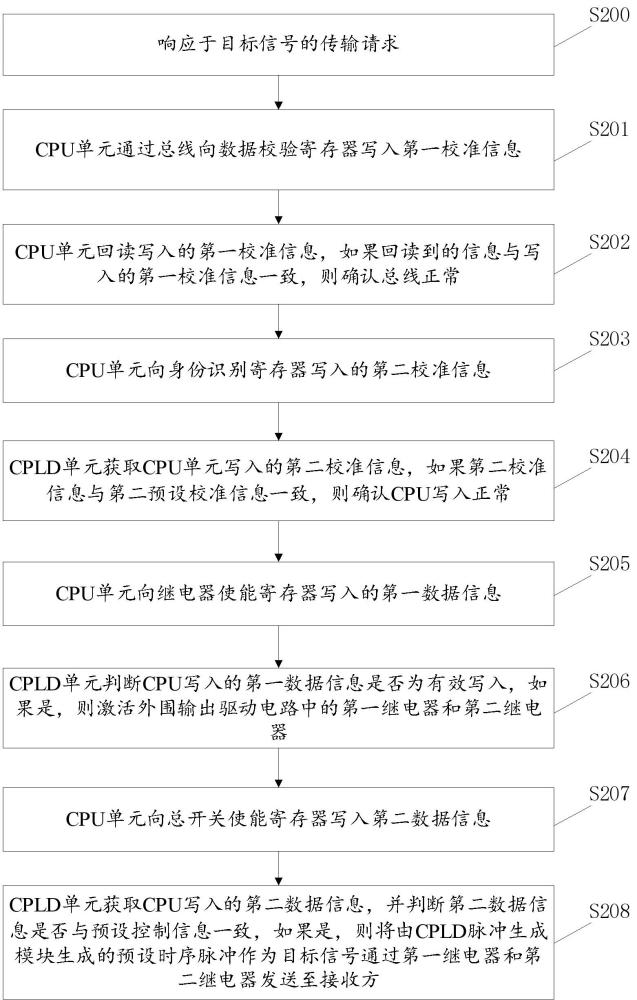

3、响应于目标信号的传输请求;

4、判断cpu向继电器使能寄存器写入的第一数据信息是否为有效写入;

5、如果是,则激活外围输出驱动电路中的第一继电器和第二继电器;

6、获取所述cpu向总开关使能寄存器写入的第二数据信息,并判断所述第二数据信息是否与预设控制信息一致;

7、如果是,则将由cpld脉冲生成模块生成的预设时序脉冲作为目标信号通过所述第一继电器和所述第二继电器发送至接收方。

8、根据本申请提供的技术方案,判断cpu向继电器使能寄存器写入的第一数据信息是否为有效写入之前,还包括:

9、由所述cpu回读其通过总线向数据校验寄存器写入的第一校准信息,如果读取到的信息与写入的所述第一校准信息一致,则确认总线正常;

10、根据本申请提供的技术方案,在确认总线正常之后,且在判断cpu向继电器使能寄存器写入的第一数据信息是否为有效写入之前,还包括:

11、获取所述cpu向身份识别寄存器写入的第二校准信息,如果所述第二校准信息与所述第二预设校准信息一致,则确认所述cpu写入正常。

12、根据本申请提供的技术方案,所述继电器使能寄存器包括:两个独立控制的第一继电器使能寄存器和第二继电器使能寄存器;所述第一数据信息包括:分别写入第一继电器使能寄存器和第二继电器使能寄存器的两个子数据信息;

13、判断cpu向继电器使能寄存器写入的第一数据信息是否为有效写入,具体包括:

14、获取写入所述第一继电器使能寄存器和所述第二继电器使能寄存器的所述子数据信息;

15、当两个所述子数据信息与对应的预设使能信息均一致时,则确认所述cpu向继电器使能寄存器写入的第一数据信息为有效写入。

16、根据本申请提供的技术方案,激活外围输出驱动电路中的第一继电器和第二继电器,具体包括:

17、向外围输出驱动电路发送使能信号,控制所述外围驱动电路为所述第一继电器和第二继电器提供电流,使得所述第一继电器和所述第二继电器吸合,进入激活状态。

18、根据本申请提供的技术方案,所述cpld脉冲生成模块生成有第一脉冲序列和第二脉冲序列;

19、将由cpld脉冲生成模块生成的预设时序脉冲作为目标信号发送至接收方,具体包括:

20、按照预设时序发送所述第一脉冲序列和所述第二脉冲序列;所述第一脉冲序列和所述第二脉冲序列具有不同的脉冲宽度和周期。

21、第二方面,本申请提供一种提高信号可靠性的电路,应用有上述的一种提高信号可靠性的方法,所述电路包括:

22、相互通讯联通的cpu单元和cpld单元;

23、所述cpld单元至少具有通过内部逻辑可实现的接口通信模块、cpld脉冲生成模块、可信度认证模块、输出控制使能模块;

24、输出驱动电路,所述输出驱动电路包括:目标信号传输支路、独立控制的第一继电器驱动支路与第二继电器驱动支路。

25、根据本申请提供的技术方案,所述目标信号传输支路包括:与所述cpld单元顺次串联的所述第一继电器和所述第二继电器,用于向接收方传输目标信号;

26、所述第一继电器驱动支路一端与所述cpld单元相连接,另一端与所述第一继电器相连接;所述第二继电器驱动支路一端与所述cpld单元相连接,另一端与所述第二继电器相连接;

27、所述第一继电器驱动支路与第二继电器驱动支路分别用于激活所述第一继电器和所述第二继电器。

28、第三方面,本申请提供一种终端设备,包括存储器、处理器以及存储在所述存储器中并可在所述处理器上运行的计算机程序,其特征在于,所述处理器执行所述计算机程序时实现如上述的一种提高信号可靠性的方法的步骤。

29、第四方面,本申请提供一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现如上述的一种提高信号可靠性的方法的步骤。

30、综上所述,本技术方案具体地公开了一种提高信号可靠性的方法、电路、设备以及介质。其中,该方法包括:判断cpu向继电器使能寄存器写入的第一数据信息是否为有效写入;如果是,则激活外围输出驱动电路中的第一继电器和第二继电器;获取所述cpu向总开关使能寄存器写入的第二数据信息,并判断所述第二数据信息是否与预设控制信息一致;如果是,则将由cpld脉冲生成模块生成的预设时序脉冲作为目标信号发送至接收方。

31、现有的离散量一般通过1bit数据进行发送或接收,由于传输线间相互耦合或外部干扰,通过单独一个信号判断事件是否有效显然不是十分可靠,尤其针对涉及人员安全或任务安全的关键重要信号时,本申请通过cpu对继电器使能寄存器的有效写入,可以激活外部电磁继电器物理开关,通过cpu向总开关使能寄存器的特定写入,可以控制cpld 内部逻辑总开关和2个逻辑分开关,基于这三个逻辑开关通过严格的时序关系组合起来,进而保证输出的目标信号是在正常可控范围内发出,提高关键信号的输出可靠性。

技术特征:

1.一种提高信号可靠性的方法,其特征在于,包括:

2.根据权利要求1所述的一种提高信号可靠性的方法,其特征在于,判断cpu向继电器使能寄存器写入的第一数据信息是否为有效写入之前,还包括:

3.根据权利要求2所述的一种提高信号可靠性的方法,其特征在于,在确认总线正常之后,且在判断cpu向继电器使能寄存器写入的第一数据信息是否为有效写入之前,还包括:

4.根据权利要求1所述的一种提高信号可靠性的方法,其特征在于,所述继电器使能寄存器包括:两个独立控制的第一继电器使能寄存器和第二继电器使能寄存器;所述第一数据信息包括:分别写入第一继电器使能寄存器和第二继电器使能寄存器的两个子数据信息;

5.根据权利要求4所述的一种提高信号可靠性的方法,其特征在于,激活外围输出驱动电路中的第一继电器和第二继电器,具体包括:

6.根据权利要求1所述的一种提高信号可靠性的方法,其特征在于,所述cpld脉冲生成模块生成有第一脉冲序列和第二脉冲序列;

7.一种提高信号可靠性的电路,其特征在于,应用有上述权利要求1-6任一项所述的一种提高信号可靠性的方法,所述电路包括:

8.根据权利要求7所述的一种提高信号可靠性的电路,其特征在于,所述目标信号传输支路包括:与所述cpld单元(2)顺次串联的所述第一继电器(4)和所述第二继电器(5),用于向接收方传输目标信号;

9.一种终端设备,包括存储器、处理器以及存储在所述存储器中并可在所述处理器上运行的计算机程序,其特征在于,所述处理器执行所述计算机程序时实现如权利要求1至6任一项所述的一种提高信号可靠性的方法的步骤。

10.一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现如权利要求1-6任一项所述的一种提高信号可靠性的方法的步骤。

技术总结

本申请公开了一种提高信号可靠性的方法、电路、设备以及介质,涉及航空计算机技术领域,其中,该方法包括:判断CPU向继电器使能寄存器写入的第一数据信息是否为有效写入;如果是,则激活外围输出驱动电路中的第一继电器和第二继电器;获取所述CPU向总开关使能寄存器写入的第二数据信息,并判断所述第二数据信息是否与预设控制信息一致;如果是,则将由CPLD脉冲生成模块生成的预设时序脉冲作为目标信号发送至接收方,采用脉冲信号代替高低电平作为有效信号。该方法了可以避免导线串扰、干扰或者软件跑飞导致的误触发,进而提高信号传输的可靠性。

技术研发人员:张军,刘勇,韩旭

受保护的技术使用者:天津津航计算技术研究所

技术研发日:

技术公布日:2025/3/10

- 还没有人留言评论。精彩留言会获得点赞!