一种基于FPGA的同步串口装置的制作方法

本技术涉及同步串行通信,尤其公开了一种基于fpga的同步串口装置。

背景技术:

1、并行传输指的是数据以成组的方式,在多条并行信道上同时进行传输,是在传输中有多个数据位同时在设备之间进行的传输。但是并行传输通信成本高,每位传输要求一个单独的信道支持,因此如果一个字符包含8个二进制位,则并行传输要求8个独立的信道支持。

2、因此,现有并行传输装置存在的通信成本高,是目前亟待解决的技术问题。

技术实现思路

1、本实用新型提供了一种基于fpga的同步串口装置,旨在解决现有并行传输装置存在的通信成本高的技术问题。

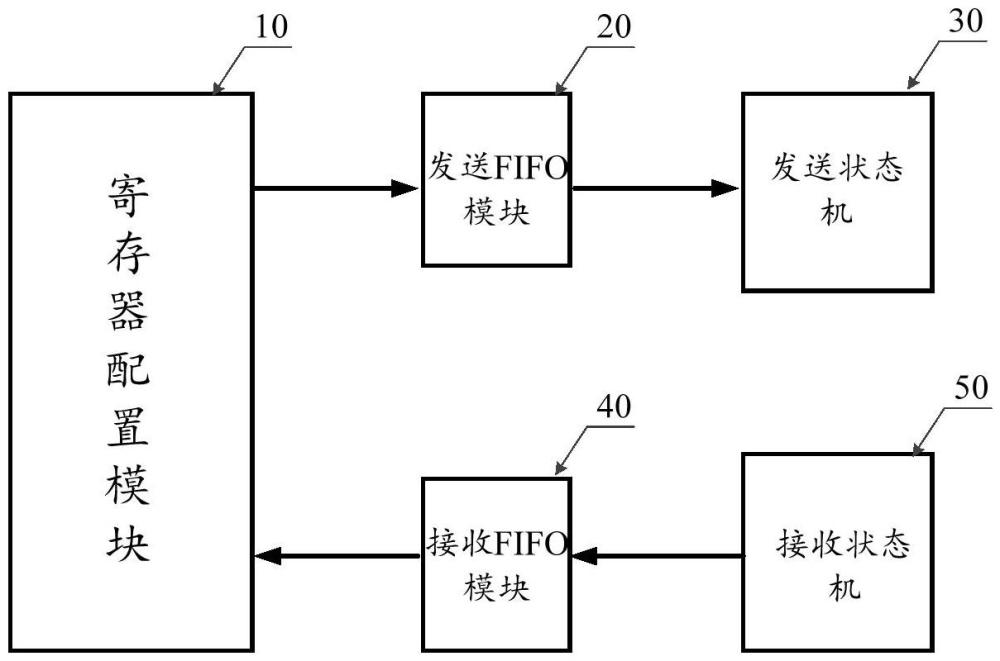

2、本实用新型涉及一种基于fpga的同步串口装置,包括寄存器配置模块、发送fifo模块、发送状态机、接收fifo模块和接收状态机,其中,存器配置模块通过发送fifo模块与发送状态机相连接,存器配置模块通过接收fifo模块与接收状态机相连接。

3、进一步地,寄存器配置模块包括移位寄存器、读数据寄存器、写数据寄存器和cpu,cpu分别与移位寄存器、读数据寄存器和写数据寄存器相连接。

4、进一步地,寄存器配置模块包括fpga芯片。

5、进一步地,fpga芯片的型号为fmql45t900。

6、进一步地,发送fifo模块包括发送fifo芯片。

7、进一步地,接收fifo模块包括接收fifo芯片。

8、进一步地,发送fifo芯片和接收fifo芯片的型号均为jmax4754。

9、进一步地,发送状态机包括发送状态机芯片。

10、进一步地,接收状态机包括接收状态机芯片。

11、进一步地,发送状态机芯片和接收状态机芯片的型号均为jm3096w。

12、本实用新型所取得的有益效果为:

13、本实用新型提供一种基于fpga的同步串口装置,采用寄存器配置模块、发送fifo模块、发送状态机、接收fifo模块和接收状态机,其中,存器配置模块通过发送fifo模块与发送状态机相连接,存器配置模块通过接收fifo模块与接收状态机相连接,寄存器配置模块用于向发送fifo模块发送数据,启动发送状态机;还用于从接收fifo模块中读取接收状态机发送过来的数据。本实用新型提供的基于fpga的同步串口装置,电路简单,成本低;采用同步串口的通信方式,传送信息的位数几乎不受限制,一次通信传输的数据有几十到几千个字节,通信效率较高,适用于大数据量的传输。

技术特征:

1.一种基于fpga的同步串口装置,其特征在于,包括寄存器配置模块(10)、发送fifo模块(20)、发送状态机(30)、接收fifo模块(40)和接收状态机(50),其中,所述存器配置模块(10)通过所述发送fifo模块(20)与所述发送状态机(30)相连接,所述存器配置模块(10)通过所述接收fifo模块(40)与所述接收状态机(50)相连接。

2.如权利要求1所述的基于fpga的同步串口装置,其特征在于,所述寄存器配置模块(10)包括移位寄存器、读数据寄存器、写数据寄存器和cpu,所述cpu分别与所述移位寄存器、所述读数据寄存器和所述写数据寄存器相连接。

3.如权利要求2所述的基于fpga的同步串口装置,其特征在于,所述寄存器配置模块(10)包括fpga芯片。

4.如权利要求3所述的基于fpga的同步串口装置,其特征在于,所述fpga芯片的型号为fmql45t900。

5.如权利要求1所述的基于fpga的同步串口装置,其特征在于,所述发送fifo模块(20)包括发送fifo芯片。

6.如权利要求5所述的基于fpga的同步串口装置,其特征在于,所述接收fifo模块(40)包括接收fifo芯片。

7.如权利要求6所述的基于fpga的同步串口装置,其特征在于,所述发送fifo芯片和所述接收fifo芯片的型号均为jmax4754。

8.如权利要求1所述的基于fpga的同步串口装置,其特征在于,所述发送状态机(30)包括发送状态机芯片。

9.如权利要求8所述的基于fpga的同步串口装置,其特征在于,所述接收状态机(50)包括接收状态机芯片。

10.如权利要求9所述的基于fpga的同步串口装置,其特征在于,所述发送状态机芯片和所述接收状态机芯片的型号均为jm3096w。

技术总结

本技术公开了一种基于FPGA的同步串口装置,采用寄存器配置模块、发送FIFO模块、发送状态机、接收FIFO模块和接收状态机,其中,存器配置模块通过发送FIFO模块与发送状态机相连接,存器配置模块通过接收FIFO模块与接收状态机相连接。本技术提供的基于FPGA的同步串口装置,电路简单,成本低;采用同步串口的通信方式,传送信息的位数几乎不受限制,一次通信传输的数据有几十到几千个字节,通信效率较高,适用于大数据量的传输。

技术研发人员:吕剑维,李雪

受保护的技术使用者:湖南泽天智航电子技术有限公司

技术研发日:20240110

技术公布日:2024/12/10

- 还没有人留言评论。精彩留言会获得点赞!