测试系统以及测试方法与流程

本发明涉及一种测试技术,尤其涉及一种用于测试存储器电路的测试系统以及测试方法。

背景技术:

1、随着科技的发展,电子装置中存储器数量越来越多。然而,由于制程或其他因素,存储器可能会存在缺陷。在一些相关技术中,可利用测试电路对存储器进行测试来确认存储器是否存在缺陷。

技术实现思路

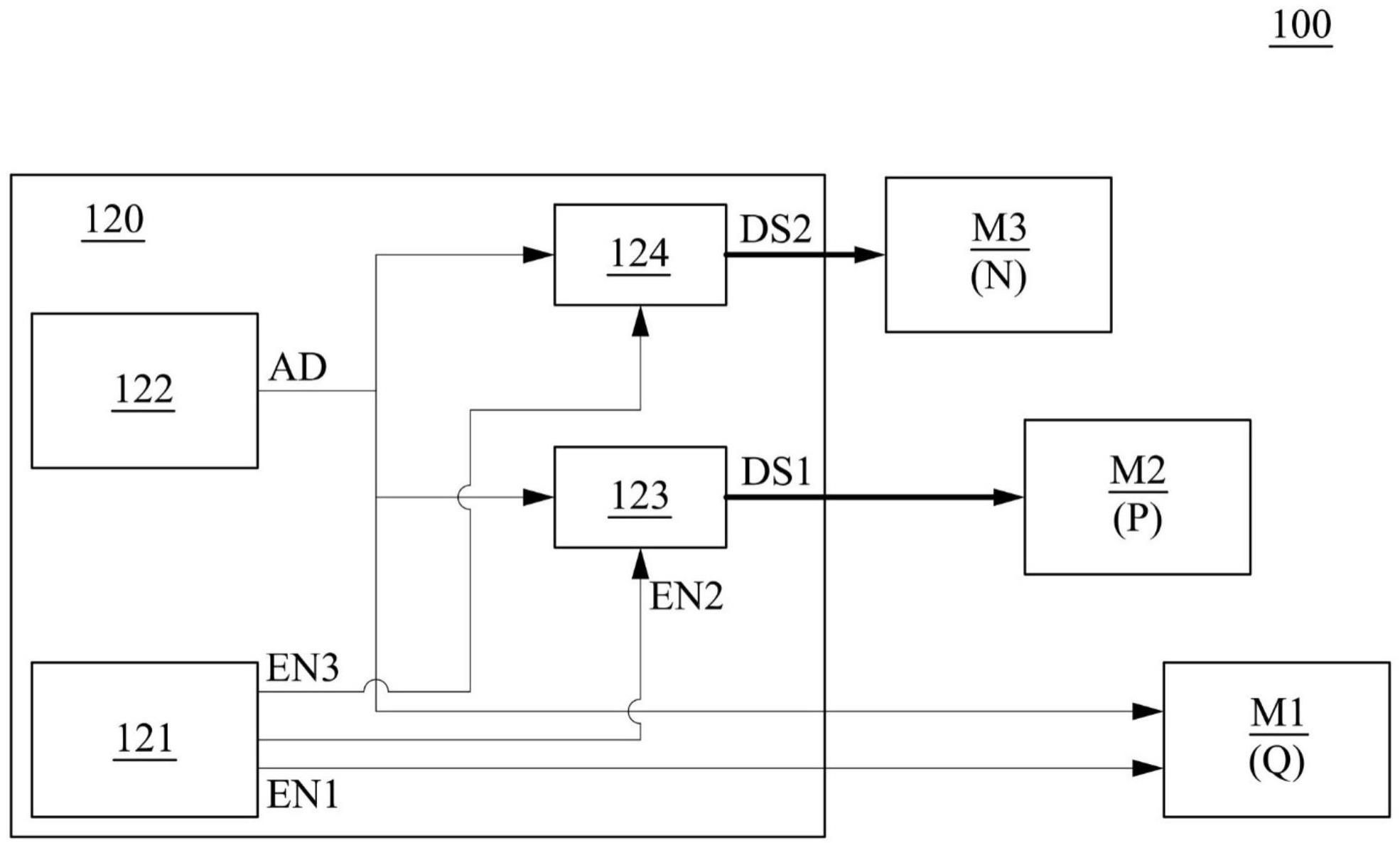

1、本发明的一些实施方式涉及一种测试系统。测试系统包括多个存储器电路以及一测试电路。测试电路耦接这些存储器电路。测试电路用于对这些存储器电路执行一读写操作,且这些存储器电路各自具有对应于读写操作的一读写起始时间点。测试电路还用于控制这些存储器电路的这些读写起始时间点为彼此相异。

2、本发明的一些实施方式涉及一种测试方法。测试方法包括以下操作:通过一测试电路对多个存储器电路执行一读写操作,其中这些存储器电路各自具有对应于读写操作的一读写起始时间点;以及通过测试电路控制这些存储器电路的这些读写起始时间点为彼此相异。

3、综上所述,在本发明中,利用单个测试电路对多个存储器电路进行测试,且测试电路可错开这些存储器电路的读写起始时间点。据此,本发明可在不(或少量)增加测试电路所占据的电路面积且不增加测试时间的情况下,避免瞬间压降过大,以确保电路可正常运行。

技术特征:

1.一种测试系统,包括:

2.根据权利要求1所述的测试系统,其特征在于,所述多个存储器电路包括一第一存储器电路以及一第二存储器电路,其中所述第一存储器电路的一存储容量大于所述第二存储器电路的一存储容量,且所述第一存储器电路的所述读写起始时间点早于所述第二存储器电路的所述读写起始时间点。

3.根据权利要求2所述的测试系统,其特征在于,所述第二存储器电路对应于所述读写操作的一读写结束时间点相同于或早于所述第一存储器电路对应于所述读写操作的一读写结束时间点。

4.根据权利要求2所述的测试系统,其特征在于,所述测试电路包括:

5.根据权利要求4所述的测试系统,其特征在于,所述第一偏移电路用于比较所述地址信号所携带的一地址值与一偏移值,其中当所述地址值等于所述偏移值时,所诉第一偏移电路根据所述第二使能信号以及所述地址信号产生该第一偏移信号来对所述第二存储器电路执行所述读写操作。

6.根据权利要求5所述的测试系统,其特征在于,所述第一偏移电路包括:

7.根据权利要求4所述的测试系统,其特征在于,所述第二存储器电路具有对应于所述读写操作的一读写结束时间点,且所述第二使能信号在所述第二存储器电路的所述读写结束时间点具有一禁能电平。

8.根据权利要求4所述的测试系统,其特征在于,所述第一存储器电路具有对应于所述读写操作的一读写结束时间点,且所述第二使能信号在所述第一存储器电路的所述读写结束时间点具有一禁能电平。

9.根据权利要求4所述的测试系统,其特征在于,所述多个存储器电路还包括一第三存储器电路,其中所述使能信号产生电路还用于产生一第三使能信号,其中所述测试电路还包括:

10.一种测试方法,包括:

技术总结

本发明提供一种测试系统,其包括多个存储器电路以及一测试电路。测试电路耦接这些存储器电路。测试电路用于对这些存储器电路执行一读写操作,且这些存储器电路各自具有对应于读写操作的一读写起始时间点。测试电路还用于控制这些存储器电路的这些读写起始时间点为彼此相异。

技术研发人员:林士杰,林盛霖,邓力玮

受保护的技术使用者:瑞昱半导体股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!