一种具有多级缓存的处理器以及电子设备的制作方法

本申请涉及通信,尤其涉及一种具有多级缓存的处理器以及电子设备。

背景技术:

1、随着摩尔定律下晶体管技术的进一步微缩,片上系统(system on chip,soc)内的静态随机存储器(static random access memory,sram)缓存所占的比例和能耗逐渐成为限制计算性能和功耗的显著瓶颈。sram存储单元由六个晶体管组成,在晶体管技术平面像finfet技术转移后的亚14纳米工艺时代,sram的面积通常能占据整个soc芯片的一半以上,但仍然不能满足许多对计算性能要求较高的场景的需求,同时sram的功耗特别是空闲时漏电造成的静态功耗随着工艺节点的演进越来越严重,也越来越制约着芯片的功耗优化空间。

技术实现思路

1、本申请实施例提供一种具有多级缓存的处理器以及电子设备,用以降低处理器功耗,并实现较高的性价比。

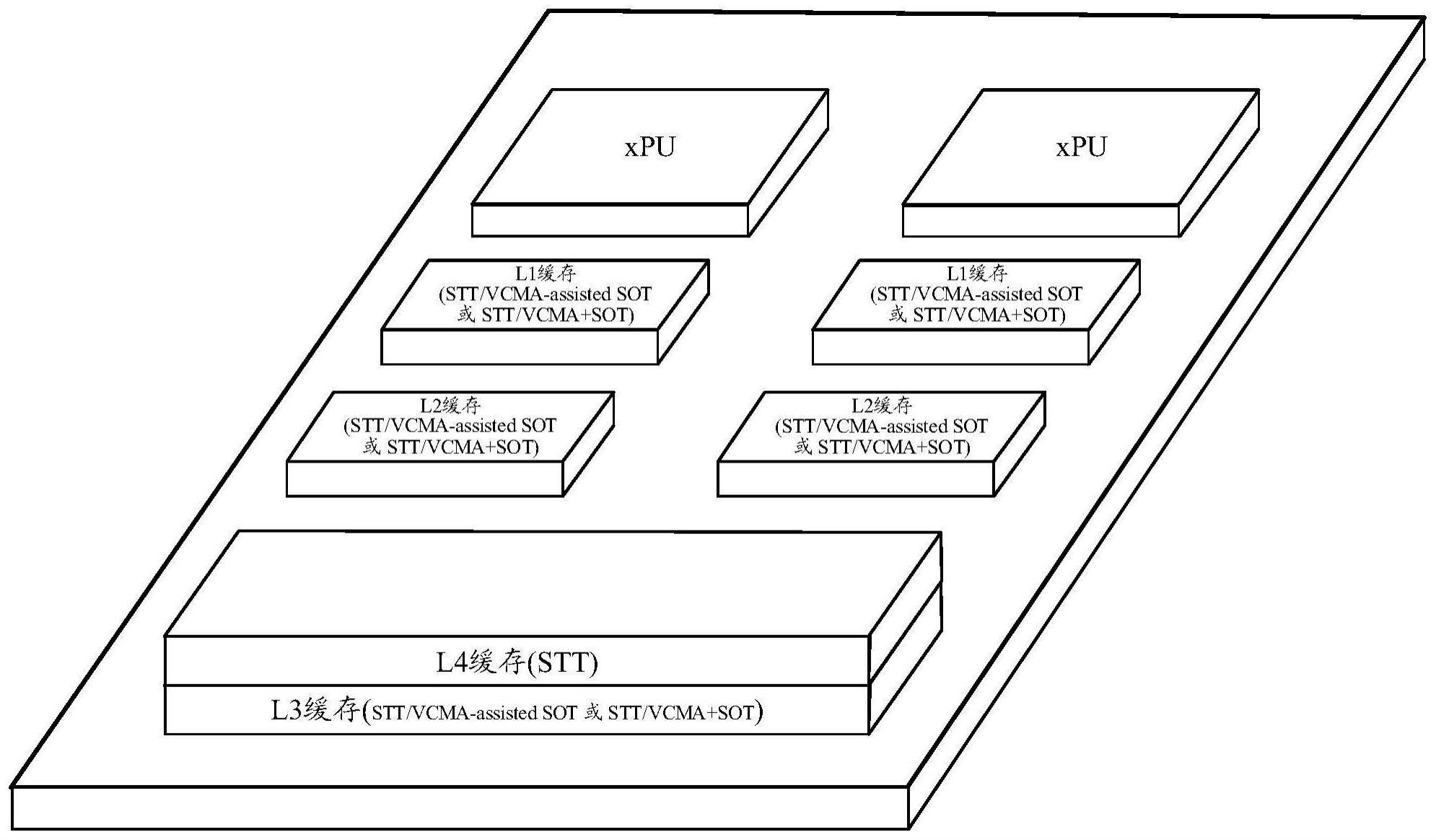

2、第一方面,提供一种具有多级缓存的处理器,包括:至少一个处理器核,任意一个所述处理器核具有n级缓存模块,所述n级缓存模块包括第一级缓存模块、最后一级缓存模块,以及介于所述第一级缓存模块和所述最后一级缓存模块的中间级缓存模块,n为大于1的整数;对于任意一个所述处理器核:

3、所述第一级缓存模块和所述中间级缓存模块中的任意一个缓存模块包括自旋轨道转换磁性随机存储器(sot-mram)存储单元阵列或包括vgsot-mram存储单元阵列或包括stt-assisted sot的mram存储单元阵列,所述vgsot-mram存储单元为具有电压控制磁性各向异性vcma效应的sot-mram存储单元;

4、所述最后一级缓存模块叠加于所述中间级缓存模块,所述最后一级缓存模块包括stt-mram存储单元阵列。

5、可选的,所述中间级缓存模块(例如第n-1级缓存模块)以及所述最后一级缓存模块为至少两个处理器核共享的缓存模块,其余缓存模块为处理器核专属(独享)的缓存模块。

6、上述实现方式中,一方面,各级缓存模块均使用mram器件,由于mram属于非易失性存储器件,因此不存在空闲状态下的漏电和需要刷新的问题,因此相较于易失性存储器(如sram、dram和edram等)可以降低功耗;另一方面,由于最后一级缓存模块叠加在中间级缓存模块上,可以节省处理器空间;再一方面,上述实现方式可根据不同级缓存的性能和容量要求,结合不同类型mram存储单元的特点,使得各级缓存模块采用适宜类型的mram存储单元,以实现处理器从整体上在性能、容量和成本上实现较高的性价比。例如,所述处理器中,第n-1级缓存模块以及最后一级缓存模块为至少两个处理器核共享的缓存模块,其余缓存模块为处理器核专属的缓存模块。由于处理器核专属的缓存模块对性能要求较高,因此可使用vgsot-mram存储单元阵列实现,从而基于vgsot-mram存储单元性能高且存储密度也较高的特点,满足专属缓存模块的性能要求;由于处理器核共享的缓存模块对容量要求较高,因此使用stt-mram存储单元阵列实现,基于stt-mram存储单元存储容量较高且成本较低的特点,使得共享缓存模块的存储容量满足要求,并且从处理器整体上可以兼顾生产成本,达到较高的性价比。

7、在一种可能的实现方式中,所述最后一级缓存模块在所述中间级缓存模块的后道金属工艺中制备形成。通过在后道金属层中插入stt-mram存储单元,对处理器(芯片)面积开销没有增加或者没有显著增加,并且工艺简单易行。

8、在一种可能的实现方式中,所述最后一级缓存模块包括至少两个堆叠封装的stt-mram存储器,所述stt-mram存储器中包括stt-mram存储单元阵列。

9、在一种可能的实现方式中,所述最后一级缓存模块的stt-mram存储单元阵列中包括至少一层stt-mram存储单元。由于最后一级缓存模块的stt-mram存储单元阵列中可包括多层stt-mram存储单元,因此可以进一步提高存储容量。

10、在一种可能的实现方式中,所述最后一级缓存模块,以及所述中间缓存模块中所述最后一级缓存模块的前级缓存模块分别为独立存储器,所述最后一级缓存模块和所述前级缓存模块堆叠封装。

11、在一种可能的实现方式中,所述stt-mram存储单元阵列中的任意一个stt-mram存储单元,包括磁性隧道结(mtj)以及与所述mtj电性耦接的选通单元。

12、可选的,所述选通单元由具有开关特性的单层薄膜实现。

13、由于选通单元可以有某种具有开关特性的单层薄膜实现,这样可以降低制备复杂度。

14、在一种可能的实现方式中,所述选通单元为沟道晶体管。

15、在一种可能的实现方式中,所述第一级缓存模块以及所述中间级缓存模块均由vgsot-mram或者stt-assited sot存储单元阵列实现。

16、在一种可能的实现方式中,所述n级缓存模块包括第一级缓存模块、第二级缓存模块、第三级缓存模块、第四级缓存模块。

17、第二方面,提供一种电子设备,该电子设备包括如上述第一方面中任一项所述的处理器。

技术特征:

1.一种具有多级缓存的处理器,其特征在于,包括:至少一个处理器核,任意一个所述处理器核具有n级缓存模块,所述n级缓存模块包括第一级缓存模块、最后一级缓存模块,以及介于所述第一级缓存模块和所述最后一级缓存模块的中间级缓存模块,n为大于1的整数;对于任意一个所述处理器核:

2.如权利要求1所述的处理器,其特征在于,所述最后一级缓存模块在所述中间级缓存模块的后道金属工艺中制备形成。

3.如权利要求1-2任一项所述的处理器,其特征在于,所述最后一级缓存模块包括至少两个堆叠封装的stt-mram存储器,所述stt-mram存储器中包括stt-mram存储单元阵列。

4.如权利要求1-3任一项所述的处理器,其特征在于,所述最后一级缓存模块的stt-mram存储单元阵列中包括至少一层stt-mram存储单元。

5.如权利要求1-4任一项所述的处理器,其特征在于,所述最后一级缓存模块,以及所述中间缓存模块中所述最后一级缓存模块的前级缓存模块分别为独立存储器,所述最后一级缓存模块和所述前级缓存模块堆叠封装。

6.如权利要求1-5任一项所述的处理器,其特征在于,所述stt-mram存储单元阵列中的任意一个stt-mram存储单元,包括磁性隧道结mtj以及与所述mtj电性耦接的选通单元。

7.如权利要求6所述的处理器,其特征在于,所述选通单元由具有开关特性的单层薄膜实现。

8.如权利要求6所述的处理器,其特征在于,所述选通单元为沟道晶体管。

9.如权利要求1-8任一项所述的处理器,其特征在于,所述第一级缓存模块以及所述中间级缓存模块均由vgsot-mram或者stt-assited sot存储单元阵列实现。

10.如权利要求1-9任一项所述的处理器,其特征在于,所述n级缓存模块包括第一级缓存模块、第二级缓存模块、第三级缓存模块、第四级缓存模块。

11.一种电子设备,其特征在于,包括如权利要求1-10任一项所述的处理器。

技术总结

一种具有多级缓存的处理器以及电子设备。至少一个处理器核,任意一个所述处理器核具有N级缓存模块,所述N级缓存模块包括第一级缓存模块、最后一级缓存模块,以及介于所述第一级缓存模块和所述最后一级缓存模块的中间级缓存模块,N为大于1的整数;对于任意一个所述处理器核:所述第一级缓存模块和所述中间级缓存模块中的任意一个缓存模块包括SOT‑MRAM存储单元阵列或包括VGSOT‑MRAM存储单元阵列或包括STT‑assisted SOT的MRAM存储单元阵列;所述最后一级缓存模块叠加于所述中间级缓存模块,所述最后一级缓存模块包括STT‑MRAM存储单元阵列。

技术研发人员:陈伟,朱晓明

受保护的技术使用者:华为技术有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!