半导体存储装置的制作方法

本实施方式涉及半导体存储装置。

背景技术:

1、已知有具备存储单元阵列和多个感测放大器单元的半导体存储装置,该存储单元阵列具备多个存储单元及与多个存储单元连接的多个位线,该多个感测放大器单元与多个位线分别连接。

技术实现思路

1、本实施方式提供能够良好地进行控制的半导体存储装置。

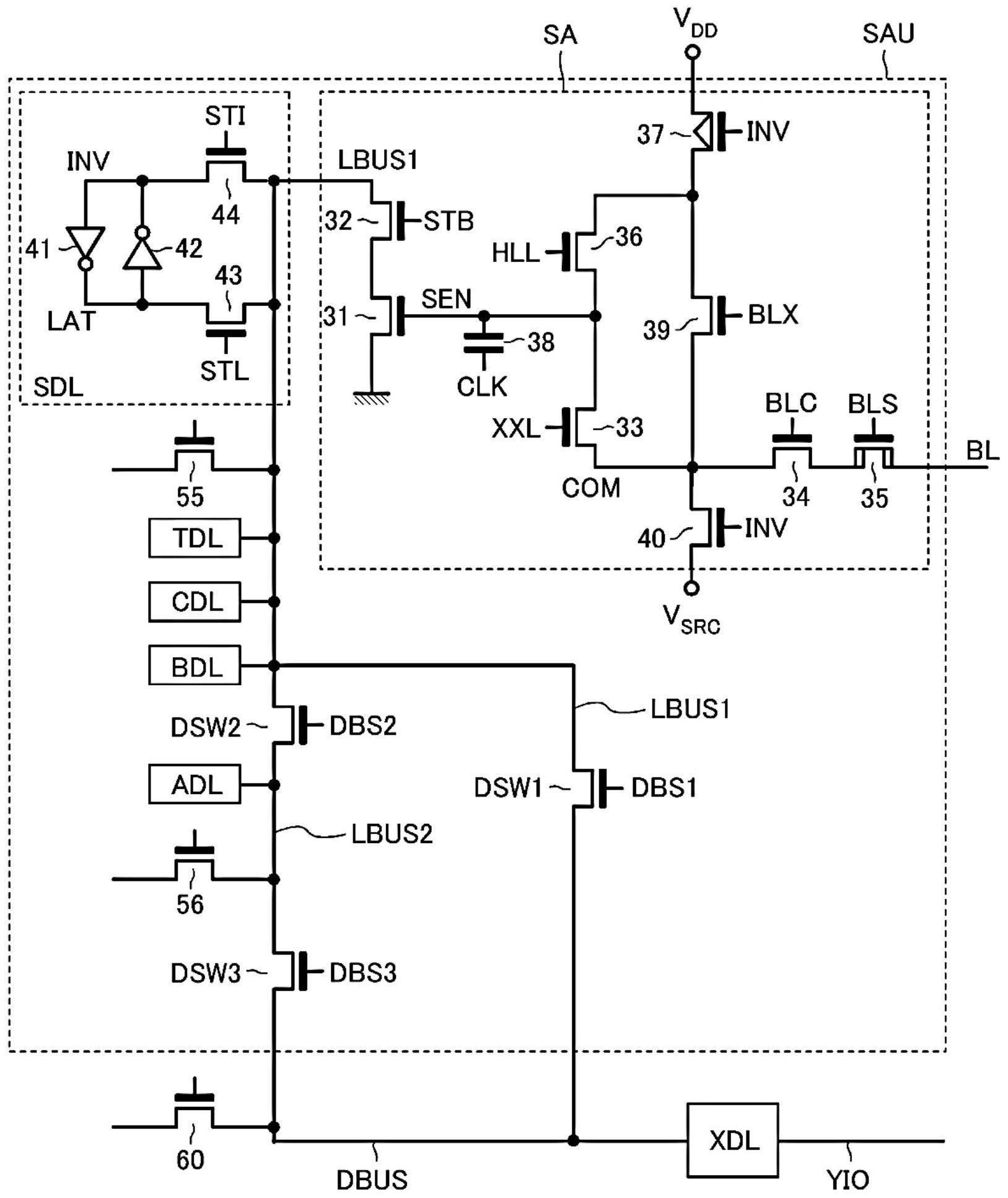

2、一个实施方式所涉及的半导体存储装置具备:存储串;与存储串连接的位线;与位线连接的感测放大器;与感测放大器电连接的第一锁存电路、第二锁存电路、第三锁存电路以及第四锁存电路;与感测放大器、第一锁存电路以及第二锁存电路连接的第一布线;与第三锁存电路连接的第二布线;与第四锁存电路连接的第三布线;将第一布线与第三布线可电断开地连接的第一开关晶体管;将第一布线与第二布线可电断开地连接的第二开关晶体管;以及将第二布线与第三布线可电断开地连接的第三开关晶体管。

技术特征:

1.一种半导体存储装置,具备:

2.根据权利要求1所述的半导体存储装置,其中,

3.根据权利要求2所述的半导体存储装置,其中,

4.根据权利要求1所述的半导体存储装置,其中,

5.根据权利要求1至4中任一项所述的半导体存储装置,其中,

6.根据权利要求1至4中任一项所述的半导体存储装置,其中,

7.根据权利要求1至4中任一项所述的半导体存储装置,其中,

8.根据权利要求7所述的半导体存储装置,其中,

技术总结

实施方式提供能够良好地进行控制的半导体存储装置。一个实施方式的半导体存储装置具备:存储串;与存储串连接的感测放大器;第一锁存电路、第二锁存电路、第三锁存电路以及第四锁存电路;与感测放大器、第一锁存电路以及第二锁存电路连接的第一布线;与第三锁存电路连接的第二布线;与第四锁存电路连接的第三布线;将第一布线与第三布线可电断开地连接的第一开关晶体管;将第一布线与第二布线可电断开地连接的第二开关晶体管;以及将第二布线与第三布线可电断开地连接的第三开关晶体管。

技术研发人员:藤生政树,志贺仁

受保护的技术使用者:铠侠股份有限公司

技术研发日:

技术公布日:2024/1/15

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1