存储芯片的控制电路、控制方法及相关设备与流程

本说明书涉及芯片,更具体地说,本发明涉及一种存储芯片的控制电路、控制方法及相关设备。

背景技术:

1、想要实现高性能计算不仅需要极大的计算需求,也需要庞大的数据存储及吞吐需求。然而处理器性能与存储器访问带宽和延迟之间的差距越来越大,成为限制计算性能的主要因素之一。这种存储器提供数据的能力与处理器计算能力的不平衡,又被称为“存储墙”。

2、目前,消除“存储墙”主要是通过提高每个存储芯片的数据带宽或者减少存储芯片中存储单元的数据延迟用以提升整个存储器的数据提供能力。通过提高带宽的方法存在着只对连续地址的数据访问有效的缺点。减少数据延迟目前采用的方法是寻找存储器内低延时存储空间或改善芯片的结构,而寻找存储器内低延时存储空间受环境影响较大,且控制复杂;改善芯片结构的方式会增加工艺难度并减少存储容量。

技术实现思路

1、在

技术实现要素:

部分中引入了一系列简化形式的概念,这将在具体实施方式部分中进一步详细说明。本发明的发明内容部分并不意味着要试图限定出所要求保护的技术方案的关键特征和必要技术特征,更不意味着试图确定所要求保护的技术方案的保护范围。

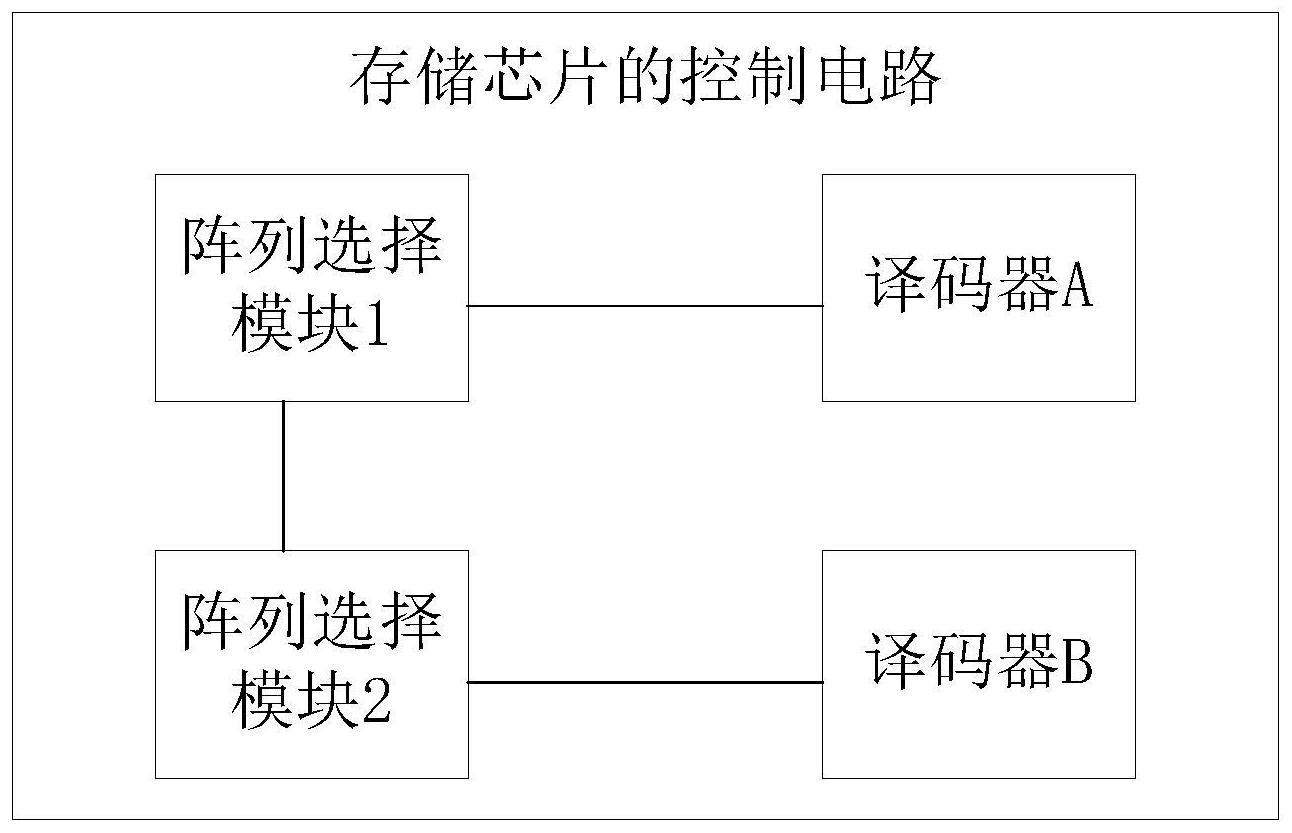

2、为了寻求一种合理的、简单的能够有效消除“存储墙”的途径,第一方面,本发明提出一种存储芯片的控制电路,上述控制电路包括:

3、至少两个阵列选择模块和至少两个译码器;

4、各上述阵列选择模块与自身对应的上述译码器连接,上述阵列选择模块与自身至少一侧相邻的上述阵列选择模块相连;

5、上述阵列选择模块用于根据阵列选择信号和存储方式选择信号生成用于激活译码器的使能信号;

6、上述译码器,用于接收上述使能信号和行地址信号,并受上述使能信号控制对行地址信号进行译码,以确定目标字线。

7、可选的,上述译码器包括:第一译码器,各上述第一译码器共享同一地址信号;

8、上述行地址信号包括行地址第一信号;

9、上述第一译码器用于接收使能信号和行地址第一信号以生成目标字线第一地址,上述目标字线第一地址用于确定上述目标字线。

10、可选的,上述译码器还包括:至少一个字线驱动模块和第二译码器;

11、上述字线驱动模块与自身对应的上述第一译码器相连;上述行地址信号还包括行地址第二信号;

12、上述第二译码器用于根据行地址第二信号生成目标字线第二地址,上述目标字线第二地址用于确定上述目标字线;

13、上述字线驱动模块之间共享上述目标字线第二地址;

14、上述字线驱动模块用于根据上述目标字线第一地址和上述目标字线第二地址确定并激活上述目标字线。

15、可选的,上述存储方式选择信号,包括:指示存储方式为差分存储方式或指示存储方式为普通存储方式,所述差分存储方式用于同时开启多个所述译码器。

16、第二方面,本发明还提出一种存储芯片的控制方法,用于如第一方面上述的任一项的控制电路,包括:

17、采用阵列选择模块根据阵列选择信号和存储方式选择信号生成用于激活译码器的使能信号;

18、译码器接收使能信号和行地址信号,并根据上述使能信号对上述行地址信号进行译码,以确定目标字线。

19、可选的,上述存储方式选择信号包括指示存储方式为差分存储方式的信号;

20、上述方法包括:

21、上述阵列选择模块将上述阵列选择信号发送到其他阵列选择模块,上述阵列选择模块和上述其他阵列选择模块为一组用于差分存储数据的阵列选择模块;

22、各上述译码器接收使能信号和行地址信号以确定目标字线,上述使能信号包括与各上述译码器对应的上述阵列选择模块发送的用于启动上述译码器的信号。

23、可选的,上述方法还包括:

24、将上述行地址信号对应的字线及其相邻的n条字线确定为第二目标字线;

25、激活上述第二目标字线;

26、控制上述第二目标字线连接的存储单元和上述第二目标字线之间的n个第二灵敏放大器阵列以差分存储方式对数据进行处理。

27、第三方面,本发明还提出一种三维芯片,包括:如第一方面上述的任一项的控制电路。

28、第四方面,本发明还提出一种电子设备,包括:如第三方面叙述的三维芯片。

29、第五方面,一种电子系统,包括:存储器、处理器以及存储在上述存储器中并可在上述处理器上运行的计算机程序,上述处理器用于执行存储器中存储的计算机程序时实现如上述的第二方面任一项的存储芯片的控制方法的步骤。

30、综上,本申请实施例提供存储芯片的控制电路包括至少两个阵列选择模块和至少两个译码器,各阵列选择模块与自身对应的译码器连接,阵列选择模块与自身至少一侧相邻的阵列选择模块相连,阵列选择模块根据阵列选择信号和存储方式选择信号生成用于激活译码器的使能信号,译码器接收使能信号和地址信号,并根据使能信号对行地址信号进行译码,以确定目标字线,并激活相应的目标字线,以存储方式选择信号对应的存储方式控制存储芯片存储数据。普通存储方式能够充分利用存储单元提升容量,差分存储方式存储速度较快,通过此控制电路使得存储芯片的存储空间的存储方式可以基于用户需求灵活切换,满足用户对于存储空间和存储速度的需求。

31、本发明的存储器的控制方法,本发明的其它优点、目标和特征将部分通过下面的说明体现,部分还将通过对本发明的研究和实践而为本领域的技术人员所理解。

技术特征:

1.一种存储芯片的控制电路,其特征在于,包括:至少两个阵列选择模块和至少两个译码器;

2.如权利要求1所述的控制电路,其特征在于,所述译码器包括:第一译码器,各所述第一译码器共享同一行地址信号;

3.如权利要求2所述的控制电路,其特征在于,所述译码器还包括:至少一个字线驱动模块和第二译码器;

4.如权利要求1所述的控制电路,其特征在于,所述存储方式选择信号,包括:指示存储方式为差分存储方式或指示存储方式为普通存储方式,所述差分存储方式用于同时开启多个所述译码器。

5.一种存储芯片的控制方法,其特征在于,包括:

6.如权利要求5所述的控制方法,其特征在于,所述存储方式选择信号包括指示存储方式为差分存储方式的信号;

7.如权利要求6所述的方法,其特征在于,还包括:

8.一种三维芯片,其特征在于,包括:如权利要求1至4所述的任一项所述的控制电路。

9.一种电子设备,其特征在于,包括:如权利要求9所述的三维芯片。

10.一种电子系统,包括:存储器、处理器以及存储在所述存储器中并可在所述处理器上运行的计算机程序,其特征在于,所述处理器用于执行存储器中存储的计算机程序时实现如权利要求5至7中任一项所述的存储芯片的控制方法的步骤。

技术总结

本发明公开了一种存储芯片的控制电路、控制方法及其设备。该控制电路包括:至少两个阵列选择模块和至少两个译码器;各上述阵列选择模块与自身对应的上述译码器连接,上述阵列选择模块与自身至少一侧相邻的上述阵列选择模块相连;上述阵列选择模块用于根据阵列选择信号和存储方式选择信号生成用于激活译码器的使能信号;上述译码器,用于接收上述使能信号和行地址信号,并受使能信号控制对行地址信号进行译码,以确定目标字线。普通存储方式能够充分利用存储单元提升容量,差分存储方式存储速度较快,通过此控制电路使得存储芯片的存储空间的存储方式可以基于用户需求灵活切换,满足用户对于存储空间和存储速度的需求。

技术研发人员:拜福君

受保护的技术使用者:西安紫光国芯半导体有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!