存储器布线结构及其布线方法与流程

本申请涉及半导体制造领域,尤其涉及一种可以改善动态耦合的存储器布线结构及其布线方法。

背景技术:

1、随着存储器技术的发展和半导体制造工艺精度的提高,存储器的结构越来越微细化。在这种情况下,存储器内各单元之间的物理距离变窄,两个相邻单元之间的信号耦合(coupling)效应增加,从而产生时序/电压噪声。为减少耦合效应,通常在相邻单元之间增加掩膜层。但是通过增加掩膜层的方式不仅增加了制造成本,还会因为制造时间增加而导致生产效率降低,导致数据错误。存储器的集成度越高,相邻单元之间的影响越大。

2、因此,如何在不增加掩膜层的基础上减少耦合效应,且满足小芯片尺寸和低制造成本,是需要解决的技术问题。

技术实现思路

1、本申请所要解决的技术问题是提供一种存储器布线结构及其布线方法,能够在不增加掩膜层的基础上减少耦合效应,且满足小芯片尺寸和低制造成本。

2、本申请提供了一种存储器布线结构,所述存储器布线结构包括:第一信号线路、第二信号线路以及布线选择器;所述第一信号线路与所述第二信号线路相邻,所述第一信号线路接收第一信号,所述第二信号线路接收第二信号;所述布线选择器响应于使能信号,控制所述第二信号输入所述第一信号线路以对所述第一信号线路进行补偿,并控制所述第一信号输入所述第二信号线路以对所述第二信号线路进行补偿,从而改善所述第一信号线路与所述第二信号线路之间的动态耦合。

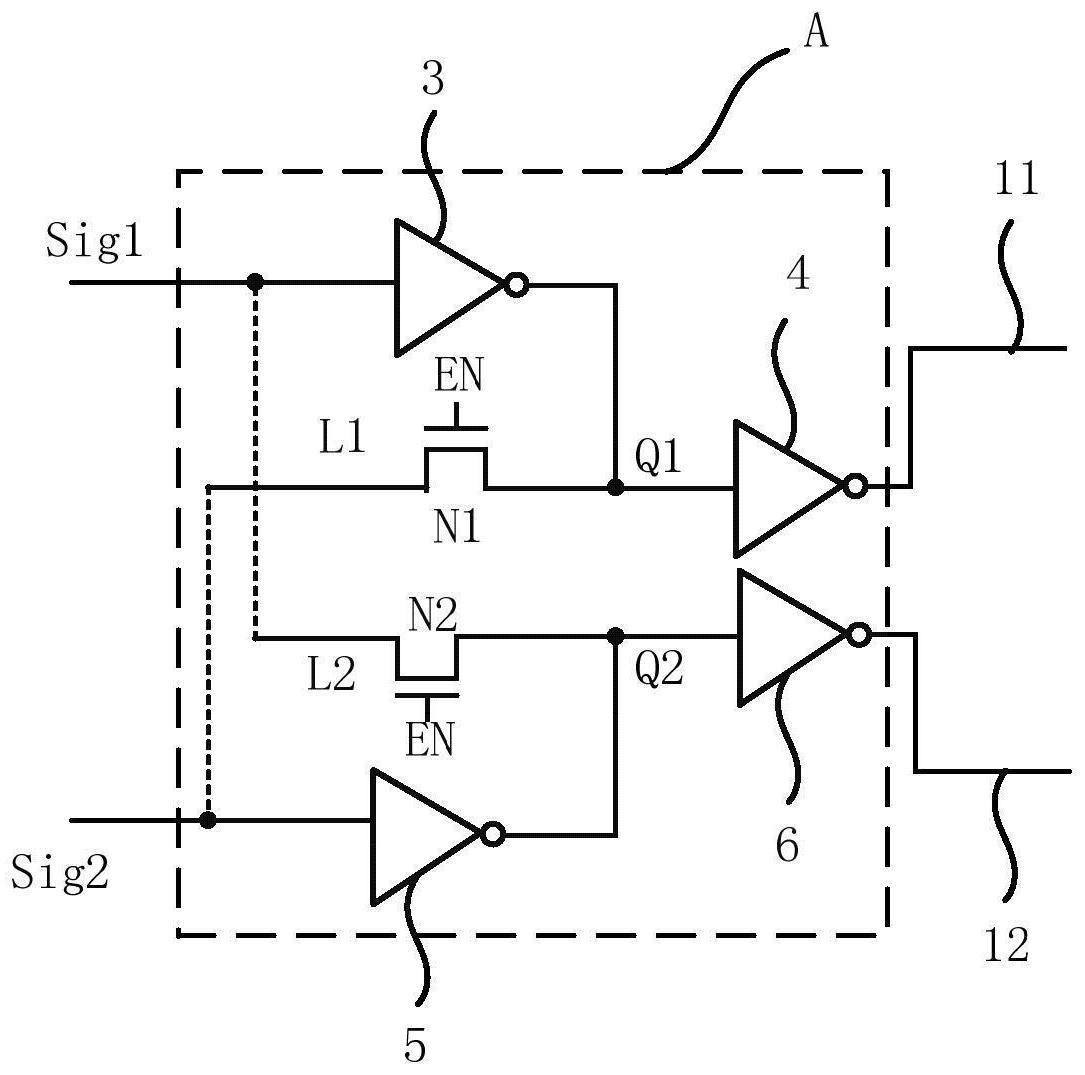

3、在一些实施例中,所述第一信号线路包括第一反相器组、所述第二信号线路包括第二反相器组,所述第一反相器组及第二反相器组均包括串联的两个反相器;所述第一反相器组的输入端接收所述第一信号,所述第二反相器组的输入端接收所述第二信号;所述布线选择器为所述第一信号线路配置的第一补偿线路与为所述第二信号线路配置的第二补偿线路,所述第一补偿线路包括第一晶体管,所述第二补偿线路包括第二晶体管;所述第一晶体管的第一端接收所述第二信号,其第二端连接至所述第一反相器组中两个反相器的连接端,其控制端接收所述使能信号;所述第二晶体管的第一端接收所述第一信号,其第二端连接至所述第二反相器组中两个反相器的连接端,其控制端接收所述使能信号。

4、在一些实施例中,所述结构还包括:耦合噪声传感器,所述耦合噪声传感器用于感测动态耦合影响,以提供所述使能信号。

5、在一些实施例中,所述耦合噪声传感器包括:与所述第一信号线路的结构相同的主控干扰线路以及与所述主控干扰线路具有信号耦合效应的被控受干扰线路;其中,于所述主控干扰线路中输入一检测信号,当感测到所述被控受干扰线路受到主控干扰线路的干扰时,通过所述被控受干扰线路输出所述使能信号。

6、在一些实施例中,所述被控受干扰线路包括:连接至所述被控受干扰线路输入节点的第三反向器组以及复位开关;当所述被控受干扰线路受到主控干扰线路的干扰时,所述第三反向器组输出所述使能信号;所述复位开关用于响应于复位信号对所述被控受干扰线路进行复位,以用于为下一次输出所述使能信号做准备。

7、为了解决上述问题,本申请还提供了一种存储器布线方法,所述存储器布线方法包括:通过第一信号线路接收第一信号,通过第二信号线路接收第二信号,其中,所述第一信号线路与所述第二信号线路相邻;以及响应于使能信号,通过布线选择器控制所述第二信号输入所述第一信号线路以对所述第一信号线路进行补偿,并控制所述第一信号输入所述第二信号线路以对所述第二信号线路进行补偿,从而改善所述第一信号线路与所述第二信号线路之间的动态耦合。

8、在一些实施例中,所述布线选择器包括为所述第一信号线路配置的第一补偿线路与为所述第二信号线路配置的第二补偿线路;所述的响应于使能信号,通过布线选择器控制所述第二信号输入所述第一信号线路以对所述第一信号线路进行补偿,并控制所述第一信号输入所述第二信号线路以对所述第二信号线路进行补偿的步骤进一步包括:响应于所述使能信号,所述第一补偿线路接收所述第二信号以对所述第一信号线路进行补偿;以及响应于所述使能信号,所述第二补偿线路接收所述第一信号以对所述第一信号线路进行补偿。

9、在一些实施例中,所述存储器布线方法还包括:通过耦合噪声传感器感测动态耦合影响,以提供所述使能信号。

10、在一些实施例中,所述的通过耦合噪声传感器感知动态耦合影响,以提供所述使能信号的步骤进一步包括:配置与所述第一信号线路的结构相同的主控干扰线路;配置与所述主控干扰线路具有信号耦合效应的被控受干扰线路;于所述主控干扰线路中输入一检测信号,当感测到所述被控受干扰线路受到主控干扰线路的干扰时,通过所述被控受干扰线路输出所述使能信号。

11、在一些实施例中,所述方法还包括:响应于复位信号对所述被控受干扰线路进行复位,以用于为下一次输出所述使能信号做准备。

12、上述技术方案,避免相邻的信号线路之间由于信号耦合造成输出的信号失真,从而避免了存储器在存储或读取时的数据错误,在不增加掩膜层的基础上减少耦合效应,且满足小芯片尺寸和低制造成本。

13、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本申请。对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为授权说明书的一部分。

技术特征:

1.一种存储器布线结构,其特征在于,包括:第一信号线路、第二信号线路以及布线选择器;

2.根据权利要求1所述的存储器布线结构,其特征在于,所述布线选择器包括布置在所述第一信号线路上的第一反相器组、布置在所述第二信号线路上的第二反相器组,所述第一反相器组及第二反相器组均包括串联的两个反相器,所述第一反相器组的输入端接收所述第一信号,所述第二反相器组的输入端接收所述第二信号;

3.根据权利要求1所述的存储器布线结构,其特征在于,所述结构还包括:

4.根据权利要求1所述的存储器布线结构,其特征在于,所述耦合噪声传感器包括:

5.根据权利要求4所述的存储器布线结构,其特征在于,所述被控受干扰线路包括:连接至所述被控受干扰线路输入节点的第三反向器组以及复位开关;

6.一种存储器布线方法,其特征在于,包括:

7.根据权利要求6所述的存储器布线方法,其特征在于,所述布线选择器包括为所述第一信号线路配置的第一补偿线路与为所述第二信号线路配置的第二补偿线路;所述的响应于使能信号,通过布线选择器控制所述第二信号输入所述第一信号线路以对所述第一信号线路进行补偿,并控制所述第一信号输入所述第二信号线路以对所述第二信号线路进行补偿的步骤进一步包括:

8.根据权利要求6所述的存储器布线方法,其特征在于,所述方法还包括:

9.根据权利要求8所述的存储器布线方法,其特征在于,所述的通过耦合噪声传感器感知动态耦合影响,以提供所述使能信号的步骤进一步包括:

10.根据权利要求9所述的存储器布线方法,其特征在于,所述方法还包括:

技术总结

本申请提供了一种存储器布线结构及其布线方法。所述存储器布线结构包括:相邻的第一信号线路与第二信号线路,所述第一信号线路接收第一信号,所述第二信号线路接收第二信号;布线选择器,响应于使能信号,控制所述第二信号输入所述第一信号线路以对所述第一信号线路进行补偿,并控制所述第一信号输入所述第二信号线路以对所述第二信号线路进行补偿,从而改善所述第一信号线路与所述第二信号线路之间的动态耦合。本申请避免了相邻的信号线路之间由于信号耦合造成的输出信号失真,避免了存储器在存储或读取时的数据错误,在不增加掩膜层的基础上减少耦合效应,且满足小芯片尺寸和低制造成本。

技术研发人员:请求不公布姓名

受保护的技术使用者:提米芯创(上海)科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!