本公开涉及半导体测试领域,特别涉及一种测试方法、测试结构及存储器。

背景技术:

1、动态随机存取存储器(dynamic random access memory,dram)是一种广泛应用于计算机系统的半导体存储器。

2、为了保证提供给客户的产品满足客户要求或满足jedec规格,产品在出货前需要经过一系列的测试以保证出货品质和信赖性要求。

3、对于存储器的测试而言,测试的有效性、测试时间及测试机台成本是需要考虑的三个重要因素,对于存储器的老化测试而言,老化测试时间长且测试机台昂贵,导致老化测试成本高。

技术实现思路

1、本公开实施例提供一种测试方法、测试结构及存储器,通过在存储器中设置相关电路和接口,降低测试机台成本,且测试基于存储器内建自测试(buildinselftest,bist)的方式进行,以提高测试效率,从而降低整个老化测试的测试成本。

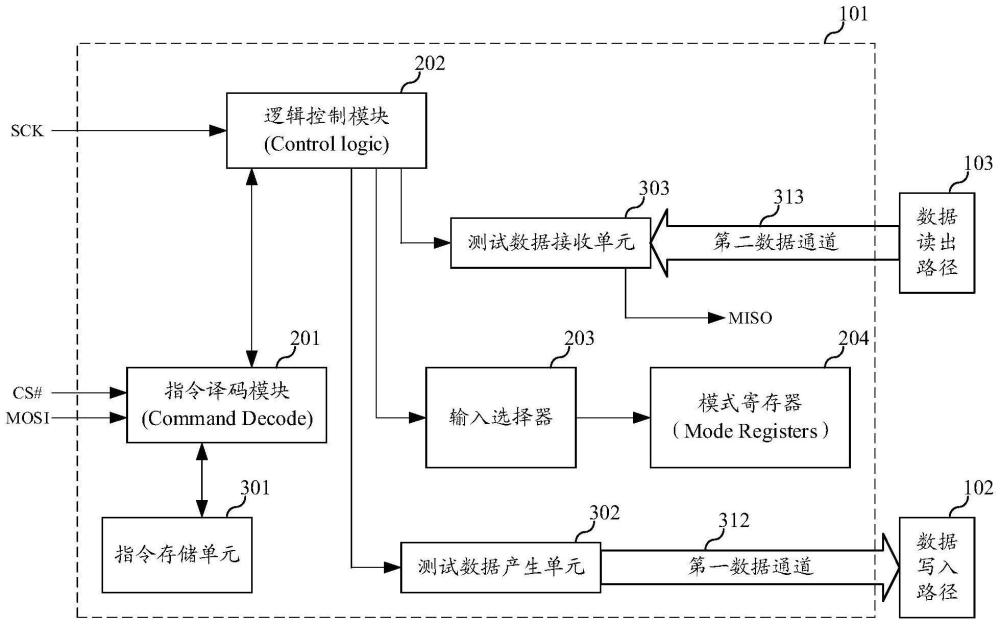

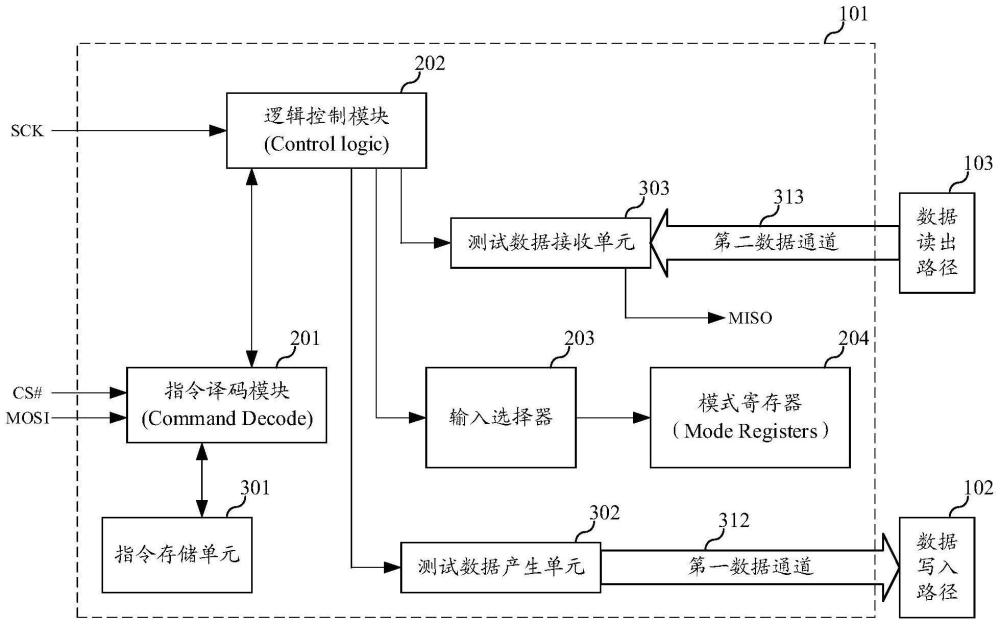

2、本公开一实施例提供了一种测试结构,设置于存储器外围控制电路,外围控制电路包括:指令译码模块、逻辑控制模块、输入选择器和模式寄存器,包括:指令存储单元,连接指令译码模块,被配置为,存储对存储器进行老化测试的测试命令;测试数据产生单元,输入端连接逻辑控制模块,输出端通过第一数据通道连接存储器的数据写入路径,用于向存储单元中写入测试数据;测试数据接收单元,一输入端连接逻辑控制模块,另一输入端通过第二数据通道连接存储器的数据读出路径,用于读出存储单元中的测试数据;测试数据接收单元还被配置为,基于向存储单元中写入的测试数据与从存储单元中读出的测试数据的差异,获取并输出存储器的老化程度的测试结果。

3、指令存储单元用于存储存储器进行老化测试所需的测试指令,存储器的指令译码模块和逻辑控制模块识别测试指令,并根据测试指令控制存储器进行相应测试;且测试数据产生单元通过第一数据通道连接存储器的数据写入路径,测试数据接收单元通过第二数据通道连接存储器的数据读出路径,从而实现测试结构与存储单元进行测试数据的传输,即通过在存储器中设置测试结构,存储器可以基于内部结构完成测试,降低了测试机台成本,且测试基于bist的方式进行,提高了测试效率,从而降低整个老化测试的测试成本。

4、另外,指令存储单元还用于获取数据保持时间;存储器被配置为,存储单元在存储测试数据且保持数据保持时间后读出测试数据。指令存储单元通过获取不同的数据保持时间,以获取写入和读出的测试数据一致时,存储器的数据存储时间,从而实现对存储器在不同数据存储时间下的老化测试,提高测试的准确性。

5、另外,数据接收单元还被配置为,基于向存储单元中写入的测试数据与从存储单元中读出的测试数据的差异,输出存在差异的存储单元的地址信号。通过数据接收单元输出存在差异的存储单元的地址信号,实现对存储器进行老化测试的过程中,输出共走状态异常的存储单元对应的地址西信号,以便于工程师后续对存储器异常状态的存储单元的读写方式进行改进。

6、另外,测试数据产生单元,包括:地址获取子单元,被配置为,获取待测存储单元的地址信号;测试数据生成子单元,连接地址获取子单元,被配置为,基于地址信号和测试数据,生成测试图形;发送子单元,连接测试数据生成子单元和第一数据通道,被配置为,输出测试图形。基于测试图形单次进行大批量数据测试,保证老化测试结果的准确性,且优化老化测试的测试时间。

7、另外,第一数据通道和第二数据通道基于测试信号开启,测试信号表征存储器执行老化测试。通过测试信号导通第一数据通道和第二数据通道,节省存储器的功耗,且避免新增的数据传输路径干扰存储器在正常工作模式下的数据传输。

8、另外,测试结构基于spi串行外围接口协议接收或发送数据。

9、另外,串行外围接口,包括:测试输入引脚,耦接指令译码模块,被配置为,输入存储器进行老化测试所需的测试命令和测试数据;测试输出引脚,耦接测试数据接收单元,被配置为,输出测试结果;时钟引脚,耦接逻辑控制模块,被配置为,接收时钟信号;选择引脚,耦接指令译码模块,被配置为,接收片选信号。通过设置在存储器内的测试结构进行老化测试,通过4接口连接测试机台即可完成老化测试,极大地降低了测试机台成本,从而降低整个老化测试的测试成本。

10、本公开另一实施例提供一种测试方法,应用于上述实施例提供的测试结构,包括:调用并识别指令存储单元中存储的测试命令;获取测试数据、片选信号和时钟信号,并基于识别的测试命令、片选信号和时钟信号,基于第一数据通道向待测存储单元中写入测试数据;基于第二数据通道读出待测存储单元中的测试数据,并基于向存储单元中写入的测试数据与从存储单元中读出的测试数据的差异,获取并输出存储器老化测试的测试结果。

11、通过第一数据通道向待测存储单元中写入测试数据,通过第二数据通道读出待测存储单元中存储的测试数据,从而实现测试结构与存储单元进行测试数据的传输,即通过在存储器中设置测试结构,存储器可以基于内部结构完成测试,降低了测试机台成本,且测试基于bist的方式进行,提高了测试效率,从而降低整个老化测试的测试成本。

12、另外,测试结果包括:存储器的老化程度,以及写入和读出测试数据存在差异的存储单元的地址信号。

13、另外,输出存储器老化测试的测试结果,包括:基于测试输出引脚向测试机台输出测试结果。

14、另外,获取测试数据、片选信号和时钟信号,包括:基于测试输入引脚获取测试机台发送的测试数据、片选信号和时钟信号。

15、另外,调用并识别指令存储单元中存储的测试命令之后,且获取测试数据、片选信号和时钟信号之前,还包括:获取测试信号,输入选择器基于测试信号配置模式寄存器于测试模式。

16、另外,向待测存储单元中写入测试数据,包括:获取待测存储单元的地址信号;基于地址信号和测试数据,生成测试图形;向待测存储单元中写入测试图形。

17、另外,向待测存储单元中写入测试数据之后,且读出待测存储单元中的测试数据之前,还包括:待测存储单元存储数据保持时间的测试数据。

18、本公开又一实施例还提供了一种存储器,设置有上述实施例提供的测试结构,或者还可以基于上述实施例提供的测试放大进行测试。通过在存储器中设置相关电路和接口,降低测试机台成本,且测试基于bist的方式进行,以提高测试效率,从而降低存储器老化测试的测试成本。

技术特征:1.一种测试结构,设置于存储器外围控制电路,所述外围控制电路包括:指令译码模块、逻辑控制模块、输入选择器和模式寄存器,其特征在于,包括:

2.根据权利要求1所述的测试结构,其特征在于,包括:

3.根据权利要求1所述的测试结构,其特征在于,所述数据接收单元还被配置为,基于向存储单元中写入的所述测试数据与从存储单元中读出的所述测试数据的差异,输出存在差异的所述存储单元的地址信号。

4.根据权利要求1所述的测试结构,其特征在于,所述测试数据产生单元,包括:

5.根据权利要求1所述的测试结构,其特征在于,所述第一数据通道和所述第二数据通道基于测试信号开启,所述测试信号表征所述存储器执行老化测试。

6.根据权利要求1-5任一项所述的测试结构,其特征在于,包括:所述测试结构基于spi串行外围接口协议接收或发送数据。

7.根据权利要求6所述的测试结构,其特征在于,串行外围接口,包括:

8.一种测试方法,应用于权利要求1~7任一项所述的测试结构,其特征在于,包括:

9.根据权利要求8所述的测试方法,其特征在于,所述测试结果包括:所述存储器的老化程度,以及写入和读出所述测试数据存在差异的所述存储单元的地址信号。

10.根据权利要求8或9所述的测试方法,其特征在于,所述输出存储器老化测试的测试结果,包括:基于测试输出引脚向测试机台输出所述测试结果。

11.根据权利要求8所述的测试方法,其特征在于,所述获取测试数据、片选信号和时钟信号,包括:基于测试输入引脚获取测试机台发送的所述测试数据、所述片选信号和所述时钟信号。

12.根据权利要求8所述的测试方法,其特征在于,所述调用并识别指令存储单元中存储的测试命令之后,且所述获取测试数据、片选信号和时钟信号之前,还包括:获取测试信号,输入选择器基于所述测试信号配置所述模式寄存器于测试模式。

13.根据权利要求8所述的测试方法,其特征在于,所述向待测存储单元中写入所述测试数据,包括:

14.根据权利要求8所述的测试方法,其特征在于,所述向待测存储单元中写入所述测试数据之后,且所述读出所述待测存储单元中的所述测试数据之前,还包括:所述待测存储单元存储数据保持时间的所述测试数据。

15.一种存储器,其特征在于,设置有权利要求1~7任一项所述的测试结构。

技术总结本公开实施例涉及半导体测试领域,特别涉及一种测试方法、测试结构及存储器,测试方法包括:指令存储单元,用于存储对存储器进行老化测试的测试命令;测试数据产生单元,输入端连接逻辑控制模块,输出端通过第一数据通道连接存储器的数据写入路径,用于向存储单元中写入测试数据;测试数据接收单元,一输入端连接逻辑控制模块,另一输入端通过第二数据通道连接存储器的数据读出路径,用于读出存储单元中的测试数据;测试数据接收单元用于获取并输出存储器的老化程度的测试结果。本公开实施例通过在存储器中设置相关电路和接口,降低测试机台成本,且测试基于存储器内建自测试的方式进行,以提高测试效率,从而降低整个老化测试的测试成本。

技术研发人员:侯永康,陈春晖,宋标

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:技术公布日:2024/1/5