非易失性存储器件的制作方法

本发明构思涉及存储器件,更具体地,涉及具有与垂直沟道结构相对应的单元串的非易失性存储器件。

背景技术:

1、存储器件用于存储数据,并且分为易失性存储器件和非易失性存储器件。为了响应对非易失性存储器件的增大容量和小型化的需求,开发了一种包括在衬底上沿垂直方向延伸的多个垂直沟道结构的3d存储器件。为了进一步提高3d存储器件的集成度,随着垂直堆叠在衬底上的多条字线的数量增加,每个垂直沟道结构的长度会增加。随着垂直沟道结构的长度增加,可能发生位线电压未在整个沟道区域正确传输的沟道恢复劣化现象。

技术实现思路

1、本发明构思提供了一种非易失性存储器件,尽管该非易失性存储器件的沟道区域的长度或电阻增加了,仍然能够通过在整个沟道区域中顺利地执行沟道恢复来改善性能。

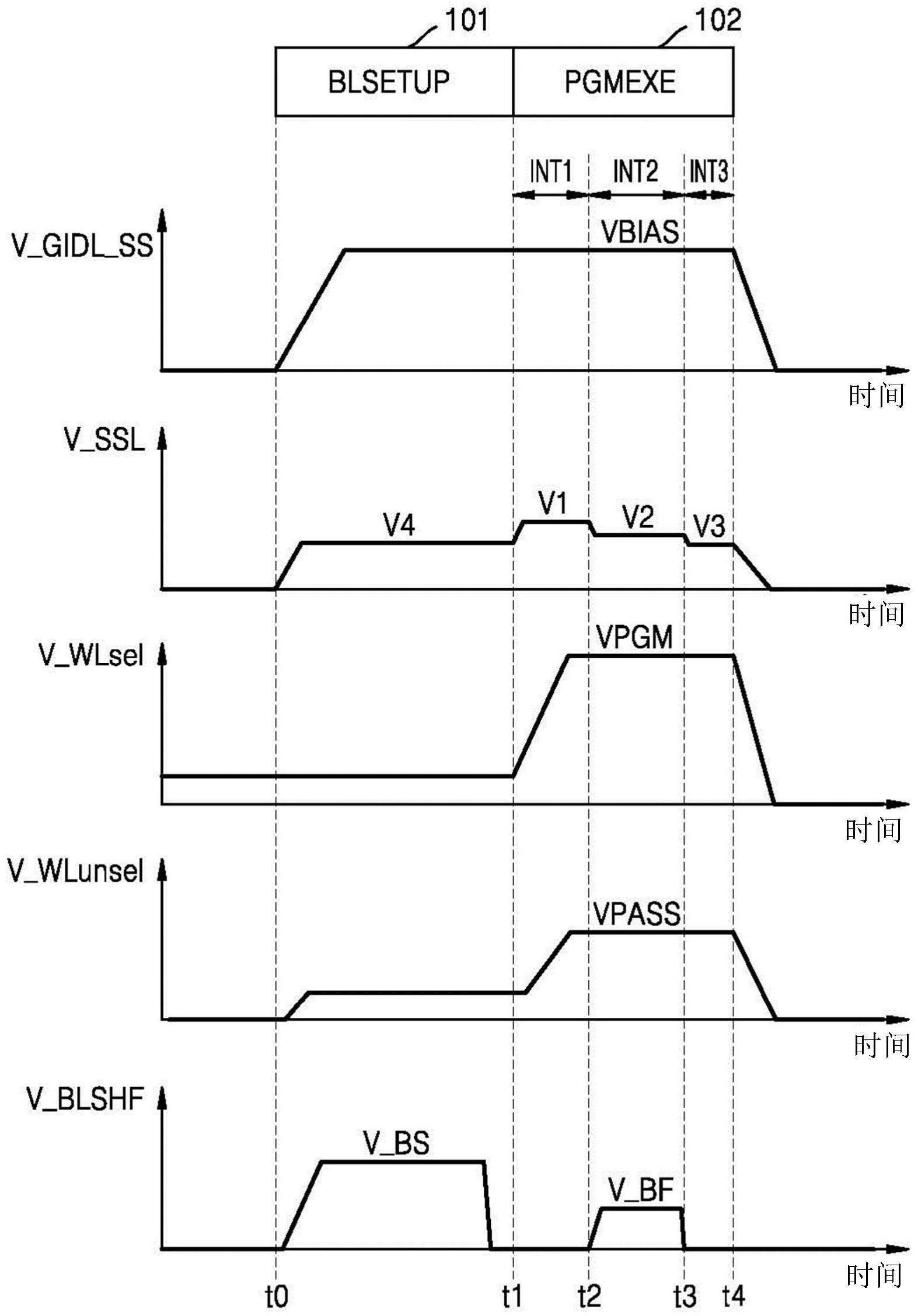

2、根据本发明构思的一个方面,提供了一种非易失性存储器件,所述非易失性存储器件包括:存储单元阵列,所述存储单元阵列包括多个单元串,每个单元串在衬底上方沿垂直方向延伸,并且每个单元串包括分别连接到多条字线的多个存储单元和连接到串选择线的串选择晶体管;页缓冲电路,所述页缓冲电路包括连接到所述存储单元阵列的多个页缓冲器,每个页缓冲器包括被配置为存储强制信息的强制锁存器,并且每个页缓冲器通过位线连接到选定单元串;以及控制逻辑电路,所述控制逻辑电路被配置为在对选定字线进行编程操作期间,将以下电压中的至少两个电压控制为彼此不同:在位线强制操作之前的第一间隔内施加到所述串选择线的第一电压、在执行所述位线强制操作的第二间隔内施加到所述串选择线的第二电压、以及在执行所述位线强制操作之后的第三间隔内施加到所述串选择线的第三电压,所述位线强制操作用于通过所述位线向所述选定单元串传送所述强制信息。

3、根据本发明构思的另一方面,提供了一种非易失性存储器件,包括:多条字线,所述多条字线包括相对靠近衬底的第一字线和相对远离所述衬底的第二字线;存储单元阵列,所述存储单元阵列包括多个单元串,每个单元串在所述衬底上方沿垂直方向延伸并且每个单元串包括分别连接到所述多条字线的多个存储单元;页缓冲电路,所述页缓冲电路包括连接到所述存储单元阵列的多个页缓冲器,所述多个页缓冲器中的每个页缓冲器通过位线连接到选定单元串,并且包括位线切断晶体管和强制锁存器,所述位线切断晶体管被配置为响应于位线切断信号被驱动,所述强制锁存器被配置为存储强制信息;以及控制逻辑电路,所述控制逻辑电路被配置为在对选定字线进行编程操作期间,控制在位线强制操作被执行之前的延迟间隔,在所述延迟间隔中与所述位线切断信号相对应的位线切断电压维持在与接地电压相对应的电压电平,所述位线强制操作通过所述位线向所述选定单元串传送所述强制信息,基于所述选定字线对应于所述第一字线的所述延迟间隔的长度大于基于所述选定字线对应于所述第二字线的所述延迟间隔的长度。

4、根据本发明构思的另一方面,提供了一种非易失性存储器件,包括:多条字线,所述多条字线包括第一组和第二组,所述第一组包括相对靠近衬底的字线,所述第二组包括相对远离所述衬底的字线;串选择线,所述串选择线在所述多条字线上方;存储单元阵列,所述存储单元阵列包括多个单元串,每个单元串在所述衬底上方沿垂直方向延伸,每个单元串连接到所述多条字线和所述串选择线;页缓冲电路,所述页缓冲电路包括连接到所述存储单元阵列的多个页缓冲器,所述多个页缓冲器中的每个页缓冲器通过位线连接到选定单元串且包括位线切断晶体管和强制锁存器,所述位线切断晶体管被配置为响应于位线切断信号被驱动,所述强制锁存器被配置为存储强制信息;以及控制逻辑电路,所述控制逻辑电路被配置为在对选定字线的编程操作中控制施加到所述串选择线以执行位线强制操作的电压和与所述位线切断信号相对应的位线切断电压,所述位线强制操作通过所述位线向所述选定单元串传送所述强制信息,所述控制逻辑电路还被配置为:针对所述第一组和所述第二组不同地控制在执行所述位线强制操作之前的第一间隔内施加到所述串选择线的第一电压,以及针对所述第一组和所述第二组不同地控制在执行所述位线强制操作之前的延迟间隔,在所述延迟间隔中所述位线切断电压维持在与所述接地电压相对应的电压电平。

技术特征:

1.一种非易失性存储器件,所述非易失性存储器件包括:

2.根据权利要求1所述的非易失性存储器件,其中,

3.根据权利要求1所述的非易失性存储器件,其中,

4.根据权利要求1所述的非易失性存储器件,其中,

5.根据权利要求1所述的非易失性存储器件,其中,

6.根据权利要求5所述的非易失性存储器件,其中,

7.根据权利要求5所述的非易失性存储器件,其中,

8.根据权利要求7所述的非易失性存储器件,其中,

9.根据权利要求7所述的非易失性存储器件,其中,

10.根据权利要求9所述的非易失性存储器件,其中,

11.根据权利要求1所述的非易失性存储器件,其中,

12.一种非易失性存储器件,所述非易失性存储器件包括:

13.根据权利要求12所述的非易失性存储器件,其中,

14.根据权利要求13所述的非易失性存储器件,其中,

15.根据权利要求14所述的非易失性存储器件,其中,

16.根据权利要求14所述的非易失性存储器件,其中,

17.根据权利要求13所述的非易失性存储器件,其中,

18.一种非易失性存储器件,所述非易失性存储器件包括:

19.根据权利要求18所述的非易失性存储器件,其中,所述控制逻辑电路还被配置为:

20.根据权利要求18所述的非易失性存储器件,其中,

技术总结

本发明提供了一种非易失性存储器件,该非易失性存储器件包括:存储单元阵列,所述存储单元阵列包括均包括存储单元和连接到串选择线的串选择晶体管的单元串;页缓冲电路,页缓冲电路包括均包括被配置为存储强制信息的强制锁存器的页缓冲器;以及控制逻辑电路,被配置为在对选定字线进行编程操作期间,将以下电压中的至少两个电压控制为彼此不同:在位线强制操作之前的第一间隔内施加到所述串选择线的第一电压、在执行所述位线强制操作的第二间隔内施加到所述串选择线的第二电压、以及在执行所述位线强制操作之后的第三间隔内施加到所述串选择线的第三电压,所述位线强制操作用于向所述选定单元串传送所述强制信息。

技术研发人员:崔容赫,李耀翰,朴相元,柳载悳

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!