半导体存储装置的制作方法

本发明涉及一种使或非(not or,nor)型快闪存储器与电阻变化型存储器集成的半导体存储装置。

背景技术:

1、或非型快闪存储器是在位线与源极线之间配置一个存储单元(memory cell),能够进行对存储单元的随机存取(random access)的非易失性存储器。另外,为了实现其集成度的提高,采用了虚拟接地方式或多值方式(例如日本专利特开2011-192346号公报)。

2、另一方面,作为取代或非型快闪存储器的非易失性存储器,有利用可变电阻元件的电阻变化型存储器。电阻变化型存储器是通过对可变电阻元件施加脉冲电压,使可变电阻元件可逆且非易失地变为高电阻状态或低电阻状态来存储数据(例如日本专利6810725号公报)。

技术实现思路

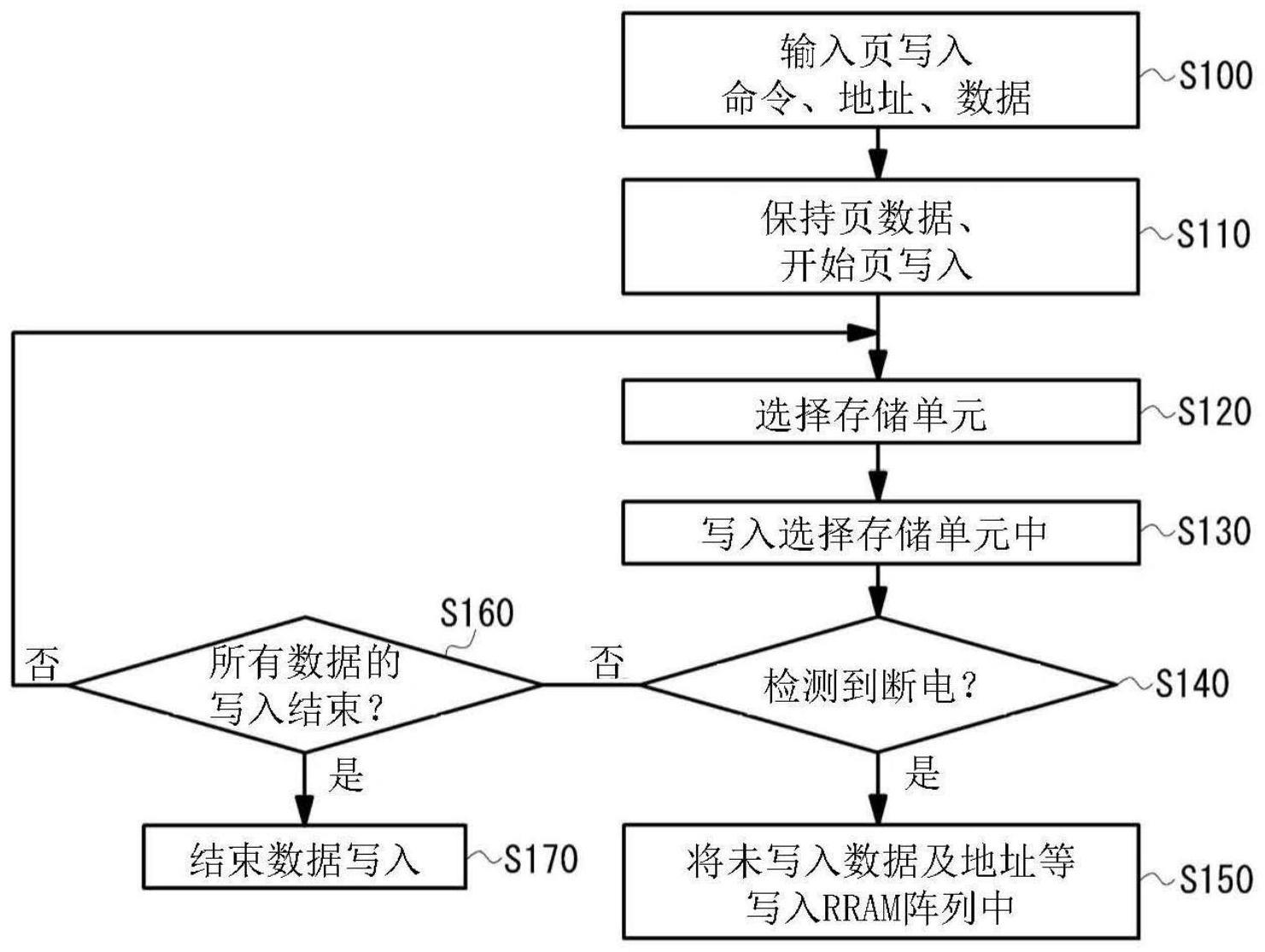

1、或非(not or,nor)型快闪存储器能够随机存取存储单元,但为了实现与与非(notand,nand)型快闪存储器等的兼容性,能够进行以页为单位的写入(编程)。nor型快闪存储器例如根据从主计算机输出的数据输入命令接收页数据或地址,接着根据页写入命令向选择页写入页数据。nor型快闪存储器将接收到的页数据保持于数据寄存器中,并将从数据寄存器中选择的数据写入选择页中。然后,主计算机为了检查页写入正常完成而读取状态信息。

2、然而,在正进行页写入的过程中,若向nor型快闪存储器的电源电压被切断,或者电源电压相较于保证运行的最低电压而言降低,则写入会中断。由于保持页数据的数据寄存器为易失性,因此若电源电压相较于运行保证电压而言下降,则保持于数据寄存器中的页数据会消失,即使电源电压复位,nor型快闪存储器也无法重新开始页写入。另外,可知,主计算机在电源电压复位后,无法从状态信息中正常完成写入,但由于无法获知正确写入了多少数据,因此最终必须从一开始就重新进行页写入。

3、本发明解决此种以往的课题,其目的在于提供一种可使因电源电压的瞬停或变动等而中断的写入复位的半导体存储装置。

4、本发明的半导体存储装置包括:存储单元阵列,包括具有或非(nor)型或与或(nand)型快闪存储器结构的第一存储单元阵列,及具有电阻变化型存储器结构的第二存储单元阵列;控制部件,控制第一存储单元阵列或第二存储单元阵列中被选择的存储单元的读写;以及第一检测部件,检测电源电压已下降至断电电平,当在向第一存储单元阵列的写入动作过程中由所述第一检测部件检测到断电电平时,所述控制部件将至少未完成向第一存储单元阵列的写入的未写入数据写入第二存储单元阵列中。

5、根据本发明,在检测到电源电压的断电电平时,将未完成向第一存储单元阵列的写入的未写入数据写入第二存储单元阵列中,因此可避免未写入数据的消失,在电源电压复原时,可将未写入数据写入第一存储单元阵列中,从而使中断的写入复位。

技术特征:

1.一种半导体存储装置,包括:

2.根据权利要求1所述的半导体存储装置,还包括第二检测部件,所述第二检测部件检测电源电压已达到通电电平,

3.根据权利要求1或2所述的半导体存储装置,其中,所述控制部件进而将用于进行向所述第一存储单元阵列的写入的地址与未写入数据一起写入所述第二存储单元阵列中,

4.根据权利要求1或2所述的半导体存储装置,其中,所述控制部件进而将用于进行向所述第一存储单元阵列的写入的命令与未写入数据一起写入所述第二存储单元阵列中,

5.根据权利要求1或2所述的半导体存储装置,还包括数据保持部件,所述数据保持部件保持从外部输入的数据,

6.根据权利要求5所述的半导体存储装置,其中,所述数据保持部件保持从外部输入的页数据,所述控制部件基于从外部输入的页写入命令,向所述第一存储单元阵列中被选择的行写入所述数据保持部件所保持的页数据,进而,所述控制部件将从所述第二存储单元阵列读取的未写入数据写入所述被选择的行中。

7.根据权利要求5所述的半导体存储装置,其中,所述数据保持部件保持从外部输入的字节数据,所述控制部件基于从外部输入的字节写入命令,向所述第一存储单元阵列中被选择的行写入所述数据保持部件所保持的字节数据,进而,所述控制部件将从所述第二存储单元阵列读取的未写入数据写入所述被选择的行中。

8.根据权利要求5所述的半导体存储装置,还包括数据选择部件,所述数据选择部件选择所述数据保持部件所保持的数据,

9.根据权利要求1所述的半导体存储装置,其中,所述控制部件使用断电电平与成为所述第二存储单元阵列的写入极限的最小电压之间的电压,向所述第二存储单元阵列写入未写入数据。

10.根据权利要求1所述的半导体存储装置,其中,所述存储单元阵列包括所述第一存储单元阵列与所述第二存储单元阵列所共用的位线、及连接于所述第一存储单元阵列与所述第二存储单元阵列之间,且将所述位线选择性地连接或非连接于所述第二存储单元阵列的进入栅。

11.根据权利要求10所述的半导体存储装置,其中,所述第二存储单元阵列包含一页,所述第二存储单元阵列配置于用于选择所述位线的位线选择电路的下方。

技术总结

本发明提供一种可使因电源电压的瞬停或变动等而中断的写入自动复位的半导体存储装置。本发明的非易失性存储器包括形成有或非型阵列及电阻变化型阵列的存储单元阵列。在向或非型阵列的写入过程中电源电压下降到断电电平的情况下,读写控制部将未写入数据写入电阻变化型阵列中。之后,在检测到电源电压的通电时,读写控制部从电阻变化型阵列读取未写入数据,并将未写入数据写入或非型阵列中,由此使中断的写入复位。

技术研发人员:矢野胜

受保护的技术使用者:华邦电子股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!