一种eFlash电路和模拟电路共用测试PAD的电路结构的制作方法

一种eflash电路和模拟电路共用测试pad的电路结构

(一)技术领域:

1.本发明属于集成电路芯片的测试电路设计领域,具体涉及eflash测试电路设计与模拟测试电路共用测试pad的实现。

(二)

背景技术:

2.eflash具有掉电数据保持的非挥发特性,是mcu中必不可少的组成部分,用来存储代码和使用过程中产生的数据。不同于一般模拟电路,eflash中包含多种电压,尤其是写入和消除动作需要高压/低压,考虑到eflash中高低压,以及其他一些特性,测试时eflash相关功能、性能通常是单独测试的,相关测试pad一般也不与外围其他模拟电路共用。主要是考虑到eflash测试电路与模拟测试电路的不同电压域之间互联,容易产生意料之外的漏电通路以及耐压等问题。

3.本发明所涉及的电路中,eflash测试电路采用pmos开关管控制传送4v电位到测试pad,模拟测试电路采用nmos开关管控制传送0.5~2.75v电位到测试pad上,因两者在上述电源和控制方式上的差异,通常由各自pad承担测试任务。然而,这样虽然避免了一些不必要的麻烦,却是浪费了测试pad数量和牺牲了版图面积。因此,本发明在充分考虑上述不同电压域之间互联所存在的风险之上,设计此电路结构,从而在避免漏电通路产生的同时实现了eflash电路和模拟电路共用测试pad,减少了pad数量,节省版图面积。

(三)

技术实现要素:

4.本文提出了一种eflash电路和模拟电路共用测试pad的实现方法。

5.本电路结构通过改进电平位移电路电路和pmos传输电路的方式,实现了在测试模拟电路电位时,eflash的测试通路处于完全关闭状态。

6.本发明主要包括eflash pmos传输电路、模拟电路nmos传输电路和控制电路几个电路功能模块组成,其中:

7.eflash pmos传输电路:包括pmos开关管pm0,pm1,pm2;

8.模拟电路nmos传输电路:包括nmos开关管nm0;

9.控制电路c2:改进型电平位移器。

10.nmos开关管nm0:nmos开关管nm0的源极接芯片测试pad tm,nmos开关管nm0的漏极接模拟电路待测电平tm_ana,nmos开关管nm0的栅极接控制信号ctrl1,nmos开关管nm0的衬底接地;

11.pmos开关管pm0:pmos开关管pm0的源极和衬底接芯片测试pad tm,pmos开关管pm0的漏极接pmos开关管pm1的源极,pmos开关管pm0的栅极接控制电路c2的输出g2;

12.pmos开关管pm1:pmos开关管pm1的源极接pmos开关管pm0的漏极,pmos开关管pm1的漏极接pmos开关管pm2的源极,pmos开关管pm1的栅极接vd15电平,pmos开关管pm1的衬底接eflash电路待测电平tm_ef;

13.pmos开关管pm2:pmos开关管pm2的源极接pmos开关管pm1的漏极,pmos开关管pm2

的漏极和衬底接eflash电路待测电平tm_ef,pmos开关管pm2的栅极接控制信号ctrl2。

14.控制电路c2:输入端口接控制信号ctrl2,输出端口g2与pmos开关管pm0的栅极连接,电源端接芯片测试pad tm。

15.控制电路c2(改进型电平位移器)由晶体管nm1、晶体管nm2、晶体管pm3、晶体管pm4、晶体管pm5和反相器inv1构成,其输入控制信号为ctrl2,输出信号为g2,电源为vdd;具体连接关系为:晶体管nm1的源极和衬底接地,晶体管nm1的栅极接反相器inv1的输出,晶体管nm1的漏极接晶体管pm4的漏极和晶体管pm5的栅极;晶体管pm4的漏极接晶体管nm1的漏极和晶体管pm5的栅极,晶体管pm4的源极接晶体管pm3的漏极和晶体管pm5的源极,晶体管pm4的衬底接电源vdd,晶体管pm4的栅极接晶体管pm5的漏极;晶体管nm2的源极和衬底接地,晶体管nm2的栅极接输入控制信号ctrl1,晶体管nm2的漏极接晶体管pm5的漏极、晶体管pm4的栅极;晶体管pm5的漏极接晶体管nm2的漏极、晶体管pm4的栅极,晶体管pm5的栅极接晶体管nm1的漏极和晶体管pm4的漏极和输出信号g1,晶体管pm5的源极接晶体管pm3的晶体管的漏极和晶体管pm4的源极,pm5的衬底接电源vdd;晶体管pm3的源极和衬底接电源vdd,晶体管pm3的漏极接晶体管pm4的源极和晶体管pm5的源极,晶体管pm3的栅极接固定电位vd25。

(四)附图说明:

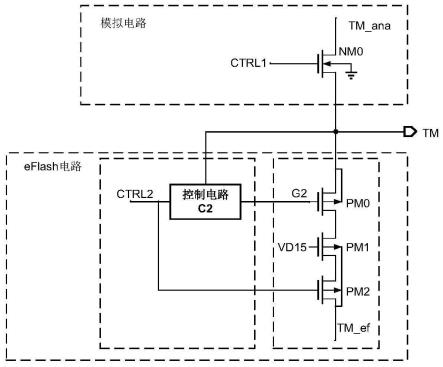

16.图1eflash电路和模拟电路共用测试pad的实现电路

17.图2改进型电平位移器电路

(五)具体实施方式:

18.下面,结合附图对本发明的具体实施方式进一步详细说明。

19.图1为本发明eflash电路和模拟电路共用测试pad的具体实现电路,展示了所述发明电路的基本结构,由mos开关管和改进型电平位移器控制电路构成。所述控制信号ctrl1,电压范围为0-2.75v;控制信号ctrl2,电压范围为0-2.3v;所述模拟电路待测信号tm_ana,电压范围为0.5-2.75v;所述eflash电路待测信号tm_ef,电压为4v;所述芯片测试pad tm,电压范围为0.5-4v。

20.图2为改进型电平位移器,在传统电平位移器中,增加pm3,其中pm3的栅极电位为vd25(2.3v电平的电源),以提升电平移位器的翻转下限。该电平位移器输入信号ctrl2的电压幅度为0-2.3v,电源电压vdd(tm)幅度为0.5-4v,此电平位移器实现2.3v电压幅度转换成4v幅度的功能,并且当待测电位tm小于vd25+vth_p(0.7v)时,pm3开关管截止,电平位移器不工作,防止漏电。

21.当tm测试eflash电路电位tm_ef时,nm0的栅极电位为0,nm0开关管截止,模拟测试电路不影响eflash输出电位的测试;pm2的栅极电位0,pm2开关管导通;pm0的栅极电为0,pm0开关管导通,pm1的栅极电位为1.5v,即pmos传输通路导通,tm输出eflash待测电位tm_ef(4v)。

22.当tm测试模拟电路电位tm_ana时,nm0的栅极电位为ctrl1(2.75v电位),nm0开关导通,模拟电路待测电平tm_ana传送到tm pad上。此时,eflash测试电路中的电平位移器的pm3的栅极电位为vd25,待测电位的最大值为2.75v,小于vd25+vth_p(0.7v)pm3开关管截

止,即电平位移器不工作。同时,pm2的栅极电位为vd25,待测电位tm_ana的最大值为2.75v,小于vd25+vth_p(0.7v)pm2开关管亦截止,即eflash测试电路完全关断且改进型电平位移器不工作,避免漏电。

23.以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的设计原则、技术方案之内,所做的任何修改、等同替换、改进等,均包含在本发明保护范围内。

技术特征:

1.一种eflash电路和模拟电路共用测试pad的电路结构,其特征在于包括nmos开关管nm0、pmos开关管pm0,pmos开关管pm1,pmos开关管pm2、控制电路c2,其中:所述nmos开关管nm0:nmos开关管nm0的源极接芯片测试pad tm,nmos开关管nm0的漏极接模拟电路待测电平tm_ana,nmos开关管nm0的栅极接控制信号ctrl1,nmos开关管nm0的衬底接地;所述pmos开关管pm0:pmos开关管pm0的源极和衬底接芯片测试pad tm,pmos开关管pm0的漏极接pmos开关管pm1的源极,pmos开关管pm0的栅极接控制电路c2的输出g2;所述pmos开关管pm1:pmos开关管pm1的源极接pmos开关管pm0的漏极,pmos开关管pm1的漏极接pmos开关管pm2的源极,pmos开关管pm1的栅极接vd15电平,pmos开关管pm1的衬底接eflash电路待测电平tm_ef;所述pmos开关管pm2:pmos开关管pm2的源极接pmos开关管pm1的漏极,pmos开关管pm2的漏极和衬底接eflash电路待测电平tm_ef,pmos开关管pm2的栅极接控制信号ctrl2。所述控制电路c2:输入端口接控制信号ctrl2,输出端口g2与pmos开关管pm0的栅极连接,电源端接芯片测试pad tm。2.根据权利要求1所述的电路结构,其特征在于所述控制电路c2由晶体管nm1、晶体管nm2、晶体管pm3、晶体管pm4、晶体管pm5和反相器inv1构成,其输入控制信号为ctrl2,输出信号为g2,电源为vdd;具体连接关系为:晶体管nm1的源极和衬底接地,晶体管nm1的栅极接反相器inv1的输出,晶体管nm1的漏极接晶体管pm4的漏极和晶体管pm5的栅极;晶体管pm4的漏极接晶体管nm1的漏极和晶体管pm5的栅极,晶体管pm4的源极接晶体管pm3的漏极和晶体管pm5的源极,晶体管pm4的衬底接电源vdd,晶体管pm4的栅极接晶体管pm5的漏极;晶体管nm2的源极和衬底接地,晶体管nm2的栅极接输入控制信号ctrl1,晶体管nm2的漏极接晶体管pm5的漏极、晶体管pm4的栅极;晶体管pm5的漏极接晶体管nm2的漏极、晶体管pm4的栅极,晶体管pm5的栅极接晶体管nm1的漏极和晶体管pm4的漏极和输出信号g1,晶体管pm5的源极接晶体管pm3的晶体管的漏极和晶体管pm4的源极,pm5的衬底接电源vdd;晶体管pm3的源极和衬底接电源vdd,晶体管pm3的漏极接晶体管pm4的源极和晶体管pm5的源极,晶体管pm3的栅极接固定电位vd25。

技术总结

本发明公开了一种eFlash电路和模拟电路共用测试PAD的电路结构。其中模拟测试电路采用NMOS控制传送0.5~2.75V电位到测试PAD上,eFlash测试电路采用PMOS控制传送4V电位到测试PAD。因两者在电源和控制方式上的差异,简单的连接在一起共用测试PAD容易引起漏电,因此设计此电路。本发明的特征在包括一个NMOS开关管,三个PMOS开关管和一个开关控制电路:所述MOS开关管在导通时可以正确传输待测电位,关闭时则处于截止状态;所述开关控制电路为改进型电平移位器电路,其输出信号施加在MOS开关管的栅极来控制MOS开关管的导通或截止。其优点在于当电源电位较低时,电平位移器不工作,避免漏电流产生。避免漏电流产生。避免漏电流产生。

技术研发人员:许延华 佟慧超 孟颖 白俊峰

受保护的技术使用者:北京中电华大电子设计有限责任公司

技术研发日:2022.10.17

技术公布日:2023/2/23

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1