DDRSDRAM信号校准装置与方法与流程

本发明涉及校准装置与方法,尤其涉及能够响应电压及/或温度的变化的ddrsdram信号校准装置与方法。

背景技术:

1、一般而言,于读取一双倍数据率同步动态随机存取存储器(ddr sdram)的数据时,该ddr sdram会发送数据选通(data strobe,dqs)信号与数据(dq)信号给一控制器。dqs信号按序包含三态部(tristate)、前置部、与多个时钟,该三态部是一先前存取操作与一当前读取操作之间的信号,该前置部用来提醒该控制器准备依据该多个时钟读取dq信号,该多个时钟接续该前置部。为了正确地让一取样电路依据dqs信号的该些时钟而非dqs信号的三态部来取样dq信号,该控制器利用一数据选通致能(dqs_en)信号的特定准位(例如:高准位)的期间来涵盖dqs信号的该些时钟的起迄;较佳情形下,该控制器令dqs_en信号的准位在dqs信号的前置部的中间位置从一原先准位变更为该特定准位,还依据ddr sdram所接收的一读取/写入命令将该dqs_en信号的准位恢复为该原先准位,从而dqs_en信号的特定准位的期间可正确地涵盖dqs信号的该些时钟而不包含dqs信号的三态部,借此该取样电路可依据dqs信号的正确的部分(亦即:dqs信号的时钟)来取样dq信号。

2、然而,纵使正确地找出dqs信号的前置部的位置,并利用该位置正确地设定dqs_en信号的准位改变的时间点,随着电压及/或温度的变化影响到电路的运行时序,该前置部的位置也会变化,这个问题在读取低功率双倍数据率同步动态随机存取存储器(lpddrsdram)的数据时特别需要重视,这是因为lpddr sdram的dqs信号的前置部的位置变化幅度可能会超过该前置部的长度,因此,在电压及/或温度变化后,该dqs_en信号的特定准位的期间可能就无法正确地涵盖dqs信号的该些时钟,从而该取样电路可能过早地依据错误的触发信号(例如:dqs信号的该三态部)取样dq信号而得到错误的读取数据,或者该取样电路可能过迟地取样dq信号而无法取得完整的读取数据。

3、针对前述问题,申请人先前提出一种解决方案(美国专利号:10978118)。然而,该解决方案可能有下列问题:

4、该解决方案取样前一笔dqs_en信号的延迟信号来判断dqs信号是否提早到来。然而,若前一次读取ddr sdram的数据的时间点与这一次读取数据的时间点之间之间隔过久,该解决方案无法取样到前一笔dqs_en信号的延迟信号,从而无法判断dqs信号是否提早到来。

5、该解决方案先拉高dqs信号的三态部的准位,再取样dqs信号的延迟信号,以判断dqs信号是否过早到来。然而,dqs的三态部的准位拉高后容易受到噪声影响,这使得取样dqs信号的延迟信号的结果不可靠。

技术实现思路

1、本公开的目的之一在于提供一种能够响应电压及/或温度的变化的ddr sdram信号校准装置与方法。

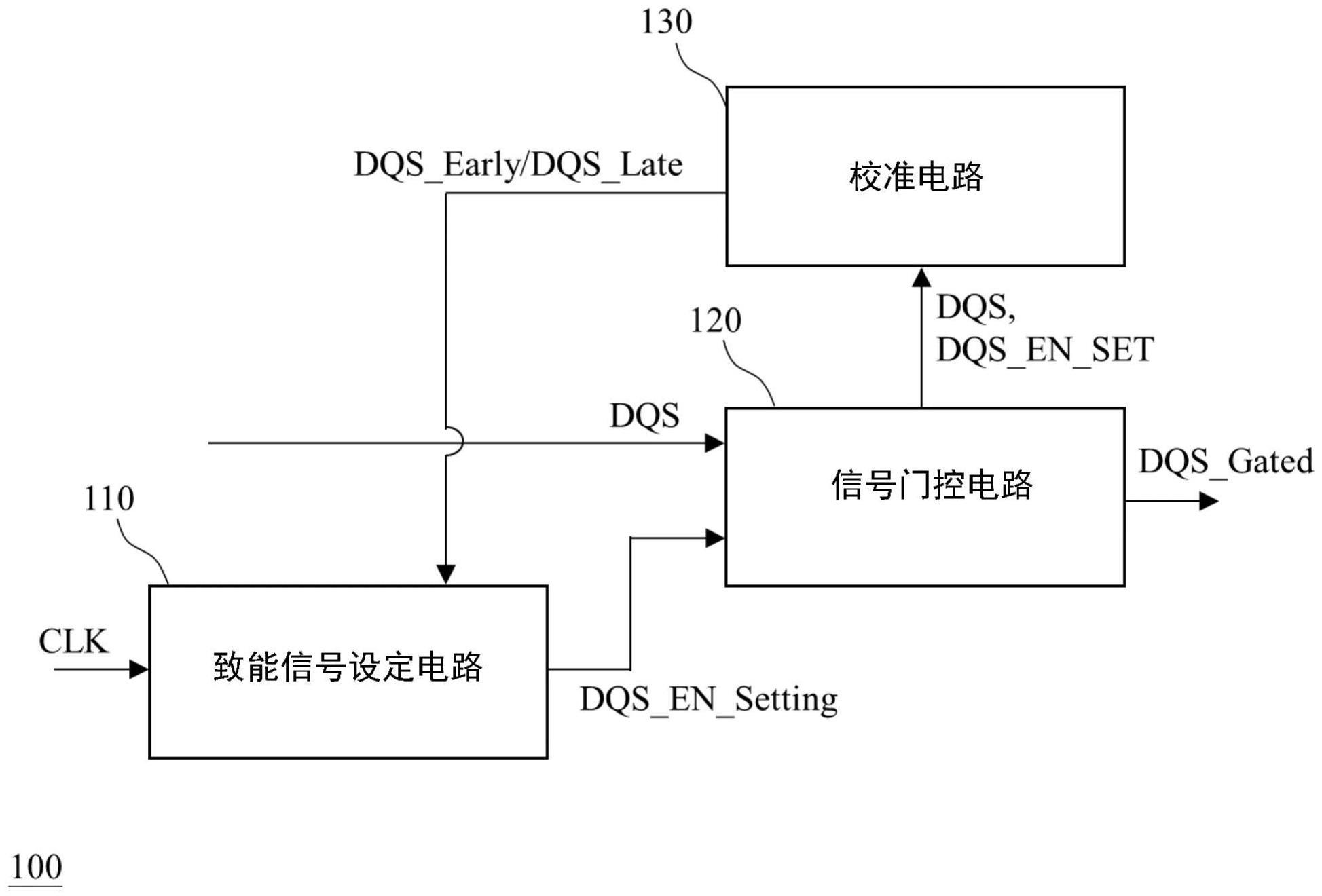

2、本公开的ddr sdram信号校准装置的一实施例包含一致能信号设定电路、一信号门控电路以及一校准电路。该致能信号设定电路用来产生数据选通(data strobe,dqs)致能设定。该信号门控电路耦接该致能信号设定电路,用来依据该数据选通致能设定产生一数据选通致能设定信号以及一数据选通致能信号,再依据该数据选通致能信号与一数据选通信号输出一门控数据选通信号。该校准电路耦接该致能信号设定电路与该信号门控电路,用来依据该数据选通致能设定信号产生一第一延迟信号,再依据该第一延迟信号产生一第二延迟信号;该校准电路进一步用来依据该第一延迟信号、该第二延迟信号与该数据选通信号输出一校正信号。该致能信号设定电路依据该校正信号维持或调整该数据选通致能设定。

3、本公开的ddr sdram信号校准方法的一实施例包含下列步骤:依据数据选通致能设定产生一数据选通致能设定信号以及一数据选通致能信号;依据该数据选通致能信号与一数据选通信号输出一门控数据选通信号;依据该数据选通致能设定信号产生一第一延迟信号;依据该第一延迟信号产生一第二延迟信号;以及依据该第一延迟信号、该第二延迟信号与该数据选通信号输出一校正信号,该校正信号用于维持或调整该数据选通致能设定。

4、有关本发明的特征、实作与技术效果,兹配合附图作优选实施例详细说明如下。

技术特征:

1.一种校准装置,包含:

2.如权利要求1所述的校准装置,其中该数据选通信号的一三态部的一信号准位为一低准位。

3.如权利要求2所述的校准装置,其中该校准电路依据该第一延迟信号与该数据选通信号产生该校正信号的一第一校正信号,该校准电路还依据该第二延迟信号与该数据选通信号产生该校正信号的一第二校正信号,从而该致能信号设定电路依据该第一校正信号与该第二校正信号维持或调整该数据选通致能设定。

4.如权利要求3所述的校准装置,其中该校准电路包含:

5.如权利要求4所述的校准装置,其中:

6.如权利要求1所述的校准装置,其中该数据选通信号的一三态部的一信号准位为一高准位。

7.如权利要求6所述的校准装置,其中该校准电路依据该第一延迟信号与该数据选通信号的反相信号产生该校正信号的一第一校正信号,该校准电路还依据该第二延迟信号与该数据选通信号的反相信号产生该校正信号的一第二校正信号,从而该致能信号设定电路依据该第一校正信号与该第二校正信号维持或调整该数据选通致能设定。

8.如权利要求7所述的校准装置,其中该校准电路包含:

9.如权利要求8所述的校准装置,其中:

10.一种校准方法,包含:

技术总结

本发明公开了一种DDR SDRAM信号校准装置与方法,能够响应电压及/或温度的变化。该校准装置包含:一致能信号设定电路,用来产生数据选通(Data Strobe,DQS)致能设定;一信号门控电路,耦接该致能信号设定电路,用来依据该数据选通致能设定产生一数据选通致能设定信号以及一数据选通致能信号,再依据该数据选通致能信号与一数据选通信号输出一门控数据选通信号;以及一校准电路,用来依据该数据选通致能设定信号产生一第一延迟信号,再依据该第一延迟信号产生一第二延迟信号,然后依据该第一延迟信号、该第二延迟信号与该数据选通信号输出一校正信号。该致能信号设定电路依据该校正信号维持或调整该数据选通致能设定。

技术研发人员:纪国伟,余俊锜,张志伟,周格至

受保护的技术使用者:瑞昱半导体股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!