具有高导电率及低互电容的位线以及相关设备、计算系统及方法与流程

本公开大体上涉及具有高导电率及低互电容的导电迹线,且更具体来说,涉及使用具有高导电率的导电材料形成的位线及位线之间的气隙。

背景技术:

1、对高密度装置的持续需求已驱使半导体装置制造商以或大致以制造工艺公差设计装置特征。例如,存储器装置中的位线可以或大致以工艺公差制造,其可导致位线相对较窄且相对靠近其他位线。换句话说,为使由位线占用的芯片面积或“基板面”尽可能小,可使位线尽可能窄且可使位线尽可能一起紧密间隔。

技术实现思路

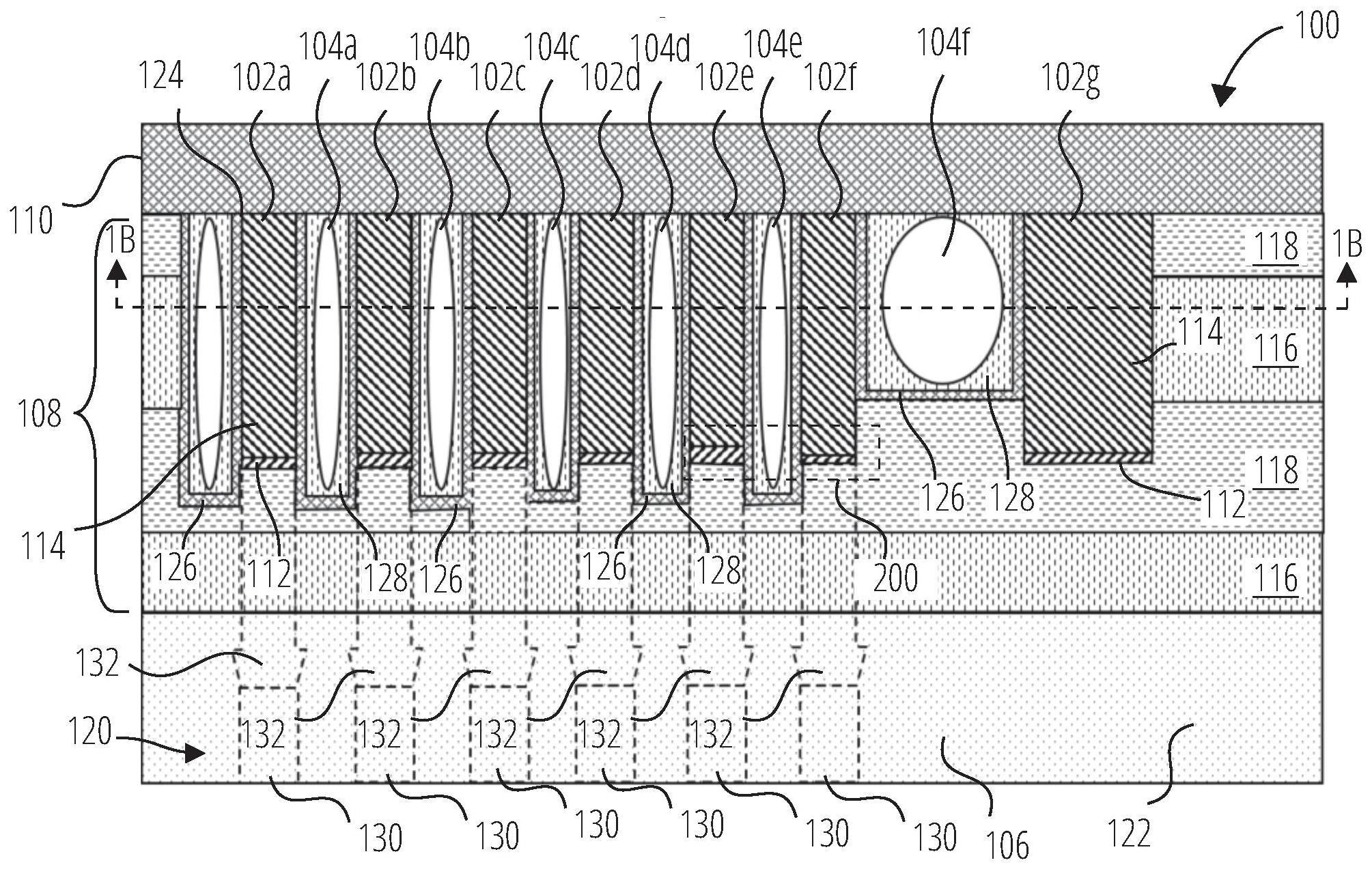

1、在一些实施例中,一种设备包含位线、所述位线之间的低k介电材料、所述位线之间的气隙、存储器单元串及将所述存储器单元串电连接到所述位线的触点。所述位线包含铜。所述低k介电材料机械地支撑所述位线。所述存储器单元串至少大体上垂直于所述位线延伸。

2、在一些实施例中,一种制造存储器装置的方法包含在竖直存储器单元串上方的电绝缘材料的位线沟槽中形成第一导电材料及移除所述电绝缘材料的在所述位线沟槽之间的部分。所述方法还包含在所述第一导电材料及所述电绝缘材料的剩余部分上保形地形成低k介电材料。所述方法进一步包含形成亚保形介电材料以在所述位线沟槽之间形成气隙及从所述位线沟槽移除所述第一导电材料的至少一部分。所述方法包含在所述位线沟槽中形成第二导电材料以替换所述所移除的第一导电材料,所述第二导电材料比所述第一导电材料更导电。

3、在一些实施例中,一种制造存储器装置的方法包含:在所述存储器装置的竖直存储器单元串上方的电绝缘材料中形成位线沟槽;在所述位线沟槽中形成第一导电材料;及移除所述第一导电材料的多余部分以暴露所述位线沟槽之间的所述电绝缘材料。所述方法还包含:移除所述电绝缘材料的在所述位线沟槽之间的部分;在所述第一导电材料及所述电绝缘材料的剩余部分上保形地形成低k介电材料;及形成亚保形介电材料以在所述位线沟槽内的所述第一导电材料上形成横向相邻于所述低k介电材料的气隙。所述方法进一步包含:移除所述亚保形介电材料及所述低k介电材料的一部分以暴露所述位线沟槽内的所述第一导电材料;使所述位线沟槽内的所述第一导电材料凹进;及在所述第一导电材料上方及在所述位线沟槽内形成第二导电材料。所述第二导电材料比所述第一导电材料更导电。

4、在一些实施例中,一种设备包含:位线,其包含铜;气隙,其在所述位线之间;低k介电材料,其在所述位线与所述气隙之间;字线;及存储器单元阵列,其包括对应于所述位线与所述字线之间的相交点的存储器单元。

5、在一些实施例中,一种计算系统包含:存储器单元阵列,其包含存储器单元;位线,其在所述存储器单元阵列上方;及低k介电材料,其在所述位线之间。所述位线电连接到所述存储器单元。所述位线包含第一导电材料及第二导电材料。所述第二导电材料比所述第一导电材料更导电。

技术特征:

1.一种设备,其包括:

2.根据权利要求1所述的设备,其进一步包括所述位线之间的亚保形介电材料,所述亚保形介电材料界定所述气隙。

3.根据权利要求2所述的设备,其中所述亚保形介电材料及所述气隙至少大体上由所述低k介电材料环绕。

4.根据权利要求1所述的设备,其中至少一些所述位线在第一部分中包括钨,且在第二部分包含所述铜。

5.根据权利要求4所述的设备,其中所述铜与所述钨之间的界面包括突入到所述铜中的所述钨的颗粒。

6.根据权利要求4所述的设备,其中所述位线中的第一位线中的所述铜与所述钨之间的第一界面与所述位线中的第二位线中的所述铜与所述钨之间的第二界面错位。

7.根据权利要求1到6中任一权利要求所述的设备,其进一步包括所述低k介电材料与所述位线之间的衬层材料。

8.根据权利要求7所述的设备,其中所述衬层材料包括钽或氮化钽。

9.一种制造存储器装置的方法,所述方法包括:

10.根据权利要求9所述的方法,其中:

11.根据权利要求9所述的方法,其中在所述沟槽中形成所述第二导电材料以替换所述所移除第一导电材料包括:

12.根据权利要求11所述的方法,其中形成所述衬层材料包括形成钽衬层材料。

13.根据权利要求9到12中任一权利要求所述的方法,其中在所述位线沟槽中形成所述第一导电材料包括在所述位线沟槽中形成钨。

14.根据权利要求9到12中任一权利要求所述的方法,其中在所述位线沟槽中形成所述第二导电材料以替换所述第一导电材料包括在所述位线沟槽中形成铜。

15.一种制造存储器装置的方法,所述方法包括:

16.根据权利要求15所述的方法,其中使所述位线沟槽内的所述第一导电材料凹进包括使用磷酸-乙酸-硝酸pan蚀刻化学品来蚀刻所述第一导电材料。

17.一种设备,其包括:

18.根据权利要求17所述的设备,其进一步包括经由至少所述位线电连接到所述存储器单元阵列的外围电路系统,所述外围电路系统包括列解码器、感测放大器、传送门、错误校正控制电路、输入/输出电路及行解码器中的一或多者。

19.根据权利要求17及18中任一权利要求所述的设备,其中所述位线包括:

20.根据权利要求19所述的设备,其中所述钨的颗粒在所述钨与所述铜之间的界面处突入到所述铜中。

21.根据权利要求19所述的设备,其中所述钨与所述铜之间的界面从位线到位线错位。

22.根据权利要求17及18中任一权利要求所述的设备,其进一步包括所述位线之间的亚保形介电材料,所述亚保形介电材料界定所述气隙。

23.一种计算系统,其包括:

24.根据权利要求23所述的计算系统,其进一步包括所述位线之间的亚保形介电材料,所述亚保形介电材料界定所述位线之间的气隙。

25.根据权利要求23所述的计算系统,其中所述第二导电材料包括铜。

26.根据权利要求23到25中任一权利要求所述的计算系统,其进一步包括:

技术总结

本发明公开具有高导电率及低互电容的位线以及相关设备、计算系统及方法。一种设备包含:位线,其包含铜;低k介电材料,其在所述位线之间;及气隙,其在所述位线之间。所述低k介电材料机械地支撑所述位线。一种制造存储器装置的方法包含:在电绝缘材料的位线沟槽中形成第一导电材料;移除所述位线沟槽之间的所述电绝缘材料的部分;在所述第一导电材料及所述电绝缘材料的剩余部分上保形地形成低k介电材料;及形成亚保形介电材料以在所述位线沟槽之间形成气隙。所述方法还包含:使所述第一导电材料凹进;及用第二导电材料替换所述第一导电材料的移除部分。

技术研发人员:A·N·斯卡伯勒,D·R·埃科诺米,J·S·布朗,J·D·霍普金斯,J·D·格林利,M·K·拉玛萨哈亚姆,R·J·克莱因

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!