存储器的制作方法

本申请涉及存储器,尤其涉及一种存储器。

背景技术:

1、伴随各种存储器的广泛使用,比如动态随机存取存储器(dynamic random accessmemory,简称dram)的使用非常广泛。实际应用中,为了保证产品的可靠性,需要对封装后的存储器进行测试。

2、因而,如何提高存储器的测试效率成为需要考虑的问题。

技术实现思路

1、本申请的实施例提供一种存储器,用以提高存储器的测试效率。

2、根据一些实施例,本申请提供一种存储器,包括:

3、压缩电路,其输入端接收通过多个数据输入输出引脚的传输路径传输的读取数据,用于对每个数据输入输出引脚的传输路径传输的读取数据分别进行压缩,获得多个压缩数据;

4、数据输入输出选择器,其第一输入端连接所述压缩电路的输出端,接收所述多个压缩数据,用于在测试模式下将所述多个压缩数据传输至目标数据输入输出引脚;

5、其中,所述目标数据输入输出引脚为所述多个数据输入输出引脚中的任意一个。

6、在一些实施例中,任意一个数据输入输出引脚的所有传输路径传输的读取数据相同时,若每个数据输入输出引脚对应的压缩数据均指示其对应的传输路径传输的读取数据中的每位数据均相同,所述多个压缩数据用于指示存储器正常,若部分数据输入输出引脚对应的压缩数据指示其对应的传输路径传输的读取数据中部分数据不同,所述多个压缩数据用于指示存储器存在故障。

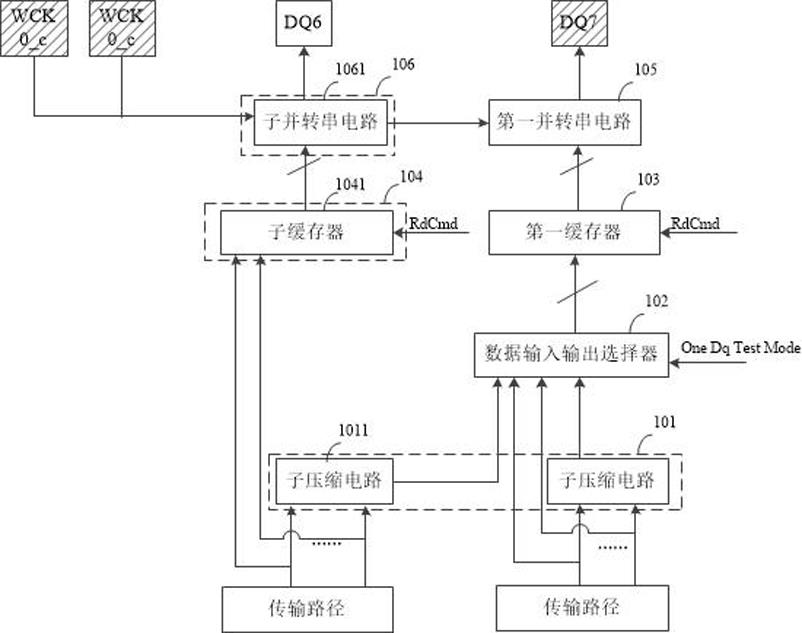

7、在一些实施例中,所述压缩电路包括多个子压缩电路,每个子压缩电路的输入端接收一个数据输入输出引脚的传输路径传输的读取数据;

8、每个子压缩电路用于将其对应的数据输入输出引脚的传输路径传输的读取数据进行压缩,获得对应的压缩数据。

9、在一些实施例中,每个所述子压缩电路包括异或门和非门;

10、所述异或门的输入端作为对应的所述子压缩电路的输入端,接收一个数据输入输出引脚的传输路径传输的读取数据,所述异或门的输出端连接所述非门的输入端,所述非门的输出端作为对应的所述子压缩电路的输出端。

11、在一些实施例中,所述数据输入输出选择器的第二输入端接收通过所述目标数据输入输出引脚的传输路径传输的读取数据,用于在工作模式下将通过所述目标数据输入输出引脚的传输路径传输的读取数据传输至所述目标数据输入输出引脚。

12、在一些实施例中,所述数据输入输出选择器包括多个第一选择器,每个第一选择器对应所述目标数据输入输出引脚的一个传输路径;

13、每个所述第一选择器的第一输入端接收一个数据输入输出引脚对应的压缩数据,每个所述第一选择器的第二输入端接收通过所述目标数据输入输出引脚的传输路径传输的读取数据中的一位数据;

14、每个所述第一选择器用于在测试模式下将其对应的数据输入输出引脚的压缩数据传输至所述目标数据输入输出引脚,在工作模式下将通过所述目标数据输入输出引脚的传输路径传输的读取数据中的一位数据传输至所述目标数据输入输出引脚。

15、在一些实施例中,所述存储器包括:

16、第一缓存器,其输入端连接所述数据输入输出选择器,用于存储所述数据输入输出选择器输出的数据,并在接收到读命令后,输出所述数据输入输出选择器输出的数据。

17、在一些实施例中,所述存储器包括:

18、第一并转串电路,其输入端连接所述第一缓存器,接收所述第一缓存器输出的数据,将所述第一缓存器输出的数据进行并转串并输出至所述目标数据输入输出引脚。

19、在一些实施例中,在所述测试模式下,所述第一并转串电路具体用于按照所述数据输入输出引脚的顺序对所述多个压缩结果进行排序,以将所述多个压缩数据转换为串行数据。

20、在一些实施例中,所述多个数据输入输出引脚包括目标数据输入输出引脚和其他数据输入输出引脚;

21、所述存储器包括:

22、第二缓存器,其输入端接收通过所述其他数据输入输出引脚的传输路径传输的读取数据,用于存储通过所述其他数据输入输出引脚的传输路径传输的读取数据,并在接收到读命令后,输出通过所述其他数据输入输出引脚的传输路径传输的读取数据。

23、在一些实施例中,所述第二缓存器包括多个子缓存器,每个子缓存器的输入端接收通过所述其他数据输入输出引脚中一个数据输入输出引脚的传输路径传输的读取数据,用于存储其对应的数据输入输出引脚的传输路径传输的读取数据,并在接收到所述读命令后,输出其对应的数据输入输出引脚的传输路径传输的读取数据。

24、在一些实施例中,所述存储器包括:

25、第二并转串电路,其输入端连接所述第二缓存器,接收所述第二缓存器输出的数据,将所述第二缓存器输出的数据进行并转串并输出至所述其他数据输入输出引脚。

26、在一些实施例中,所述第二并转串电路包括多个子并转串电路,每个子并转串电路的输入端连接一个子缓存器,每个子并转串电路接收对应子缓存器输出的数据,将对应子缓存器输出的数据进行并转串并输出至所述其他数据输入输出引脚中的一个数据输入输出引脚。

27、在一些实施例中,所述存储器还包括:

28、数据掩码引脚,其接收校验码数据,所述存储器基于所述校验码数据对所述多个数据输入输出引脚的传输路径传输的读取数据进行校验。

29、在一些实施例中,所述数据掩码引脚包括第一数据掩码引脚和第二数据掩码引脚,所述第一数据掩码引脚接收第一校验码数据,所述第二数据掩码引脚接收第二校验码数据;

30、所述存储器基于所述第一校验码数据对所述多个数据输入输出引脚中的部分数据输入输出引脚的传输路径传输的数据进行校验,基于所述第二校验码数据对所述多个数据输入输出引脚中的剩余数据输入输出引脚的传输路径传输的数据进行校验。

31、本申请提供的存储器中,压缩电路的输入端接收通过多个数据输入输出引脚的传输路径传输的读取数据,并对每个数据输入输出引脚的传输路径传输的读取数据分别进行压缩,获得多个压缩数据。数据输入输出选择器的第一输入端连接压缩电路的输出端,接收压缩电路输出的多个压缩数据,并在测试模式下将多个压缩数据传输至存储器中的多个数据输入输出引脚中的任意一个数据输入输出引脚,从而在测试时只需要使用一个数据输入输出引脚,减少数据输入输出引脚的使用数量,增加同时测试的存储器的数量,提高测试效率。

技术特征:

1.一种存储器,其特征在于,包括:

2.根据权利要求1所述的存储器,其特征在于,任意一个数据输入输出引脚的所有传输路径传输的读取数据相同时,若每个数据输入输出引脚对应的压缩数据均指示其对应的传输路径传输的读取数据中的每位数据均相同,所述多个压缩数据用于指示存储器正常,若部分数据输入输出引脚对应的压缩数据指示其对应的传输路径传输的读取数据中部分数据不同,所述多个压缩数据用于指示存储器存在故障。

3.根据权利要求2所述的存储器,其特征在于,所述压缩电路包括多个子压缩电路,每个子压缩电路的输入端接收一个数据输入输出引脚的传输路径传输的读取数据;

4.根据权利要求3所述的存储器,其特征在于,每个所述子压缩电路包括异或门和非门;

5.根据权利要求1所述的存储器,其特征在于,所述数据输入输出选择器的第二输入端接收通过所述目标数据输入输出引脚的传输路径传输的读取数据,用于在工作模式下将通过所述目标数据输入输出引脚的传输路径传输的读取数据传输至所述目标数据输入输出引脚。

6.根据权利要求5所述的存储器,其特征在于,所述数据输入输出选择器包括多个第一选择器,每个第一选择器对应所述目标数据输入输出引脚的一个传输路径;

7.根据权利要求5所述的存储器,其特征在于,所述存储器包括:

8.根据权利要求7所述的存储器,其特征在于,所述存储器包括:

9.根据权利要求8所述的存储器,其特征在于,在所述测试模式下,所述第一并转串电路具体用于按照所述数据输入输出引脚的顺序对所述多个压缩结果进行排序,以将所述多个压缩数据转换为串行数据。

10.根据权利要求9所述的存储器,其特征在于,所述多个数据输入输出引脚包括目标数据输入输出引脚和其他数据输入输出引脚;

11.根据权利要求10所述的存储器,其特征在于,所述第二缓存器包括多个子缓存器,每个子缓存器的输入端接收通过所述其他数据输入输出引脚中一个数据输入输出引脚的传输路径传输的读取数据,用于存储其对应的数据输入输出引脚的传输路径传输的读取数据,并在接收到所述读命令后,输出其对应的数据输入输出引脚的传输路径传输的读取数据。

12.根据权利要求10所述的存储器,其特征在于,所述存储器包括:

13.根据权利要求12所述的存储器,其特征在于,所述第二并转串电路包括多个子并转串电路,每个子并转串电路的输入端连接一个子缓存器,每个子并转串电路接收对应子缓存器输出的数据,将对应子缓存器输出的数据进行并转串并输出至所述其他数据输入输出引脚中的一个数据输入输出引脚。

14.根据权利要求1-13中任意一项所述的存储器,其特征在于,所述存储器还包括:

15.根据权利要求14所述的存储器,其特征在于,所述数据掩码引脚包括第一数据掩码引脚和第二数据掩码引脚,所述第一数据掩码引脚接收第一校验码数据,所述第二数据掩码引脚接收第二校验码数据;

技术总结

本申请提供一种存储器,包括压缩电路和数据输入输出选择器,压缩电路的输入端接收通过多个数据输入输出引脚的传输路径传输的读取数据,并对每个数据输入输出引脚的传输路径传输的读取数据分别进行压缩,获得多个压缩数据。数据输入输出选择器的第一输入端连接压缩电路的输出端,接收多个压缩数据,用于在测试模式下将多个压缩数据传输至目标数据输入输出引脚,其中,目标数据输入输出引脚为多个数据输入输出引脚中的任意一个。本申请的方案,在存储器的测试过程中,减少存储器的数据输入输出引脚的使用数量,增加同时测试的存储器的数量,提高测试效率。

技术研发人员:王佳

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!