存储芯片、存储设备以及计算设备的制作方法

本申请涉及存储领域,并且更具体地,涉及一种存储芯片、存储设备以及计算设备。

背景技术:

1、在数据时代,存储芯片的可靠性体现了存储芯片的性能,如何正确读取存储芯片中存储的数据,避免在读取数据的过程中出现较高的原始比特误码率(rowbiterrorrate,rber)成为业界人士关注的问题。

2、在一些场景中,存储芯片中的存储单元由于受自身非晶物理性质以及刻蚀工艺引入的缺陷影响,其开启阈值电压会随着时间和温度而发生漂移,从而导致在读取数据的过程中出现过高的rber。

3、因此,如何提高数据读取的准确性,避免读取数据的过程中出现过高的rber成为亟需要解决的技术问题。

技术实现思路

1、本申请提供一种存储芯片、存储设备以及计算设备,该存储芯片能够提高数据读取的准确性。

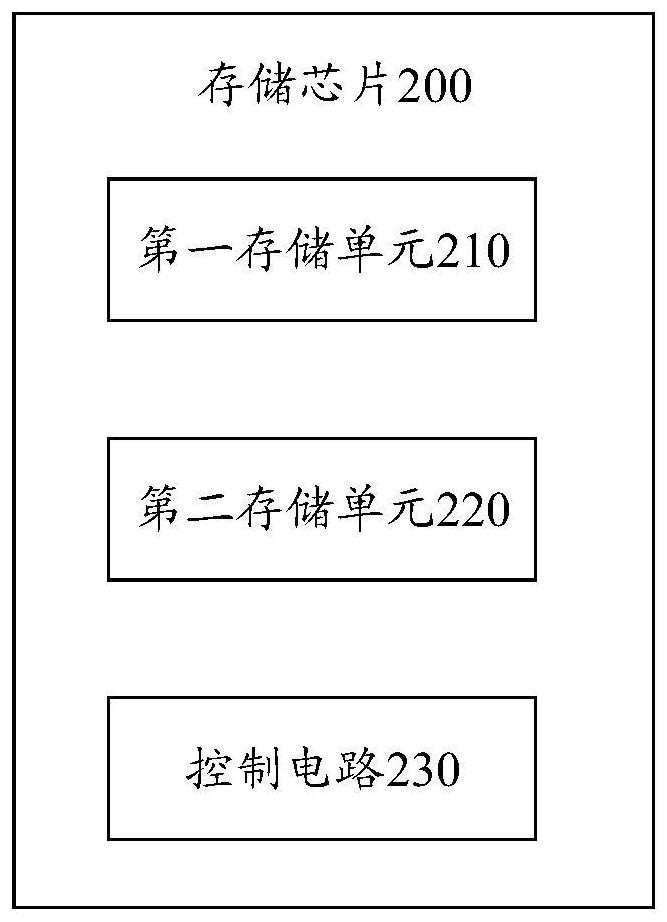

2、第一方面,提供了一种存储芯片,包括:第一存储单元,第二存储单元以及控制电路,其中,第一存储单元存储第一数据,第二存储单元存储第二数据,第二数据为预设数据,控制电路用于从该第一存储单元读出第三数据,从该第二存储单元读出第四数据,比较该第四数据与该第二数据,基于该第四数据与该第二数据相同的比较结果,确定该第一存储单元的读出结果正确,将该第三数据作为该第一数据输出。

3、上述存储芯片中的控制电路可以在从第二存储单元中读出的第四数据和第二存储单元中存储的预设的第二数据相同的情况下,从而确认第一存储单元的读出结果正确,并将从第一存储单元读出的第三数据作为输出,这样,可以提高数据读取的准确性。

4、结合第一方面,在第一方面的某些实现方式中,基于该第四数据与该第二数据不相同的比较结果,该控制电路丢弃该第三数据,并改变读激励信号,以再次对该第一存储单元和该第二存储单元执行读操作,并对读操作的结果进行比较,以确认该第一存储单元的读取结果是否正确。

5、结合第一方面,在第一方面的某些实现方式中,该控制电路预设有n个读激励信号,在每执行一次读操作后,基于该第四数据与该第二数据不相同的比较结果,改变一次读激励信号,当该读激励信号为第n个读激励信号时,且该第四数据与该第二数据不相同时,则反馈读取失败。

6、结合第一方面,在第一方面的某些实现方式中,该控制电路包括判决子电路,该判决子电路用于比较该第四数据与该第二数据。

7、结合第一方面,在第一方面的某些实现方式中,该控制电路包括电压选择子电路,该电压选择子电路用于提供该n个读激励信号。

8、结合第一方面,在第一方面的某些实现方式中,该存储芯片还包括第三存储单元,该第三存储单元用于存储第五数据,该第五数据为预设数据,且不同于该第二数据,该控制电路还用于从该第三存储单元读出第六数据,并比较该第六数据与该第五数据,并基于该第六数据与该第五数据相同,该第四数据与该第二数据相同的比较结果,确定该第一存储单元的读出结果正确,将该第三数据作为该第一数据输出。

9、结合第一方面,在第一方面的某些实现方式中,该第一存储单元与该第二存储单元为相变存储单元、铁电存储单元、磁性随机存储单元、阻变存储单元、浮栅晶体管。

10、第二方面,提供了一种数据处理的方法,包括:从第一存储单元读出第三数据,从第二存储单元读出第四数据,基于该第四数据与该第二数据相同的比较结果,确定该第一存储单元的读出结果正确,将该第三数据作为第一数据输出,第一存储单元存储有第一数据,第二存储单元存储有第二数据,第二数据为预设数据。

11、结合第二方面,在第二方面的某些实现方式中,该方法还包括:基于该第四数据与该第二数据不相同的比较结果,丢弃该第三数据,并改变读激励信号,以再次对该第一存储单元和该第二存储单元执行读操作,并对读操作的结果进行比较,以确认该第一存储单元的读取结果是否正确。

12、结合第二方面,在第二方面的某些实现方式中,该方法还包括:在每执行一次读操作后,基于该第四数据与该第二数据不相同的比较结果,改变一次读激励信号,当该读激励信号为预设的n个读激励信号中的第n个读激励信号时,且该第四数据与该第二数据不相同时,则反馈读取失败。

13、结合第二方面,在第二方面的某些实现方式中,该方法还包括:从第三存储单元读出第六数据,比较该第六数据与该第五数据,基于该第六数据与该第五数据相同,且该第四数据与该第二数据相同的比较结果,确定该第一存储单元的读出结果正确,将该第三数据作为该第一数据输出,第三存储单元存储有第五数据该第五数据为预设数据,且不同于该第二数据。

14、结合第二方面,在第二方面的某些实现方式中,该第一存储单元与该第二存储单元为相变存储单元、铁电存储单元、磁性随机存储单元、阻变存储单元、浮栅晶体管。

15、第三方面,提供了一种存储芯片,包括:读取模块,处理模块,其中,读取模块用于从第一存储单元读出第三数据,并从第二存储单元读出第四数据,第一存储单元存储有第一数据,第二存储单元存储有第二数据,该第二数据为预设数据;处理模块用于比较该第四数据与该第二数据,并基于该第四数据与该第二数据相同的比较结果,确定该第一存储单元的读出结果正确,将该第三数据作为该第一数据输出。

16、结合第三方面,在第三方面的某些实现方式中,该处理模块还用于基于该第四数据与该第二数据不相同的比较结果,丢弃该第三数据,并改变读激励信号,以再次对该第一存储单元和该第二存储单元执行读操作,并对读操作的结果进行比较,以确认该第一存储单元的读取结果是否正确。

17、结合第三方面,在第三方面的某些实现方式中,该处理模块还用于在每执行一次读操作后,基于该第四数据与该第二数据不相同的比较结果,改变一次读激励信号,当该读激励信号为预设的n个读激励信号中的第n个读激励信号时,且该第四数据与该第二数据不相同时,则反馈读取失败。

18、结合第三方面,在第三方面的某些实现方式中,该读取模块还用于从第三存储单元读出第六数据,该第三存储单元存储有第五数据该第五数据为预设数据,且不同于该第二数据;该处理模块,还用于比较该第六数据与该第五数据,基于该第六数据与该第五数据相同,且该第四数据与该第二数据相同的比较结果,确定该第一存储单元的读出结果正确,将该第三数据作为该第一数据输出。

19、结合第三方面,在第三方面的某些实现方式中,该第一存储单元与该第二存储单元为相变存储单元、铁电存储单元、磁性随机存储单元、阻变存储单元、浮栅晶体管。

20、第四方面,提供了一种存储设备,包括控制器和如第一方面或第一方面任意一种可能的实现方式中的存储芯片。

21、第五方面,提供了一种计算设备,包括如第四方面中的存储设备。

技术特征:

1.一种存储芯片,其特征在于,所述存储芯片包括:

2.根据权利要求1所述的存储芯片,其特征在于,

3.根据权利要求2所述的存储芯片,其特征在于,所述控制电路预设有n个读激励信号,在每执行一次读操作后,基于所述第四数据与所述第二数据不相同的比较结果,改变一次读激励信号,当所述读激励信号为第n个读激励信号时,且所述第四数据与所述第二数据不相同时,则反馈读取失败。

4.根据权利要求1至3中任一项所述的存储芯片,其特征在于,所述控制电路包括判决子电路,所述判决子电路用于比较所述所述第四数据与所述第二数据。

5.根据权利要求3或4所述的存储芯片,其特征在于,所述控制电路包括电压选择子电路,所述电压选择子电路用于提供所述n个读激励信号。

6.根据权利要求1至5中任一项所述的存储芯片,其特征在于,所述存储芯片还包括第三存储单元,所述第三存储单元用于存储第五数据,所述第五数据为预设数据,且不同于所述第二数据,所述控制电路还用于从所述第三存储单元读出第六数据,并比较所述第六数据与所述第五数据,并基于所述第六数据与所述第五数据相同,所述第四数据与所述第二数据相同的比较结果,确定所述第一存储单元的读出结果正确,将所述第三数据作为所述第一数据输出。

7.根据权利要求1至6中任一项所述的存储芯片,其特征在于,所述第一存储单元与所述第二存储单元为相变存储单元、铁电存储单元、磁性随机存储单元、阻变存储单元、浮栅晶体管。

8.一种数据处理的方法,其特征在于,包括:

9.根据权利要求8所述的方法,其特征在于,所述方法还包括:

10.根据权利要求9所述的方法,其特征在于,所述方法还包括:

11.根据权利要求8至10中任一项所述的方法,其特征在于,所述方法还包括:

12.根据权利要求8至11中任一项所述的方法,其特征在于,所述第一存储单元与所述第二存储单元为相变存储单元、铁电存储单元、磁性随机存储单元、阻变存储单元、浮栅晶体管。

13.一种存储设备,其特征在于,包括控制器以及如权利要求1至7中任一项所述的存储芯片,所述控制器用于控制将数据存储至所述存储芯片。

14.一种计算设备,其特征在于,包括处理器及如权利要求13所述的存储设备,所述处理器用于将数据存储至所述存储设备。

技术总结

一种存储芯片、存储设备以及计算设备,该存储芯片包括:第一存储单元,第二存储单元以及控制电路,其中,第一存储单元存储第一数据,第二存储单元存储第二数据,第二数据为预设数据,控制电路用于从所述第一存储单元读出第三数据,从所述第二存储单元读出第四数据,比较所述第四数据与所述第二数据,基于所述第四数据与所述第二数据相同的比较结果,确定所述第一存储单元的读出结果正确,将所述第三数据作为所述第一数据输出。该存储芯片能够提高数据读取的准确性。

技术研发人员:王成旭,陈一峰,童浩,谭海波

受保护的技术使用者:华为技术有限公司

技术研发日:

技术公布日:2024/6/26

- 还没有人留言评论。精彩留言会获得点赞!