用于存储器的改进的定时电路的制作方法

本公开涉及具有存储器的装置,具体涉及具有并入改进的跟踪电路的存储器的电子装置和集成电路(ic)。

背景技术:

1、存储器是无线通信设备的重要组件。近年来,无线通信技术和设备(例如,蜂窝电话、平板计算机、笔记本计算机等)越来越受欢迎和越来越多被使用。这些电子装置的复杂性日益增加,并且现在通常并入多个处理器(例如,基带处理器和/或应用处理器)以及允许用户运行复杂且功率密集的软件应用(例如,音乐播放器、web浏览器、视频流应用等)的其他ic。随着性能需求的增加,用于无线通信应用的ic可以并入多个处理器和存储器。存储器可以具有不同的存储器阵列大小和不同尺寸或配置的存储器阵列。

2、一个设计挑战是降低设计不同阵列大小的存储器的复杂性。例如,存储器的存储器阵列可以由存储器编译器生成。然而,可能不容易生成操作不同存储器阵列大小的存储器的定时电路。一个问题是定时电路平衡不同存储器阵列大小的存储器的性能和可靠性。

技术实现思路

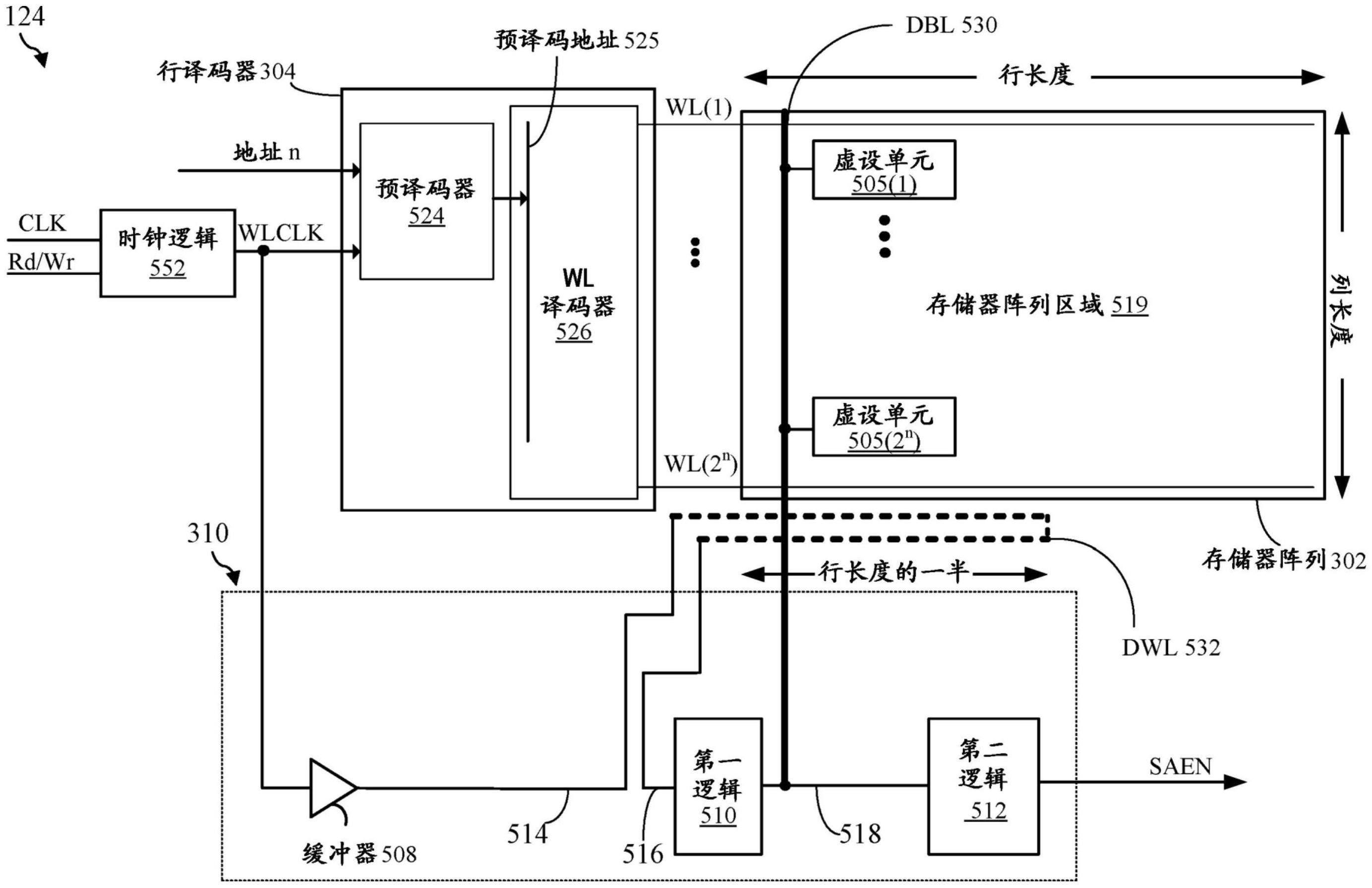

1、公开了一种存储器的各方面。在一个实现中,该存储器包括多个存储器单元、耦合到多个存储器单元的字线、耦合到多个存储器单元中的一个存储器单元的感测放大器、以及被配置为启用感测放大器的定时电路。定时电路包括延迟级和虚设字线。虚设字线被配置为模仿(emulate)字线的至少一部分。

2、公开了一种用于操作存储器的方法的各方面。在一个实现中,该方法包括断言耦合到多个存储器单元的字线并且启用耦合到多个存储器单元中的一个存储器单元的感测放大器。启用感测放大器基于使信号流过延迟级和虚设字线。虚设字线被配置为模仿字线的至少一部分。

3、公开了一种装置的方面。在一个实现中,该装置包括第一存储器,该第一存储器具有第一数目的存储器单元和耦合到第一数目的存储器单元的第一字线。第二存储器包括第二数目的存储器单元和耦合到第二数目的存储器单元的第二字线。第一存储器和第二存储器中的每一个包括用于启用存储器操作的定时电路。定时电路包括被配置为与第三数目的存储器单元的负载相对应的延迟级。第三数目的存储器单元与第一数目的存储器单元不同。

4、公开了一种用于操作第一存储器和第二存储器的方法的各方面。在一个实现中,该方法包括:断言在第一存储器中的耦合到第一数目的存储器单元的第一字线,经由第一延迟级来启用第一存储器的存储器操作,断言在第二存储器中的耦合到第二数目的存储器单元的第二字线,以及经由第二延迟级来启用第二存储器的存储器操作。第一延迟级和第二延迟级被配置为与第三数目的存储器单元的负载相对应。第三数目的存储器单元与第一数目的存储器单元不同。

5、应当理解,从以下详细描述中本领域技术人员将容易明白装置和方法的其他方面,其中通过图示的方式示出和描述了装置和方法的各个方面。如将认识到的,这些方面可以以其他和不同的形式来实现,并且这些方面的细节能够在各种其他方面进行修改。因此,附图和详细描述在本质上被认为是说明性的而不是限制性的。

技术特征:

1.一种存储器(124-1;124-2),包括:

2.根据权利要求1所述的存储器(124-1;124-2),其中所述定时电路(810)被配置为针对不同配置的存储器提供所述字线(wl(1))的不同跟踪。

3.根据权利要求1所述的存储器(124-1;124-2),其中所述定时电路进一步耦合到独立于字线译码器(526)的字线时钟或时钟逻辑(552)。

4.根据权利要求1所述的存储器(124-1;124-2),还包括:

5.根据权利要求1所述的存储器(124-1;124-2),其中所述字线(wl(1))的所述至少一部分小于所述字线(wl(1))的整体。

6.根据权利要求1所述的存储器(124-1;124-2),其中所述字线(wl(1))的所述至少一部分是所述字线(wl(1))的长度的约一半。

7.根据权利要求3所述的存储器(124-1;124-2),其中所述字线译码器(526)还被配置为驱动所述字线(wl(1)),其中所述延迟级(809)被配置为模仿对应于所述字线译码器(526)的一部分的延迟,该部分包括地址译码器(524)。

8.根据权利要求3所述的存储器(124-1;124-2),其中所述字线译码器(526)还被配置为驱动所述字线(wl(1)),其中所述字线译码器(526)被配置为输出至少一个译码地址,并且所述延迟级(809)被配置为通过输出虚设译码地址来模仿所述字线译码器(526)。

9.一种操作存储器(124-1;124-2)的方法,包括:

10.根据权利要求9所述的方法,其中所述定时电路(810)被配置为针对不同配置的存储器提供所述字线(wl(1))的不同跟踪。

11.根据权利要求9所述的方法,其中所述定时电路进一步耦合到独立于字线译码器(526)的字线时钟或时钟逻辑(552)。

12.根据权利要求9所述的方法,其中启用所述感测放大器进一步基于操作虚设位线,

13.根据权利要求9所述的方法,其中所述字线(wl(1))的所述至少一部分小于所述字线(wl(1))的整体。

14.根据权利要求9所述的方法,其中所述字线(wl(1))的所述至少一部分是所述字线(wl(1))的长度的约一半。

15.根据权利要求11所述的方法,其中所述字线译码器(526)还被配置为驱动所述字线(wl(1)),其中所述延迟级(809)被配置为模仿对应于所述字线译码器(526)的一部分的延迟,该部分包括地址译码器(524)。

16.根据权利要求11所述的方法,其中所述字线译码器(526)还被配置为驱动所述字线(wl(1)),其中所述字线译码器(526)被配置为输出至少一个译码地址,并且所述延迟级(809)被配置为通过输出虚设译码地址来模仿所述字线译码器(526)。

技术总结

呈现了一种存储器。该存储器包括多个存储器单元、耦合到多个存储器单元的字线、耦合到多个存储器单元中的一个存储器单元的感测放大器、以及被配置为启用感测放大器的定时电路。定时电路包括延迟级和虚设字线。虚设字线被配置为模仿字线的至少一部分。呈现了一种装置。该装置包括第一存储器,第一存储器具有耦合到第一数目的存储器单元的第一字线。第二存储器具有耦合到第二数目的存储器单元的第二字线。第一存储器和第二存储器中的每一个包括用于启用存储器操作的定时电路。定时电路包括与第三数目的存储器单元的负载相对应的延迟级。第三数目与第一数目不同。

技术研发人员:S·戈什,晶昌镐

受保护的技术使用者:高通股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!