动态随机存取存储器阵列电路及其写入操作中的行驱动方法与流程

本公开涉及半导体技术的领域,具体地,本公开涉及动态随机存取存储器阵列电路及其写入操作中的行驱动方法。

背景技术:

1、从二十世纪七十年代英特尔公司(intel corporation)发明动态随机存取存储器(dynamic random access memory,dram)以来,dram被广泛应用于各类计算或控制电子电路系统中。随着半导体制造工艺的发展,dram的制造从使用逻辑工艺逐渐演变为使用专用dram制造工艺,这使得dram脱离逻辑芯片,成为片外存储器。dram单元电路通常由一个晶体管和一个电容器构成(1t1c结构),具有存储密度高的优点,已成为计算机系统的重要组成部分。

2、dram作为动态随机存取存储器,依靠电容来存储数据,由于晶体管的漏电,存储在电容中的数据会随着时间推移而逐渐消失,所以必须在数据不能被读取电路正确读取之前对数据进行刷新操作。然而,刷新操作会带来额外的功耗以及中断系统运行等问题。特别是随着半导体工艺尺度的缩小,dram中存储数据的电容也随之缩小,能够存储的电荷也相应减少。此外,工艺尺度缩小还使得电源电压vdd减小,用于表示数据0和数据1的电压之间的电压差(以下称为0/1数据电压差)也相应减小。此外,工艺尺度缩小还使得晶体管的漏电变大。综上所述,随着工艺尺度的缩小,dram存储节点存储的0/1数据电压差减小,漏电速度快,数据保持时间变短,刷新操作带来的高功耗、对系统操作的频繁中断等问题也逐渐凸显。

3、在本背景技术部分中公开的以上信息仅用于理解本发明构思的背景,并且因此它可能包含不构成现有技术的信息。

技术实现思路

1、为了解决现有技术中存在的以上问题,本公开提出了新型的动态随机存取存储器阵列电路及其写入操作中的行驱动方法。

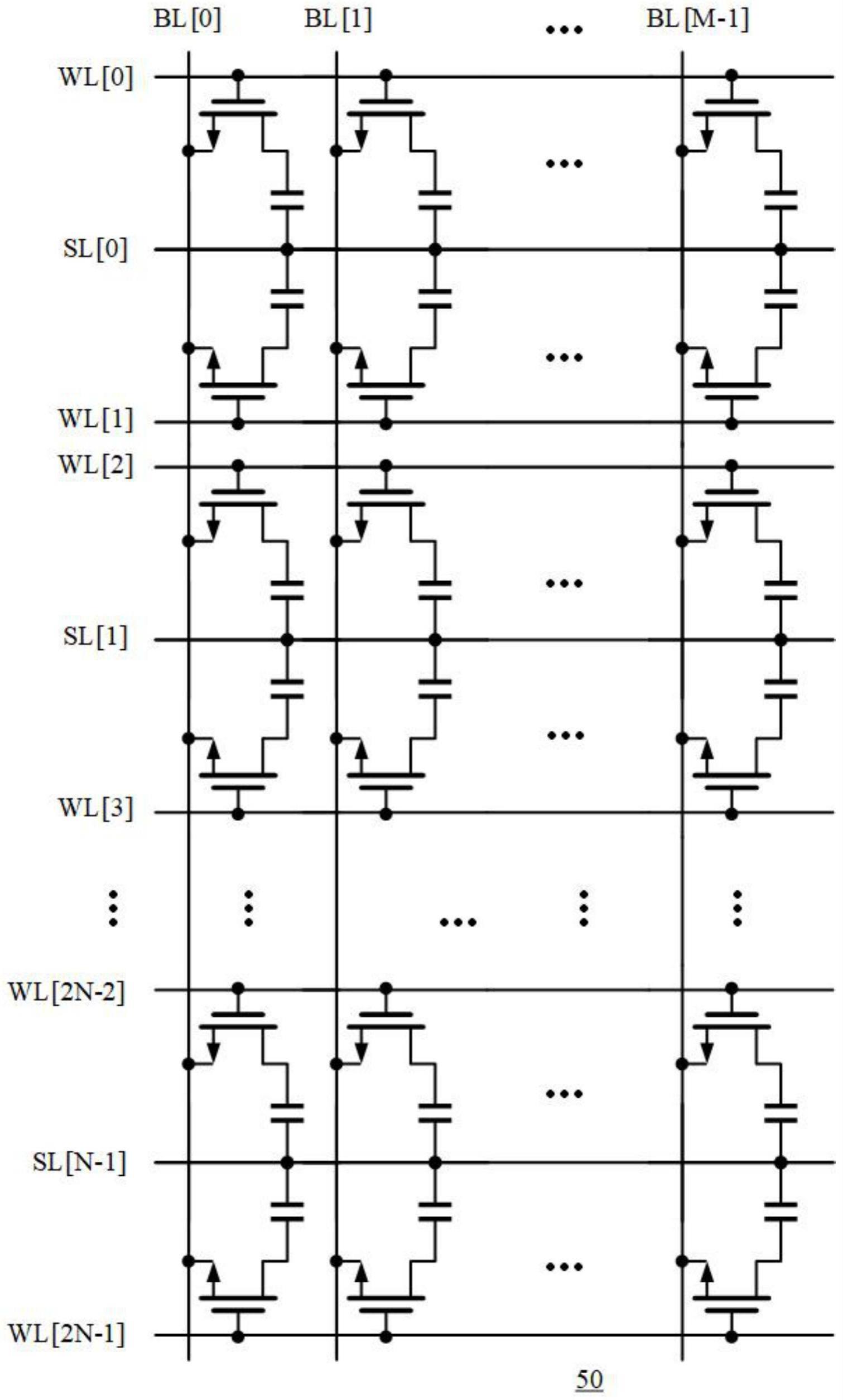

2、根据本公开的一个方面,提供了一种动态随机存取存储器阵列电路,包括2n行m列动态随机存取存储器单元电路,其中,m和n是大于零的自然数,其中,动态随机存取存储器单元电路中的每一个包括:n型存取晶体管,其栅极连接到字线并且其第一源/漏极连接到位线;以及存储电容器,其第一极板连接到n型存取晶体管的第二源/漏极并且其第二极板连接到源极线,其中,在写入操作中,字线在地电压、高于或等于电源电压的第一电压以及n型存取晶体管的阈值电压和第一电压之间的第二电压操作,以及其中,在写入操作中,当字线在第二电压操作时,源极线在电源电压操作,其中,在动态随机存取存储器阵列电路中,第2n行和第2n+1行动态随机存取存储器单元电路共用一个源极线,其中0≤n≤n-1。

3、根据本公开的另一方面,提供了一种用在根据本公开的上述方面的动态随机存取存储器阵列电路的写入操作中的行驱动方法,包括:通过对行地址进行预处理来隔行驱动所述动态随机存取存储器阵列电路中包括的各行动态随机存取存储器单元电路。

4、根据本公开的动态随机存取存储器阵列电路及其写入操作中的行驱动方法,通过在字线上使用多级电压进行操作以及引入源极线信号对存储电容器的极板进行增强写入,解决了由于存取晶体管存在的阈值电压以及存取晶体管的栅源耦合电容导致的存储节点数据写入不完全,0/1数据电压差较小的问题。因此,根据本公开的动态随机存取存储器单元电路及其写入方法延长了数据存储时间,降低了由于刷新操作而中断的频率,从而降低了功耗。

5、然而,本公开的效果不限于上述效果,并且可以在不脱离本公开的精神和范围的情况下进行各种扩展应当理解,前面的一般描述和下面的详细描述都是示例性和解释性的,并且旨在提供对要求保护的本公开的进一步说明。

技术特征:

1.一种动态随机存取存储器阵列电路,包括2n行m列动态随机存取存储器单元电路,其中,m和n是大于零的自然数,

2.根据权利要求1所述的动态随机存取存储器阵列电路,

3.根据权利要求1或2所述的动态随机存取存储器阵列电路,

4.根据权利要求3所述的动态随机存取存储器阵列电路,

5.一种用在根据权利要求1至4中任一项所述的动态随机存取存储器阵列电路的写入操作中的行驱动方法,包括:

技术总结

本公开提供了动态随机存取存储器(DRAM)阵列电路及其写入操作中的行驱动方法。根据本公开的DRAM阵列电路包括2N行M列DRAM单元电路,M和N是大于零的自然数,其中,DRAM单元电路中的每一个包括:N型存取晶体管,其栅极连接到字线并且其第一源/漏极连接到位线;以及存储电容器,其第一极板连接到N型存取晶体管的第二源/漏极并且其第二极板连接到源极线,其中在写入操作中,字线在地电压、高于或等于电源电压的第一电压以及N型存取晶体管的阈值电压和第一电压之间的第二电压操作,以及其中在写入操作中,当字线在第二电压操作时,源极线在电源电压操作,其中在DRAM阵列电路中,第2n行和第2n+1行DRAM单元电路共用一个源极线,其中0≤n≤N‑1。

技术研发人员:潘立阳,谢翔,黄焘

受保护的技术使用者:北京超弦存储器研究院

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!