一种宽电压域SRAM读写时序控制电路及方法

本发明属于集成电路设计领域,更具体地,涉及一种宽电压域sram读写时序控制电路及方法。

背景技术:

1、静态随机存取存储器(sram)具有高读写速度,低功耗和较好的数据稳定性,被广泛应用于嵌入式设备中。图1为现有技术中一种典型的sram写脉冲控制电路,当时钟上升沿到来时,如果使能信号和读写选择信号同时为低电平,写脉冲控制电路将产生一个写脉冲信号,经过一定的延时后,时钟信号产生写复位脉冲信号,使写脉冲信号失效。上述写脉冲控制电路通过写脉冲信号来控制sram的写操作,包括写字线宽度控制和写驱动电路控制。

2、图2为现有技术中一种典型的sram复制列和读脉冲控制电路,复制列反映最坏情况下读操作的延时,即位线放电到“0”所需要的最长时间。当时钟上升沿到来时,如果使能信号为低电平,读写选择信号为高电平,读脉冲控制电路将产生一个读脉冲信号。复制列位线信号的放电时间可以控制产生灵敏放大器所需的最长读字线脉宽,使灵敏放大器能够可靠地工作,以保证数据被准确读出。上述读脉冲控制电路通过读脉冲信号来控制sram的读操作,包括读字线宽度控制和读驱动电路控制。

3、sram读写脉冲控制电路都是通过在路径上插入延时链的方法来控制读字线和写字线的脉冲宽度,从而为字线宽度提供足够的余量,增加电路抗pvt(工艺、电压、温度,process、temperature、voltage)偏差的能力。然而,上述控制电路插入的延时链长度往往是固定的,当电源电压发生变化时,尤其在在宽电压下,固定长度的延时链可能会造成脉冲宽度的余量过大或者脉冲宽度过窄的问题,从而限制sram的速度与读写操作正确性。

技术实现思路

1、针对相关技术的缺陷,本发明的目的在于提供一种宽电压域sram读写时序控制电路及方法,旨在解决当电源电压发生变化时,固定长度的延时链可能会造成脉冲宽度的余量过大或者脉冲宽度过窄的问题,从而限制sram的速度与读写操作正确性的问题。

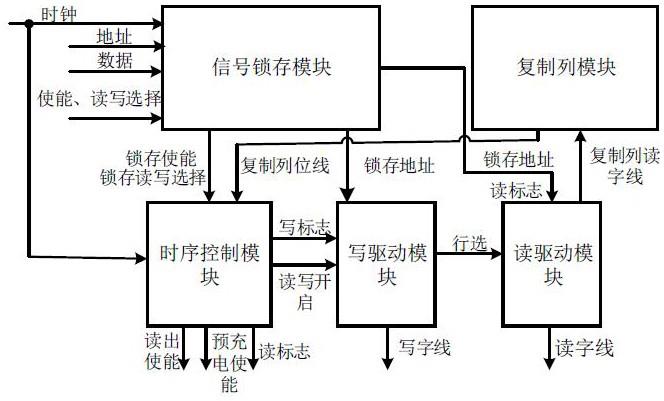

2、为实现上述目的,第一方面,本发明提供了一种宽电压域sram读写时序控制电路,包括信号锁存模块、时序控制模块、写驱动模块、读驱动模块和复制列模块:

3、所述信号锁存模块用于在时钟上升沿锁存地址信号、数据信号、使能信号和读写选择信号,并将锁存的地址信号输出给所述写驱动模块和所述读驱动模块,将锁存的使能信号和读写选择信号输出给所述时序控制模块;

4、所述时序控制模块用于根据锁存的使能信号和读写选择信号产生读写操作开启信号、读标志信号和写标志信号,以控制所述写驱动模块和读驱动模块开始对sram阵列的写操作和读操作;

5、所述写驱动模块用于根据所述读写操作开启信号和地址信号产生行选信号,输出至读驱动模块;同时,根据所述行选信号和写标志信号产生写字线信号,结合所述数据信号对阵列进行写操作;

6、所述读驱动模块用于根据所述读写操作开启信号和所述行选信号产生复制列的读字线信号;根据所述地址信号、行选信号和所述读标志信号产生存储阵列的读字线信号,以对阵列进行读操作;

7、所述复制列模块用于根据所述复制列的读字线信号进行一次复制列读操作,并将复制列位线信号反馈至时序控制模块,以指示复制列位线是否完成一次放电;

8、所述时序控制模块还用于在复制列位线完成一次放电时,产生复位信号、读出使能信号和预充电使能信号,并控制所述写驱动模块和读驱动模块停止对阵列的读操作和写操作。

9、可选的,当所述时序控制模块输出的写标志信号为高电平时,所述写驱动模块开启sram写操作。

10、可选的,当所述时序控制模块输出的读标志信号为高电平时,所述读驱动模块开启sram读操作。

11、可选的,所述复制列模块由一列存储固定值的sram单元组成,恒存对所述复制列进行读操作时,其所在位线需要放电的固定值。

12、可选的,阵列的读操作所需要的时间比阵列的写操作所需要的时间长。

13、可选的,复制列位线完成一次放电的时间为复制列一次读操作的时间,即sram的阵列进行一次读操作的最长时间。

14、第二方面,本发明还提供一种宽电压域sram读写时序控制方法,应用于如第一方面中任一项所述的宽电压域sram读写时序控制电路,包括:

15、当所述锁存的使能信号有效时,时序控制模块根据使能信号产生读写操作开启信号、读标志信号和写标志信号,输出至写驱动模块和读驱动模块;

16、当所述读写操作开启信号有效时,写驱动模块根据所述读写操作开启信号和所述地址信号,产生行选信号;读驱动模块根据所述地址信号和行选信号产生复制列的读字线信号;复制列模块在复制列的读字线信号有效时,开启复制列读操作,并将位线信号输出至所述时序控制模块;

17、若此时写标志信号有效,则写驱动模块根据所述行选信号产生写字线信号,并结合锁存的数据信号对阵列进行写操作;

18、若此时读标志信号有效,则读驱动模块根据所述行选信号产生存储阵列的读字线信号,对阵列进行读操作;

19、在复制列的位线放电完成时,时序控制模块产生复位信号和读出使能信号,根据所述读出使能信号从阵列中将数据读出,根据所述复位信号使所述读写操作开启信号失效从而结束对阵列的读操作和写操作;同时,时序控制模块产生预充电使能信号,对复制列的位线进行预充电。

20、可选的,在阵列进行读/写操作时,复制列模块根据所述读字线信号对复制列都进行一次读操作。

21、可选的,在所述时序控制模块根据使能信号产生读写操作开启信号、读标志信号和写标志信号之前,还包括:

22、在时钟上升沿,信号锁存模块锁存地址信号、数据信号、使能信号和读写选择信号,并将锁存的地址信号输出给写驱动模块和读驱动模块,将锁存的使能信号和读写选择信号输出给时序控制模块。

23、本发明实施例的技术方案,通过在sram阵列中增加一列复制列来模拟sram读操作所需要的最长时间,并根据复制列的读时间来控制字线的脉冲宽度,精确控制读操作和写操作的开启和结束时间,满足不同电压情况下读字线和写字线的脉冲宽度需求,解决了当电源电压发生变化时,固定长度的延时链可能会造成脉冲宽度的余量过大或者脉冲宽度过窄的技术问题,实现了提高sram读写稳定性,增加sram的工作电压范围的有益效果。

技术特征:

1.一种宽电压域sram读写时序控制电路,其特征在于,包括:信号锁存模块、时序控制模块、写驱动模块、读驱动模块和复制列模块;

2.如权利要求1所述的控制电路,其特征在于,当所述时序控制模块输出的写标志信号为高电平时,所述写驱动模块开启sram写操作。

3.如权利要求1所述的控制电路,其特征在于,当所述时序控制模块输出的读标志信号为高电平时,所述读驱动模块开启sram读操作。

4.如权利要求1所述的控制电路,其特征在于,所述复制列模块由一列存储固定值的sram单元组成,恒存对所述复制列进行读操作时,其所在位线需要放电的固定值。

5.如权利要求1所述的控制电路,其特征在于,阵列的读操作所需要的时间比阵列的写操作所需要的时间长。

6.如权利要求5所述的控制电路,其特征在于,复制列位线完成一次放电的时间为复制列一次读操作的时间,即sram的阵列进行一次读操作的最长时间。

7.一种宽电压域sram读写时序控制方法,应用于如权利要求1-6任一项所述的宽电压域sram读写时序控制电路,其特征在于,包括:

8.如权利要求7所述的宽电压域sram读写时序控制方法,其特征在于,在阵列进行读/写操作时,复制列模块根据所述读字线信号对复制列都进行一次读操作。

9.如权利要求7所述的宽电压域sram读写时序控制方法,其特征在于,在所述时序控制模块根据使能信号产生读写操作开启信号、读标志信号和写标志信号之前,还包括:

技术总结

本发明提供了一种宽电压域SRAM读写时序控制电路及方法。控制电路包括:信号锁存模块,在时钟上升沿锁存地址信号、数据信号、使能信号和读写选择信号;时序控制模块根据锁存的使能信号和读写选择信号产生读写操作开启信号和读写标志信号;根据位线放电时间产生复位信号、读出使能信号和预充电使能信号;写驱动模块根据读写操作开启信号、地址信号和写标志信号,产生行选信号和写字线信号;读驱动模块根据读写操作开启信号、行选信号、地址信号和读标志信号产生读字线信号;复制列模块根据复制列的读字线信号进行读操作,并将位线信号输出给时序控制模块。实现了精确控制读操作和写操作的开启和结束时间。

技术研发人员:刘政林,邓茜,于润泽,黎振豪,汪钊旭

受保护的技术使用者:华中科技大学

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!