存储器装置的制作方法

本发明是有关于一种存储器装置,且特别是有关于一种通过多芯片相互堆叠来形成的存储器装置。

背景技术:

1、在三维及式闪存中,多个存储器区块可共享一个感测放大器以节省电路布局的面积。然而,这样的作法,感测放大器的数量将影响到存储器的存取带宽。

2、在现有的设计中,小尺寸的存储单元区块的设计,可加速存储单元的存取速率。然而,通过使多个存储单元区块共享一个感测放大器的做法,会造成共享位线需要很长的长度,并产生过高的信号传输阻抗。这个过高的信号传输阻抗常为存储器的数据感测速度的瓶颈,并造成读取效率无法有效的被提升。

技术实现思路

1、本发明提供一种存储器装置,可有效降低感测放大器耦接至存储单元间的共同位线的传输阻抗。

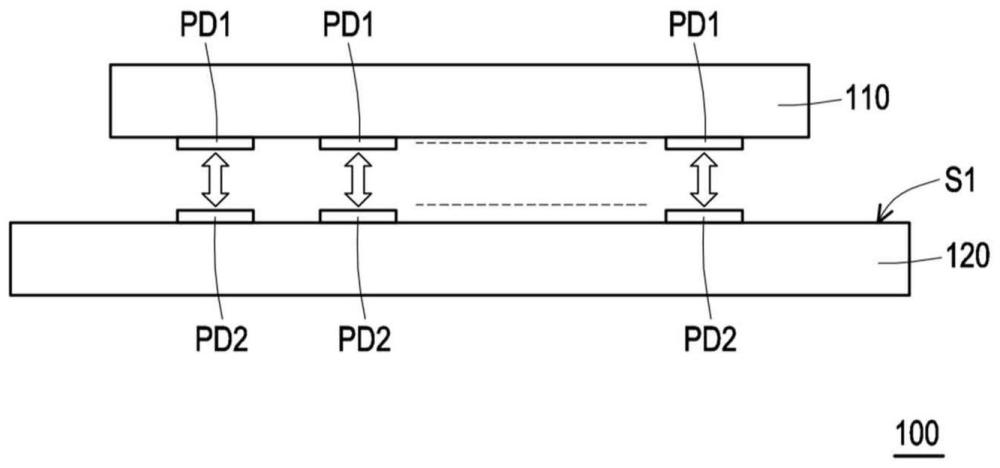

2、本发明的存储器装置包括第一芯片以及第二芯片。第一芯片具有多个源极线开关、多个位线开关、多个页缓冲器以及多个感测放大器。第一芯片并具有多个第一焊垫。第二芯片具有多个存储单元以形成多个存储单元区块。第二芯片的第一表面上具有多个第二焊垫以分别耦接至存储单元区块上的多条区域位线以及多条区域源极线。其中各第一焊垫与对应的各第二焊垫相互耦接。

3、基于上述,本发明的存储器装置通过不同的二芯片相互组合而成。其中,源极线开关、位线开关、页缓冲器以及感测放大器被设置在第一芯片中,存储单元区块被设置在第二芯片中。通过使第一芯片上的多个第一焊垫与第二芯片上的多个第二焊垫相互耦接,可完成存储器装置完整的电路回路。并且,感测放大器可通过第一焊垫、第二焊垫以分别与对应的存储单元区块的共同位线电性连接,降低共同位线的长度以及传输阻抗,提升存储器装置的工作效益。

技术特征:

1.一种存储器装置,包括:

2.根据权利要求1所述的存储器装置,其中该第二芯片上具有分别对应这些存储单元区块的多个x地址译码器。

3.根据权利要求1所述的存储器装置,其中这些源极线开关区分为多个源极线开关组,这些位线开关区分为多个位线开关组,各该源极线开关组与各该位线开关组对应各该存储单元区块。

4.根据权利要求3所述的存储器装置,其中各该存储单元区块分别对应的各该x地址译码器。

5.根据权利要求4所述的存储器装置,其中各该存储单元区块与对应的各该源极线开关组、各该位线开关组、各该感测放大器以及各该x地址译码器相互堆叠。

6.根据权利要求3所述的存储器装置,其中各该感测放大器耦接至对应的各该页缓冲器以及对应的各该位线开关组。

7.根据权利要求1所述的存储器装置,其中这些区域位线以及这些区域源极线具有相同的尺寸,相邻的各该区域位线与各该区域源极线间具有实质上相同的寄生电容值。

8.根据权利要求1所述的存储器装置,其中各该区域位线以及各该区域源极线交错平行设置在对应的各该存储单元区块的上方。

9.根据权利要求7所述的存储器装置,其中这些第二焊垫分别形成在这些区域位线以及这些区域源极线上方,并通过多个导电通孔与这些区域位线以及这些区域源极线电性耦接。

10.根据权利要求1所述的存储器装置,还包括:

11.根据权利要求10所述的存储器装置,其中这些直通硅晶穿孔穿透该第二芯片的一无电路区域。

12.根据权利要求10所述的存储器装置,其中该第二芯片的接地多晶硅层上形成多个分隔岛,这些直通硅晶穿孔分别穿透这些分隔岛。

13.根据权利要求10所述的存储器装置,其中该第二芯片的第二表面上具有多个导电凸块,这些导电凸块分别耦接至这些直通硅晶穿孔。

14.根据权利要求10所述的存储器装置,其中该周边电路设置在第一芯片的中心位置,该周边电路并区隔该第一芯片为多个区域,各该源极线开关与对应的各该位线开关、各该页缓冲器以及各该感测放大器设置在这些区域的其中之一。

技术总结

本公开提供了一种存储器装置,例如为三维与式或或非式闪存,该存储器装置包括第一芯片以及第二芯片。第一芯片具有多个源极线开关、多个位线开关、多个页缓冲器以及多个感测放大器。第一芯片并具有多个第一焊垫。第二芯片具有多个存储单元以形成多个存储单元区块。第二芯片的第一表面上具有多个第二焊垫以分别耦接至存储单元区块上的多条区域位线以及多条区域源极线。其中各第一焊垫与对应的各第二焊垫相互耦接。

技术研发人员:叶腾豪,吕函庭,胡志玮

受保护的技术使用者:旺宏电子股份有限公司

技术研发日:

技术公布日:2024/11/14

- 还没有人留言评论。精彩留言会获得点赞!