多PSRAM颗粒芯片的数据处理方法、电子设备及存储介质与流程

本申请涉及数据处理,特别涉及一种多psram颗粒芯片的数据处理方法、电子设备及存储介质。

背景技术:

1、在某些低带宽需求的芯片系统方案中,考虑不使用ddr(double data rate,双倍速率)sram(static random access memory,静态随机存取存储器)颗粒作为系统的外部存储单元,而是选择更经济的psram(pseudo static random access memory,伪静态随机存储器)颗粒代替,从而降低芯片成本而提升芯片的竞争力。但是,目前单颗psram颗粒能提供的总带宽有限,与ddr sram颗粒带宽相差几十倍,因此在某些方案中存在使用多颗psram颗粒来提供更大的带宽的需求。

2、目前已了解的大部分psram颗粒芯片控制的方案中,基本都是使用一个psram控制器对应一个psram颗粒。这样的方案在实现多psram颗粒控制时,需要更多芯片逻辑资源,且无法对总线请求做更多处理来实现带宽提升等。

技术实现思路

1、本申请旨在至少解决现有技术中存在的技术问题之一。为此,本申请提出一种多psram颗粒芯片的数据处理方法、电子设备及存储介质,能够实现对多个psram颗粒进行控制,减少芯片逻辑资源的占用。

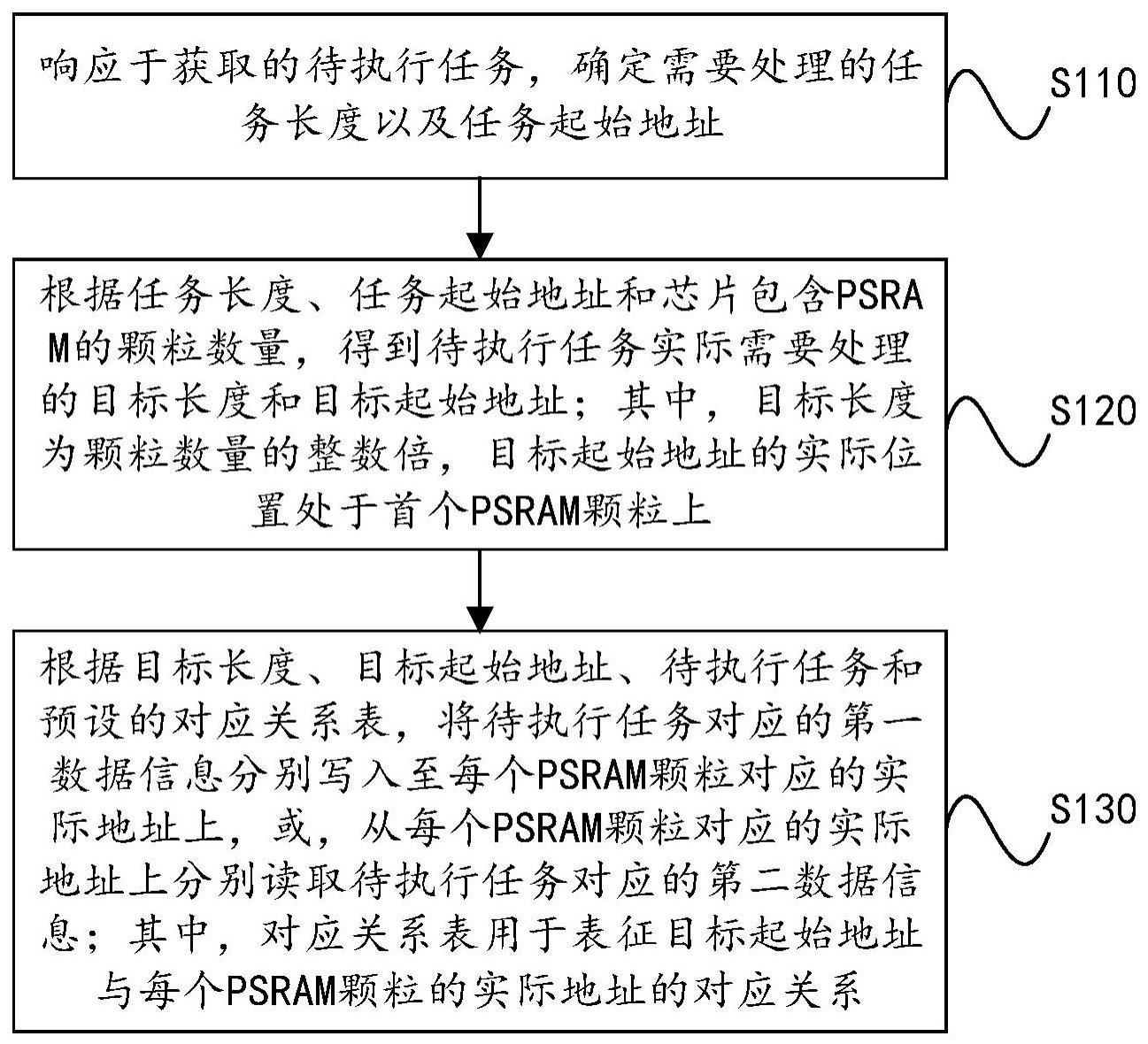

2、第一方面,本申请提供了一种多psram颗粒芯片的数据处理方法,包括:

3、响应于获取的待执行任务,确定需要处理的任务长度以及任务起始地址;

4、根据所述任务长度、所述任务起始地址和芯片包含psram的颗粒数量,得到所述待执行任务实际需要处理的目标长度和目标起始地址;其中,所述目标长度为所述颗粒数量的整数倍,所述目标起始地址的实际位置处于首个psram颗粒上;

5、根据所述目标长度、所述目标起始地址、所述待执行任务和预设的对应关系表,将所述待执行任务对应的第一数据信息分别写入至每个所述psram颗粒对应的实际地址上,或,从每个所述psram颗粒对应的实际地址上分别读取所述待执行任务对应的第二数据信息;其中,所述对应关系表用于表征所述目标起始地址与每个所述psram颗粒的实际地址的对应关系。

6、根据本申请第一方面实施例的多psram颗粒芯片的数据处理方法,至少具有如下有益效果:响应于获取的待执行任务,并确定该待执行任务所需要写入或者所需要读取的任务长度以及任务起始地址,根据任务长度、任务起始地址和芯片中包含psram的颗粒数量,得到待执行任务实际需要写入或者需要读取的目标长度和目标起始地址;根据目标长度、目标起始地址、待执行任务和预设的对应关系表,将待执行任务对应的第一数据信息分别写入至每个psram颗粒对应的实际地址上,或,从每个psram颗粒对应的实际地址上分别读取待执行任务对应的第二数据信息;目标起始地址的实际位置处于首个psram颗粒上,且目标长度为颗粒数量的整数倍,使得在完成一次待执行任务后,每个psram颗粒实际被处理的数据长度以及数据实际地址范围都是相同的,即将每个psram颗粒的数据进行对齐处理,方便数据的管理,使得每个psram颗粒控制逻辑一致,从而到达同一部分逻辑资源控制多个psram颗粒的目的,同时,本申请提供的psram颗粒芯片的数据处理方法能够实现在同一个控制器中多个psram颗粒的控制,减少芯片逻辑资源的占用。

7、根据本申请第一方面的一些实施例,所述根据所述任务长度、所述任务起始地址和芯片包含psram的颗粒数量,得到所述待执行任务实际需要处理的目标长度和目标起始地址,包括:获取所述任务起始地址除以所述颗粒数量得到的第二余数;将所述任务起始地址与所述第二余数的差作为所述目标起始地址;根据所述第二余数、所述任务长度和所述颗粒数量,得到所述待执行任务实际需要处理的目标长度。

8、根据本申请第一方面的一些实施例,所述根据所述第二余数、所述任务长度和所述颗粒数量,得到所述待执行任务实际需要处理的目标长度,包括:获取所述第二余数与所述任务长度之和除以所述颗粒数量得到的第三余数;将所述任务长度、所述第二余数和所述第三余数三者之和作为所述目标长度。

9、根据本申请第一方面的一些实施例,当所述待执行任务为数据写入任务;所述将所述待执行任务对应的第一数据信息分别写入至每个所述psram颗粒对应的实际地址上,包括:根据所述第二余数和所述第三余数,在所述第一数据信息首端加入所述第二余数字节的屏蔽位,以及在所述第一数据信息末端加入所述第三余数字节的屏蔽位,形成目标写入数据信息;根据所述目标起始地址和所述对应关系表,确定首个psram颗粒的实际地址;根据所述实际地址、所述目标长度和所述对应关系表,将所述目标写入数据分别写入至每个所述psram颗粒内。

10、根据本申请第一方面的一些实施例,当所述待执行任务为数据读取任务;所述从每个所述psram颗粒对应的实际地址上分别读取所述待执行任务对应的第二数据信息,包括:根据所述目标起始地址和所述对应关系表,确定首个psram颗粒的实际地址;根据所述实际地址、所述目标长度和所述对应关系表,从每个所述psram颗粒内分别读取目标读取数据;根据所述第二余数和所述第三余数,在所述目标读取数据的首端删除所述第二余数字节的数据,以及在所述目标读取数据的末端删除所述第三余数字节的数据,形成第二数据信息。

11、根据本申请第一方面的一些实施例,所述对应关系表中所述目标起始地址与每个所述psram颗粒的实际地址的对应关系具体为:所述目标起始地址除以所述颗粒数量得到的第一余数表示为所述psram颗粒的编号;其中,所述颗粒数量为n,所述psram颗粒的编号分别为0,1,...,n-1;所述目标起始地址除以所述颗粒数量得到的商值表示为对应的所述psram颗粒的实际地址。

12、根据本申请第一方面的一些实施例,还包括:连续获取两个待执行任务;当第一个所述待执行任务对应的任务末尾地址连接于第二个所述待执行任务对应的任务起始地址,在同一进程内将两个所述待执行任务对应的第一数据信息分别写入至每个所述psram颗粒对应的实际地址上,或,从每个所述psram颗粒对应的实际地址上分别读取两个所述待执行任务对应的第二数据信息。

13、根据本申请第一方面的一些实施例,还包括:响应于任务结束信号,将工作状态改变为空闲状态。

14、第二方面,本申请还提供了一种电子设备,包括:至少一个存储器;至少一个处理器;至少一个程序;所述程序被存储在所述存储器中,所述处理器执行至少一个所述程序以实现如第一方面任一项实施例所述的多psram颗粒芯片的数据处理方法。

15、第三方面,本申请还提供了一种计算机可读存储介质,所述计算机可读存储介质存储有计算机可执行信号,所述计算机可执行信号用于执行如第一方面任一项实施例所述的多psram颗粒芯片的数据处理方法。

16、本申请的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本申请的实践了解到。

技术特征:

1.一种多psram颗粒芯片的数据处理方法,其特征在于,包括:

2.根据权利要求1任意一项所述的多psram颗粒芯片的数据处理方法,其特征在于,所述对应关系表中所述目标起始地址与每个所述psram颗粒的实际地址的对应关系具体为:

3.根据权利要求2所述的多psram颗粒芯片的数据处理方法,其特征在于,所述根据所述任务长度、所述任务起始地址和芯片包含psram的颗粒数量,得到所述待执行任务实际需要处理的目标长度和目标起始地址,包括:

4.根据权利要求3所述的多psram颗粒芯片的数据处理方法,其特征在于,所述根据所述第二余数、所述任务长度和所述颗粒数量,得到所述待执行任务实际需要处理的目标长度,包括:

5.根据权利要求4所述的多psram颗粒芯片的数据处理方法,其特征在于,当所述待执行任务为数据写入任务;所述将所述待执行任务对应的第一数据信息分别写入至每个所述psram颗粒对应的实际地址上,包括:

6.根据权利要求4所述的多psram颗粒芯片的数据处理方法,其特征在于,当所述待执行任务为数据读取任务;所述从每个所述psram颗粒对应的实际地址上分别读取所述待执行任务对应的第二数据信息,包括:

7.根据权利要求1所述多psram颗粒芯片的数据处理方法,其特征在于,还包括:

8.根据权利要求1所述的多psram颗粒芯片的数据处理方法,其特征在于,还包括:

9.一种电子设备,其特征在于,包括:

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质存储有计算机可执行信号,所述计算机可执行信号用于执行如权利要求1至8任一项所述的多psram颗粒芯片的数据处理方法。

技术总结

本申请公开了一种多PSRAM颗粒芯片的数据处理方法、电子设备及存储介质,该处理方法包括:响应于获取的待执行任务,确定需要处理的任务长度以及任务起始地址;根据任务长度、任务起始地址和芯片包含PSRAM的颗粒数量,得到待执行任务实际需要处理的目标长度和目标起始地址;其中,目标长度为颗粒数量的整数倍,目标起始地址的实际位置处于首个PSRAM颗粒上;根据目标长度、目标起始地址、待执行任务和预设的对应关系表,将待执行任务对应的第一数据信息分别写入至每个PSRAM颗粒对应的实际地址上,或,从每个PSRAM颗粒对应的实际地址上分别读取待执行任务对应的第二数据信息。本申请能够实现对多个PSRAM颗粒进行控制,减少芯片逻辑资源的占用。

技术研发人员:何建文,原顺

受保护的技术使用者:广东匠芯创科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!