内存设备命令总线训练中的延时确定方法和装置与流程

本申请涉及存储器,尤其涉及一种内存设备命令总线训练中的延时确定方法和装置。

背景技术:

1、ddr (double data rate synchronous dynamic random access memory,双倍速率同步动态随机存储器)上电后,需要进行命令总线训练以校准ca(command/address,命令/地址)信号、cs(chip select,芯片选择)信号和时钟信号ck之间的延时,从而使芯片在高频时可以正确地发送命令。由于ddr上电后ca总线和cs线的延时是未知的,因此需要合理的命令总线训练方案来计算延时。

2、然而现有的命令总线训练中,往往直接进行延时推动,如果实际延时较小可以训练成功,但如果实际延时过大(例如ca偏离过大)会导致训练失败或训练时间过长,无法保证命令总线训练的效率和准确性。

技术实现思路

1、本申请提供一种内存设备命令总线训练中的延时确定方法和装置,以用于解决现有的命令总线训练方式无法保证命令总线训练的效率和准确性的问题。

2、本申请提供一种内存设备命令总线训练中的延时确定方法,所述方法包括:

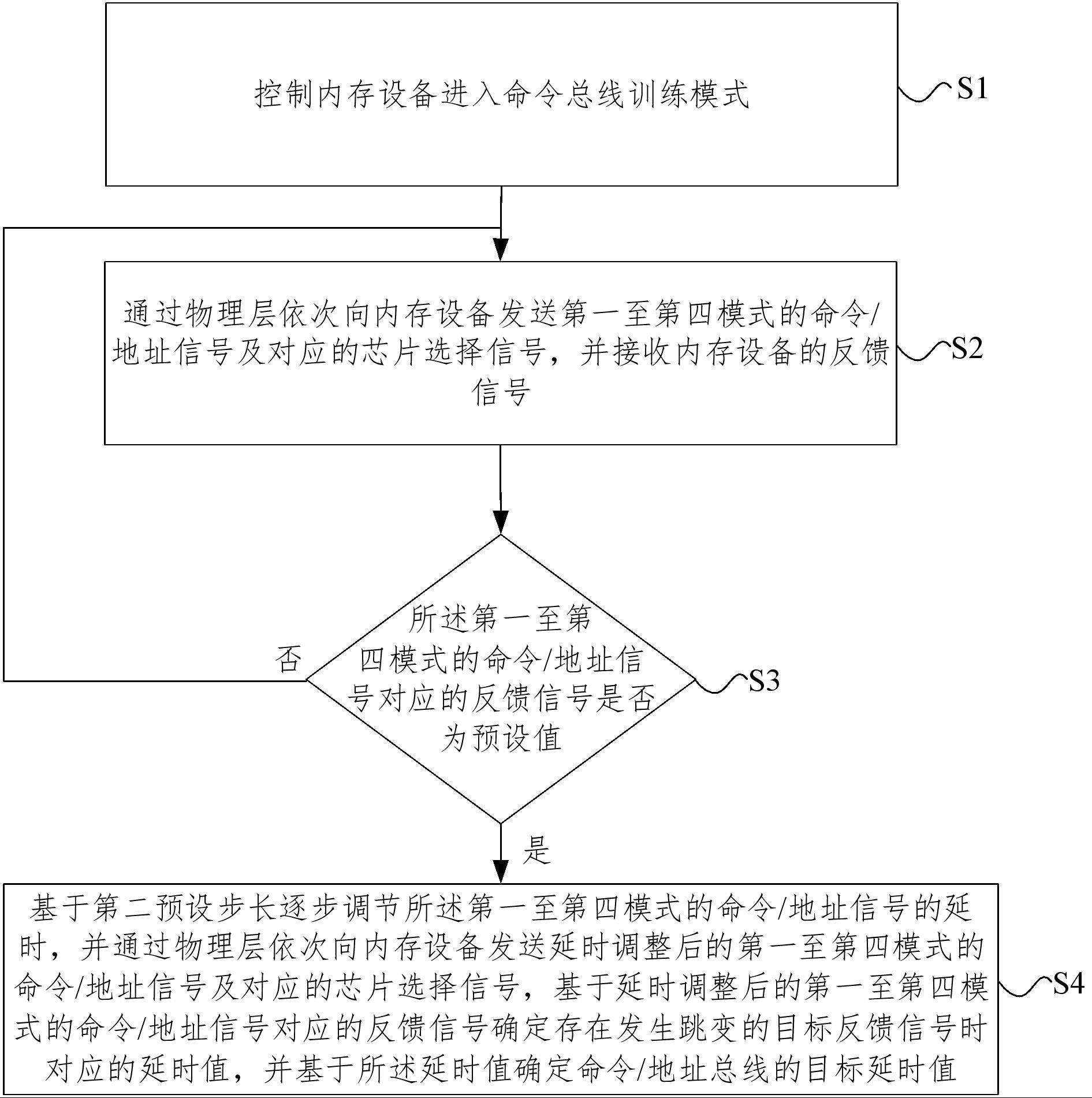

3、步骤s1,控制内存设备进入命令总线训练模式;

4、步骤s2,通过物理层依次向内存设备发送第一至第四模式的命令/地址信号及对应的芯片选择信号,并接收内存设备的反馈信号;

5、步骤s3,判断所述第一至第四模式的命令/地址信号对应的反馈信号是否为预设值,若否,基于第一预设步长调节所述第一至第四模式的命令/地址信号的延时,并跳转执行步骤s2;若是,执行步骤s4;

6、步骤s4,基于第二预设步长逐步调节所述第一至第四模式的命令/地址信号的延时,并通过物理层依次向内存设备发送延时调整后的第一至第四模式的命令/地址信号及对应的芯片选择信号,基于延时调整后的第一至第四模式的命令/地址信号对应的反馈信号确定存在发生跳变的目标反馈信号时对应的延时值,并基于所述延时值确定命令/地址总线的目标延时值。

7、根据本申请提供的一种内存设备命令总线训练中的延时确定方法,任一模式的命令/地址信号均对应于四个连续的信号区段,对应的芯片选择信号的高电平区间与所述四个连续的信号区段中的第三信号区段匹配,同时,所述芯片选择信号的高电平区间与时钟信号的目标周期匹配。

8、根据本申请提供的一种内存设备命令总线训练中的延时确定方法,所述基于第一预设步长调节所述第一至第四模式的命令/地址信号的延时,具体包括:

9、基于所述第一至第四模式的命令/地址信号对应的反馈信号的值确定命令/地址信号的偏移方向及偏移范围;

10、基于所述命令/地址信号的偏移方向及偏移范围确定所述命令/地址信号的延时修正方向及延时修正范围;

11、基于所述命令/地址信号的延时修正方向及延时修正范围,按照第一预设步长调节所述第一至第四模式的命令/地址信号的延时。

12、根据本申请提供的一种内存设备命令总线训练中的延时确定方法,所述基于所述延时值确定命令/地址总线的目标延时值,具体包括:

13、基于所述延时值确定对应的第一延时位置和第二延时位置;

14、基于所述第一延时位置和第二延时位置的中间位置,确定命令/地址总线的目标延时值。

15、根据本申请提供的一种内存设备命令总线训练中的延时确定方法,所述方法还包括:将所述目标延时值写入用于延时控制的目标寄存器中。

16、根据本申请提供的一种内存设备命令总线训练中的延时确定方法,所述控制内存设备进入命令总线训练模式,具体包括:对模式寄存器中的命令总线训练控制位进行置位操作。

17、根据本申请提供的一种内存设备命令总线训练中的延时确定方法,所述第一预设步长对应于半个时钟周期,所述第一预设步长为所述第二预设步长的n倍;其中,n为正整数。

18、根据本申请提供的一种内存设备命令总线训练中的延时确定方法,所述预设值为对应模式的命令/地址信号中的第三信号区段的值。

19、本申请还提供一种非暂态计算机可读存储介质,其上存储有计算机程序,该计算机程序被处理器执行时实现如上述任一种所述内存设备命令总线训练中的延时确定方法的步骤。

20、本申请还提供一种计算机程序产品,包括计算机程序,所述计算机程序被处理器执行时实现如上述任一种所述内存设备命令总线训练中的延时确定方法的步骤。

21、本申请提供的内存设备命令总线训练中的延时确定方法和装置,通过步骤s1,控制内存设备进入命令总线训练模式;步骤s2,通过物理层依次向内存设备发送第一至第四模式的命令/地址信号及对应的芯片选择信号,并接收内存设备的反馈信号;步骤s3,判断所述第一至第四模式的命令/地址信号对应的反馈信号是否为预设值,若否,基于第一预设步长调节所述第一至第四模式的命令/地址信号的延时,并跳转执行步骤s2;若是,执行步骤s4;步骤s4,基于第二预设步长逐步调节所述第一至第四模式的命令/地址信号的延时,并通过物理层依次向内存设备发送延时调整后的第一至第四模式的命令/地址信号及对应的芯片选择信号,基于延时调整后的第一至第四模式的命令/地址信号对应的反馈信号确定存在发生跳变的目标反馈信号时对应的延时值,并基于所述延时值确定命令/地址总线的目标延时值,能够保证命令总线训练的效率和准确性。

技术特征:

1.一种内存设备命令总线训练中的延时确定方法,其特征在于,所述方法包括:

2.根据权利要求1所述的内存设备命令总线训练中的延时确定方法,其特征在于,任一模式的命令/地址信号均对应于四个连续的信号区段,对应的芯片选择信号的高电平区间与所述四个连续的信号区段中的第三信号区段匹配,同时,所述芯片选择信号的高电平区间与时钟信号的目标周期匹配。

3.根据权利要求2所述的内存设备命令总线训练中的延时确定方法,其特征在于,所述基于第一预设步长调节所述第一至第四模式的命令/地址信号的延时,具体包括:

4.根据权利要求3所述的内存设备命令总线训练中的延时确定方法,其特征在于,所述基于所述延时值确定命令/地址总线的目标延时值,具体包括:

5.根据权利要求4所述的内存设备命令总线训练中的延时确定方法,其特征在于,所述方法还包括:将所述目标延时值写入用于延时控制的目标寄存器中。

6.根据权利要求5所述的内存设备命令总线训练中的延时确定方法,其特征在于,所述控制内存设备进入命令总线训练模式,具体包括:对模式寄存器中的命令总线训练控制位进行置位操作。

7.根据权利要求6所述的内存设备命令总线训练中的延时确定方法,其特征在于,所述第一预设步长对应于半个时钟周期,所述第一预设步长为所述第二预设步长的n倍;其中,n为正整数。

8.根据权利要求7所述的内存设备命令总线训练中的延时确定方法,其特征在于,所述预设值为对应模式的命令/地址信号中的第三信号区段的值。

9.一种电子设备,包括存储器、处理器及存储在所述存储器上并可在所述处理器上运行的计算机程序,其特征在于,所述处理器执行所述程序时实现如权利要求1至8任一项所述内存设备命令总线训练中的延时确定方法的步骤。

10.一种非暂态计算机可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现如权利要求1至8任一项所述内存设备命令总线训练中的延时确定方法的步骤。

技术总结

本申请提供一种内存设备命令总线训练中的延时确定方法和装置,属于存储器技术领域,所述方法包括:S1,控制内存设备进入命令总线训练模式;S2,依次向内存设备发送第一至第四模式的命令/地址信号及对应的芯片选择信号并接收内存设备的反馈信号;S3,判断反馈信号是否为预设值,若否,基于第一预设步长调节第一至第四模式的命令/地址信号的延时,并执行S2;若是,执行S4;S4,基于第二预设步长逐步调节第一至第四模式的命令/地址信号的延时并依次发送给内存设备,基于反馈信号确定存在发生跳变的目标反馈信号时对应的延时值,并基于延时值确定命令/地址总线的目标延时值,能够保证命令总线训练的效率和准确性。

技术研发人员:田亚男,钱阔,王晓阳

受保护的技术使用者:上海奎芯集成电路设计有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!